ICS601-01

LOW PHASE NOISE CLOCK MULTIPLIER CLOCK MULTIPLIER

IDT™ / ICS™

LOW PHASE NOISE CLOCK MULTIPLIER 3

ICS601-01 REV N 051310

Achieving Low Phase Noise

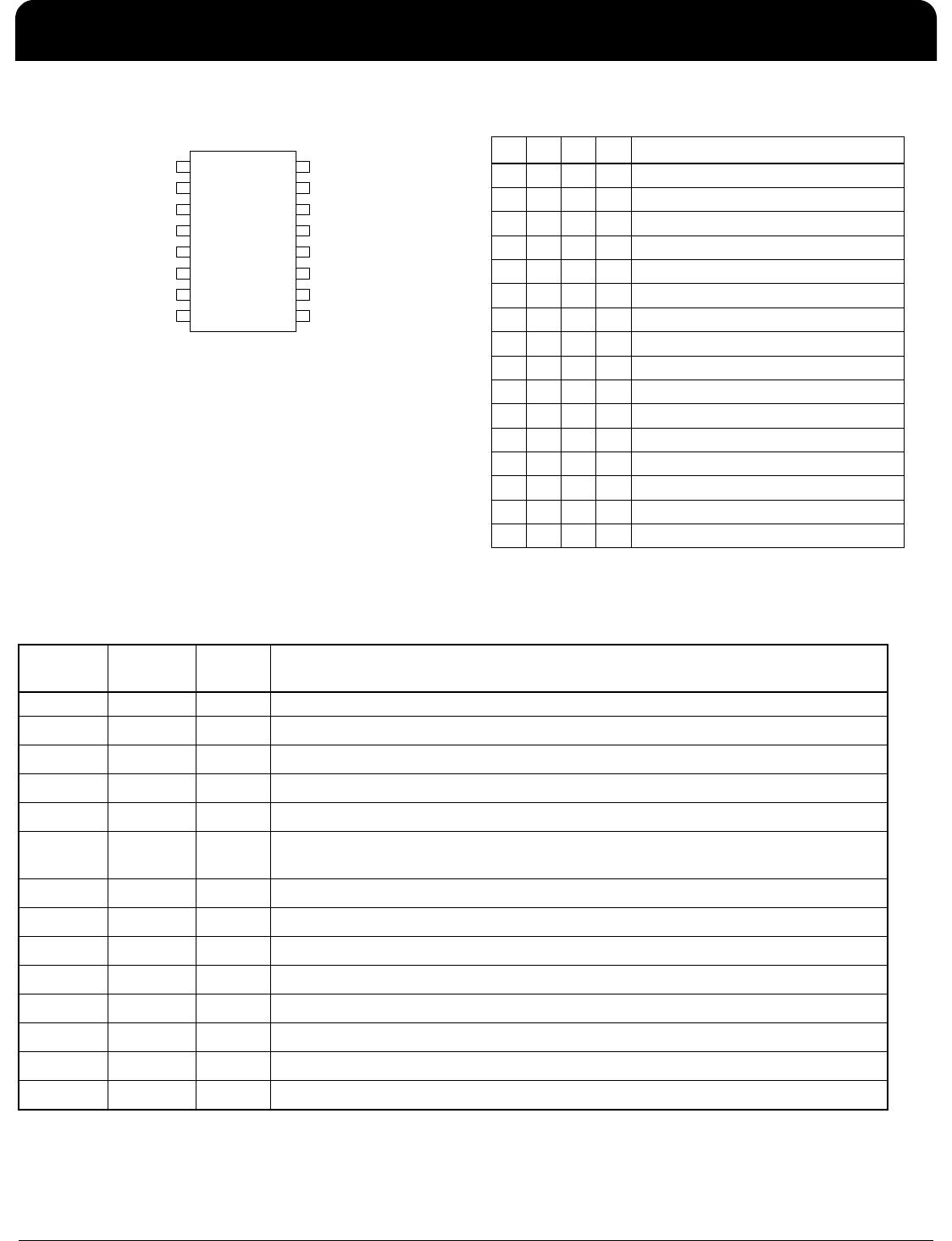

Figure 1 shows a typical phase noise measurement in a 125 MHz system. Therea are a few simple steps that can

be taken to achieve these levels of phase noise from the ICS601-01. Variations in VDD will increase the hase noise,

so it is important to have a stable, low noise supply voltage at the device. Use decoupling capacitors of 0.1µF in

parallel with 0.01µF. It is important to have these capacitors as close as possible to the ICS601-01 supply pins.

Disabling the REFOUT clock is also important for achieving low phase noise; lab tests have shown that this can

reduce the phase noise by as much as 10 dBc/Hz.

External Component/Crystal Selection

The ICS601-01 requires a minimum number of external components for proper operation. Decoupling capacitors of

0.01µF and 0.1µF should be connected between VDD and GND, as close to the part as possible. A series

termination resistor of 33Ω may be used for each clock output. The crystal must be connected as close to the chip

as possible. The crystal should be fundamental mode, parallel resonant. Do not use third overtone. For exact tuning

when using a crystal, capacitors should beconnected from pins X1 to ground and X2 to ground. In general, the

value of these capacitors is given by the following equation, where CL is the crystal load capacitance: Crystal caps

(pF) = (CL - 5) x 2. So for a crystal with 16 pF load capacitance, two 22 pF caps can be used. For any given board

layout, ICS can measure the board capacitance and recommend the exact capacitance value to use.

Figure 1. Phase Noise of ICS601-01 for 125 MHz output, 25 MHz crystal input.

VDD = 3.3 V, REFOUT disabled.

-140

-120

-100

-80

-60

-40

-20

0

1. 00E+01 1. 00E+02 1. 00E+03 1. 00E+04 1.00E+05 1. 00E+06 1. 00E+07

Offset from Carrier (Hz)

Phase Noise

dBc/Hz