CAT25640

www.onsemi.com

12

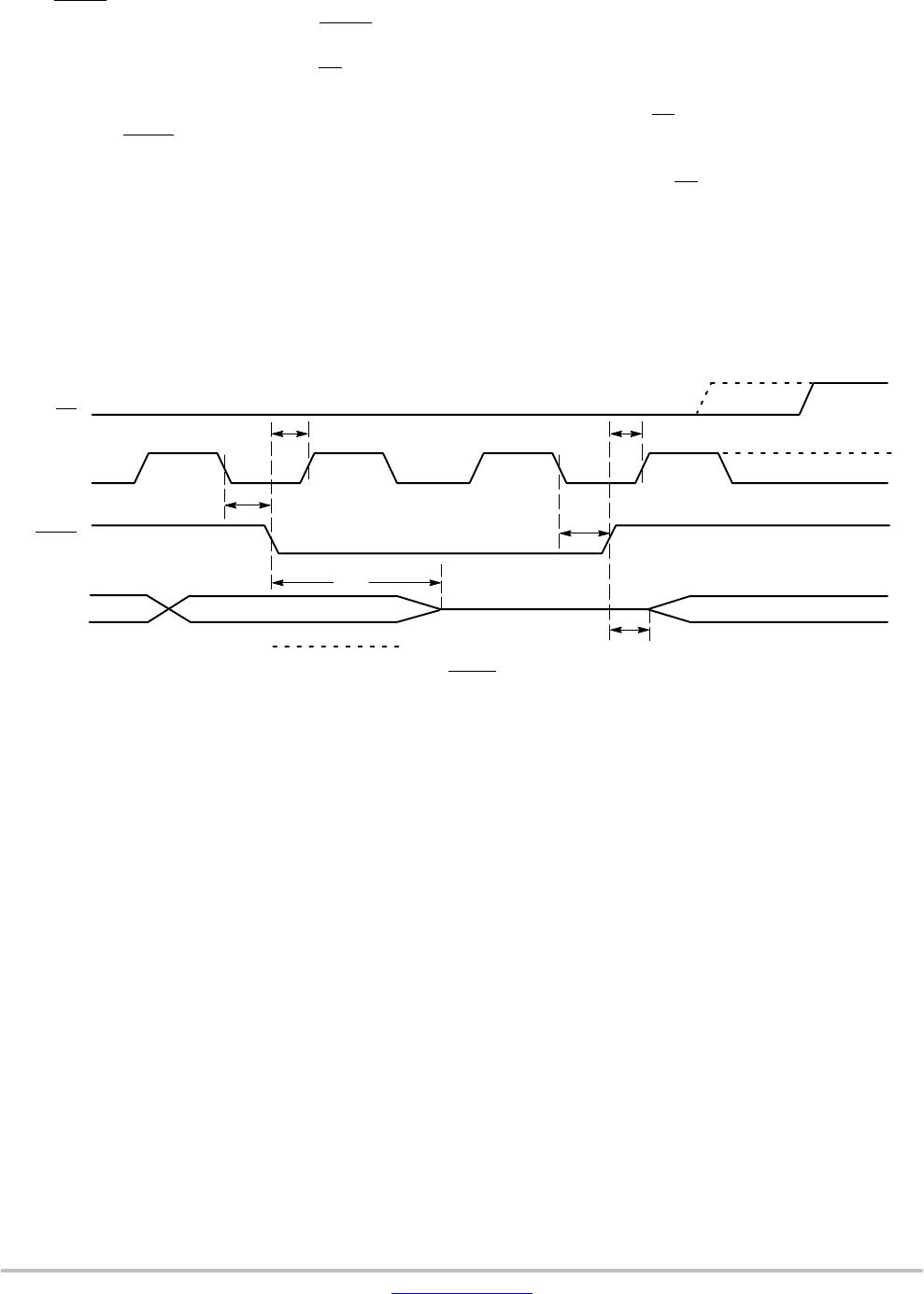

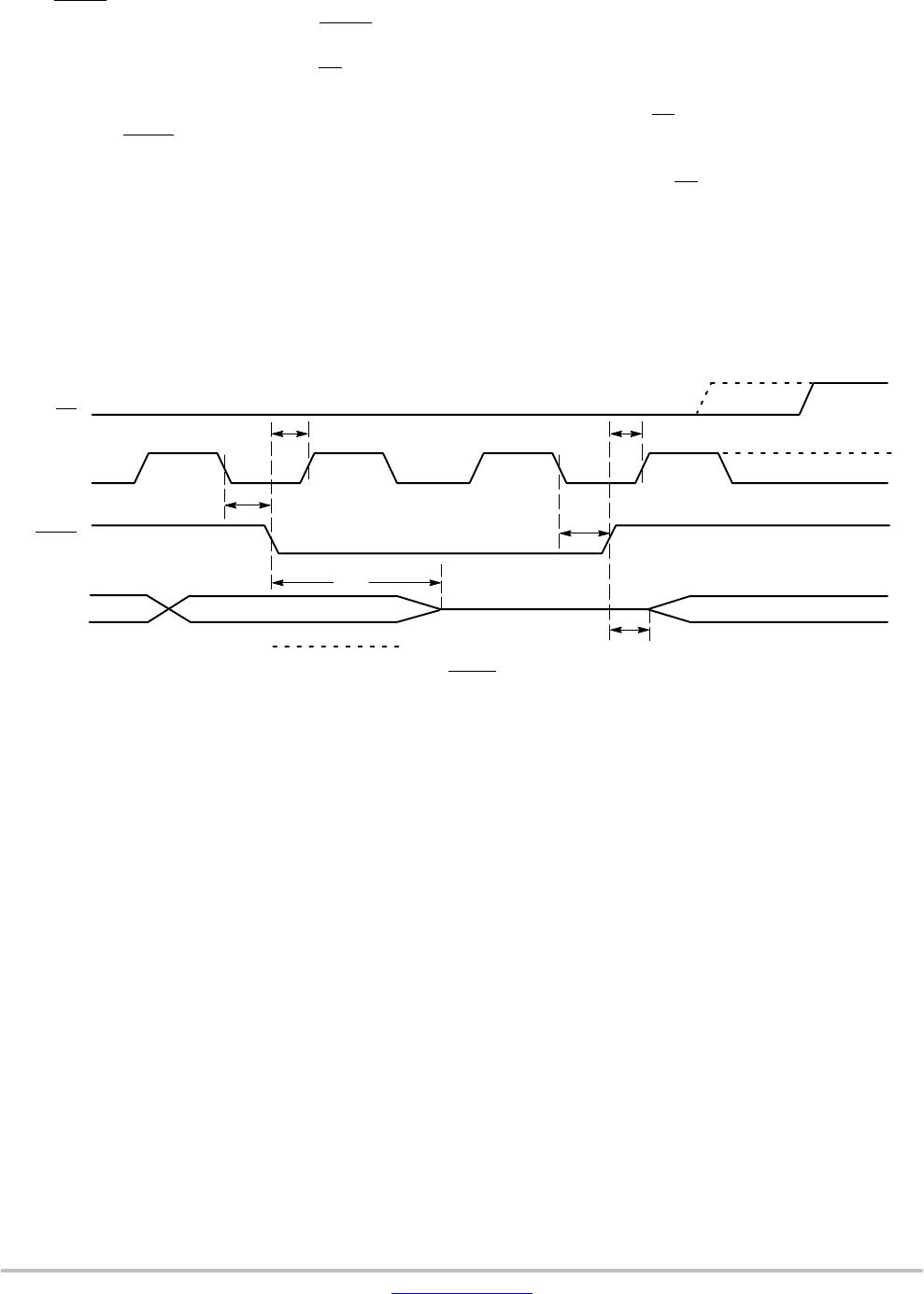

Hold Operation

The HOLD input can be used to pause communication

between host and CAT25640. To pause, HOLD

must be

taken low while SCK is low (Figure 11). During the hold

condition the device must remain selected (CS

low). During

the pause, the data output pin (SO) is tri−stated (high

impedance) and SI transitions are ignored. To resume

communication, HOLD

must be taken high while SCK is low.

Design Considerations

The CAT25640 device incorporates Power−On Reset

(POR) circuitry which protects the internal logic against

powering up in the wrong state. The device will power up

into Standby mode after V

CC

exceeds the POR trigger level

and will power down into Reset mode when V

CC

drops

below the POR trigger level. This bi−directional POR

behavior protects the device against ‘brown−out’ failure

following a temporary loss of power.

The CAT25640 device powers up in a write disable state

and in a low power standby mode. A WREN instruction

must be issued prior to any writes to the device.

After power up, the CS

pin must be brought low to enter

a ready state and receive an instruction. After a successful

byte/page write or status register write, the device goes into

a write disable mode. The CS

input must be set high after the

proper number of clock cycles to start the internal write

cycle. Access to the memory array during an internal write

cycle is ignored and programming is continued. Any invalid

op−code will be ignored and the serial output pin (SO) will

remain in the high impedance state.

Figure 11. HOLD Timing

SCK

SO

HIGH IMPEDANCE

Dashed Line = mode (1, 1)

t

LZ

CS

HOLD

t

CD

t

HD

t

HD

t

CD

t

HZ