DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as “IDT”) reserve the right to modify the products and/or specifications described herein at any time, without

notice, at IDT’s sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed

in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any

particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intel-

lectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably

expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of

IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. Integrated Device Technology, Inc.. All rights reserved.

Tech Support

www.idt.com/go/support

Sales

1-800-345-7015 or 408-284-8200

Fax: 408-284-2775

www.IDT.com/go/sales

Corporate Headquarters

6024 Silver Creek Valley Road

San Jose, CA 95138 USA

www.IDT.com

8S89831I Datasheet

18©2017 Integrated Device Technology, Inc. November 9, 2017

Package Outline Drawings

The package outline drawings are located at the end of this document. The package information is the most current data available and is subject

to change without notice or revision of this document.

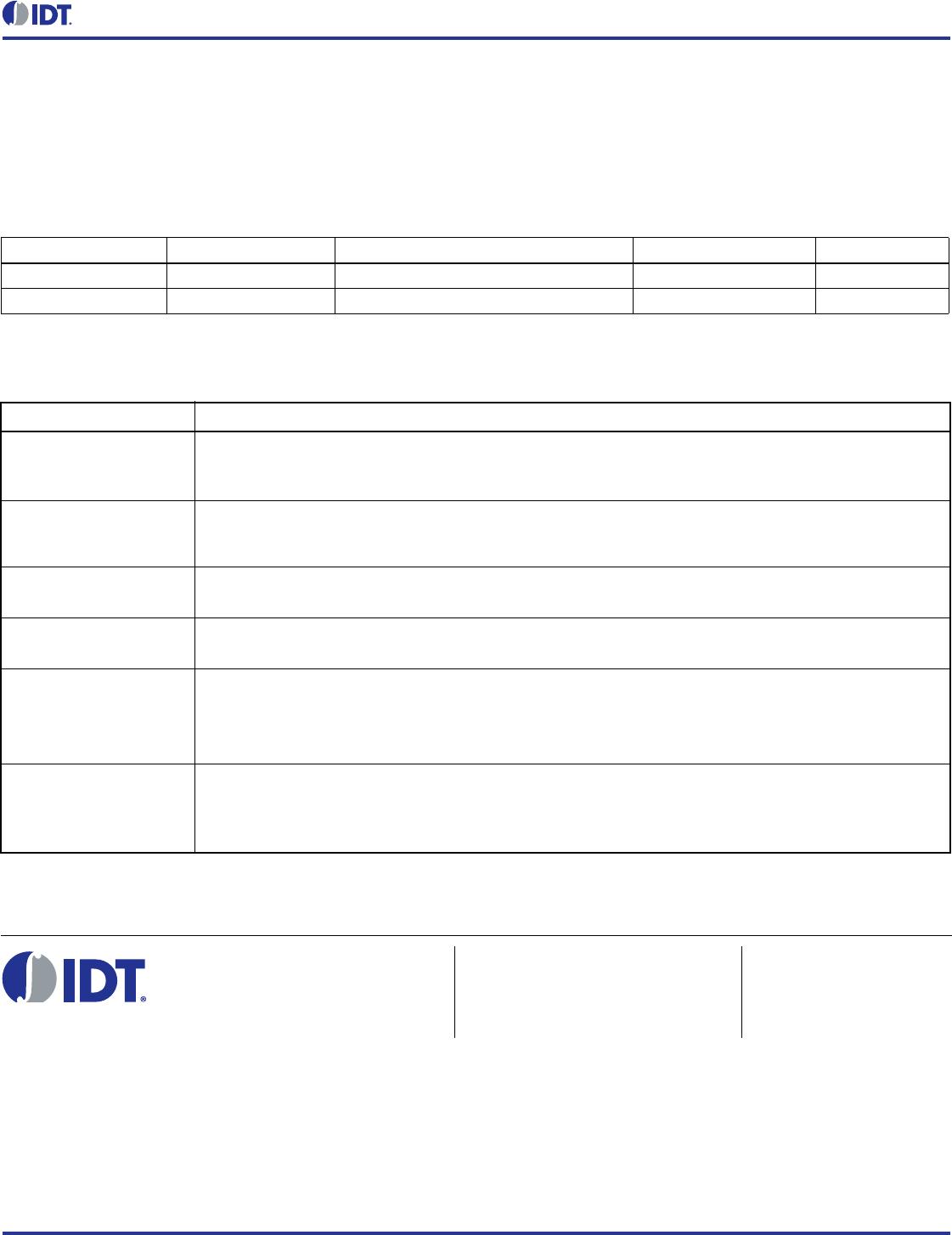

Ordering Information

Table 9. Ordering Information

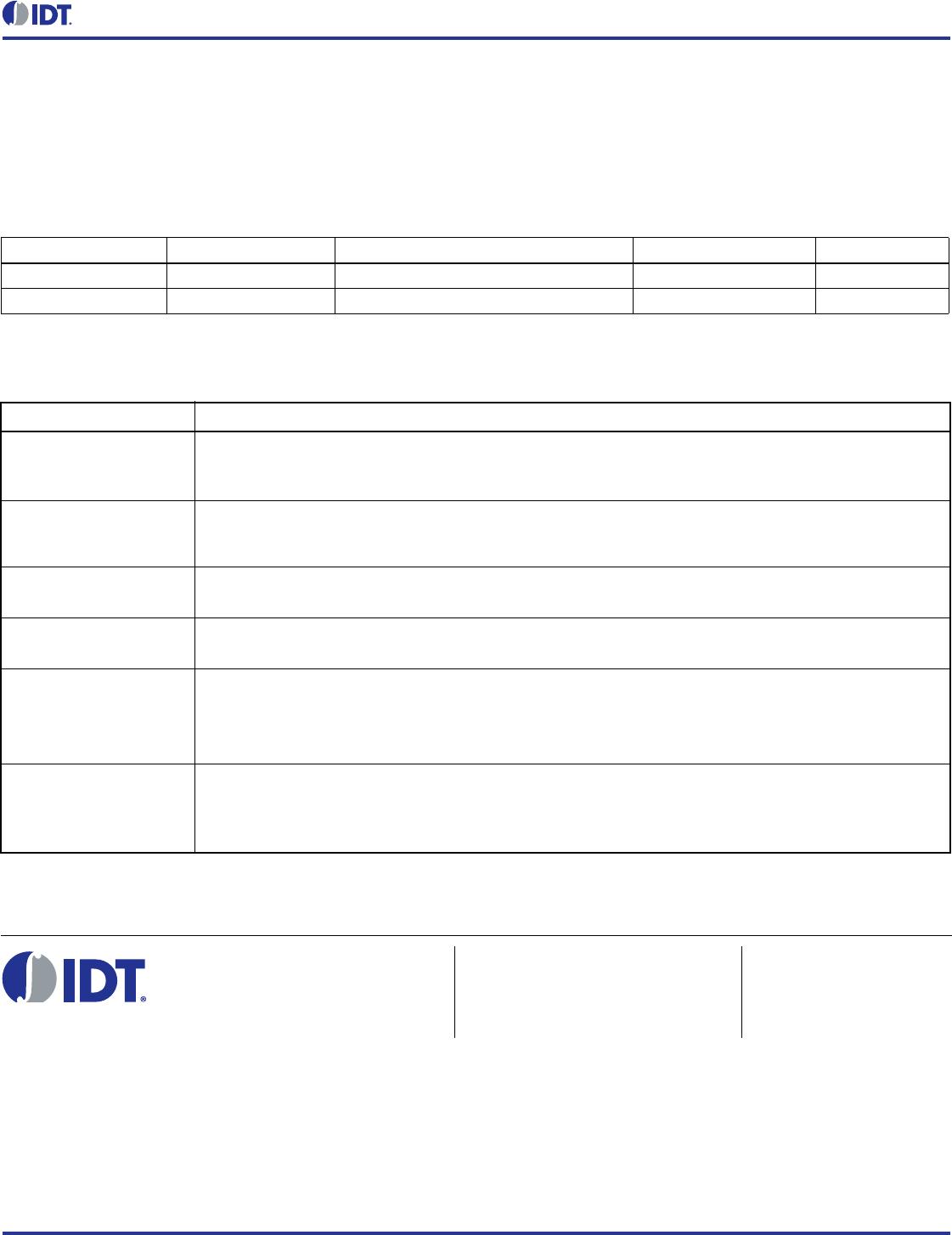

Revision History

Part/Order Number Marking Package Shipping Packaging Temperature

8S89831AKILF 831A “Lead-Free” 16 Lead VFQFN Tube -40C to 85C

8S89831AKILFT 831A “Lead-Free” 16 Lead VFQFN Tape & Reel -40C to 85C

Revision Date Description of Change

November 9, 2017

Replaced operating temperature with junction temperature in Absolute Maximum Ratings; also removed the

package thermal information

Changed the T

A

and T

B

temperature ranges to indicate “or” in all electrical table titles

October 3, 2017

Added a new bullet to Features about board temperature

Added “TB = -40°C to 105°C” to Tables 4A, 4B, 4C, 4D, and 5

Added Case Temperature Considerations

September 22, 2017

Updated the package outline drawings; however, no mechanical changes

Completed other minor improvements

June 22, 2017

Updated the thermal characteristics in Table 6

Updated the package drawings - no technical changes

January 27, 2016

Removed ICS from part numbers where needed.

General Description - Deleted ICS chip.

Ordering Information - Deleted quantity in tape in reel. Deleted LF note below table.

Updated header and footer.

April 22, 2010

Deleted Differential Input with Built-in 50

Termination Unused Input Handling application section. This section

does not apply when there is only one input.

Power Considerations - in Power Dissipation section, corrected Power (RT) calculation. Calculation = 18mW

from 98mW. Total Power and Junction Temperature calculations have also been updated.