17

LTC1553L

APPLICATIONS INFORMATION

WUU

U

this happens, FAULT will be triggered. Once FAULT is

triggered, G1 and G2 will be forced low immediately and

the LTC1553L will remain in this state until V

CC

power

supply is recycled or OUTEN is toggled.

Table 6 shows the suggested compensation components

for 5V input applications based on the inductor and output

capacitor values. The values were calculated using mul-

tiple paralleled 330µF AVX TPS series surface mount

tantalum capacitors as the output capacitor. The optimum

component values might deviate from the suggested

values slightly because of board layout and operating

condition differences.

An alternate output capacitor is the Sanyo MV-GX series.

Using multiple parallel 1500µF Sanyo MV-GX capacitors

for the output capacitor, Table 7 shows the suggested

compensation component value for a 5V input application

based on the inductor and output capacitor values.

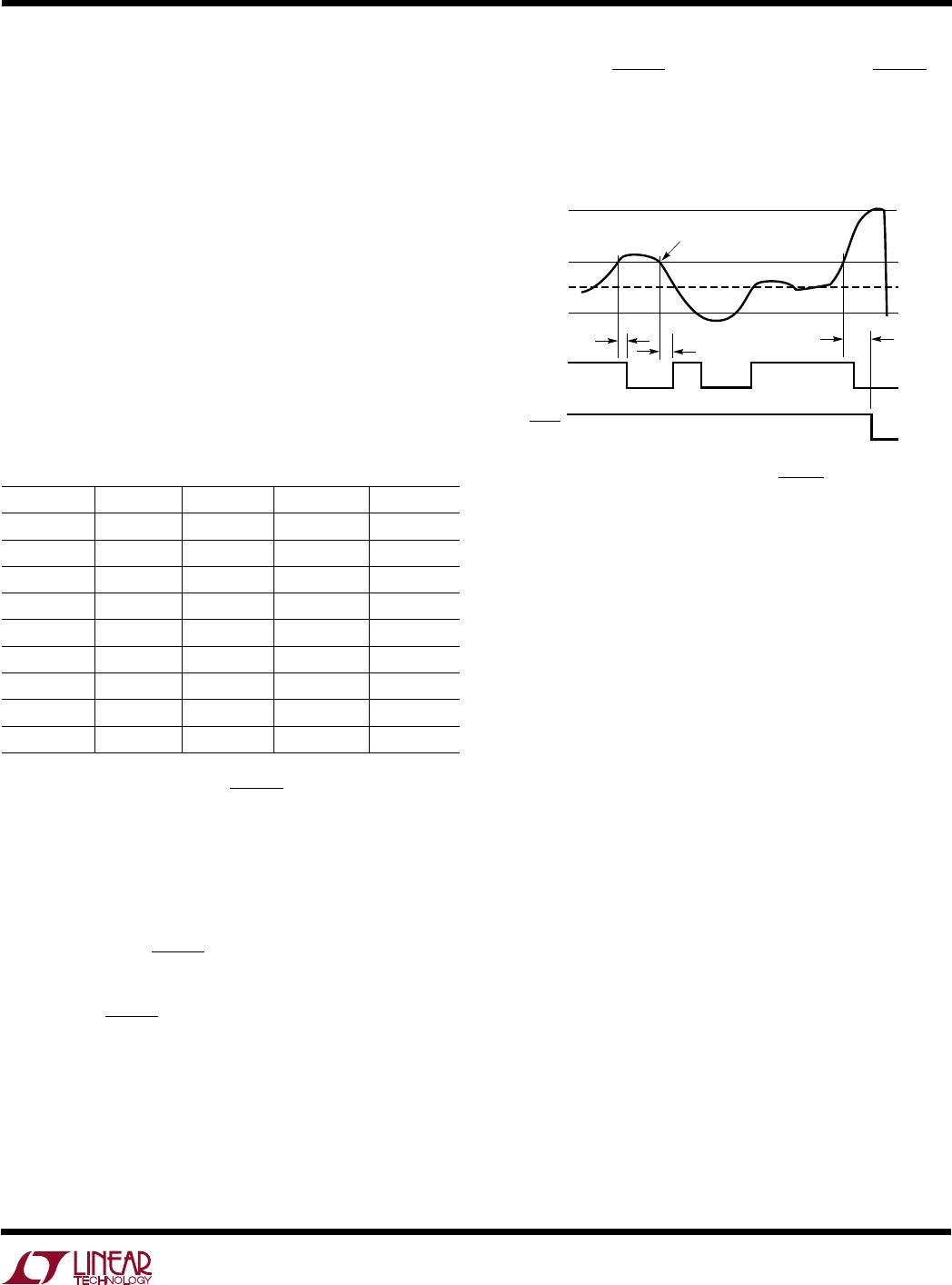

Table 7. Suggested Compensation Network for 5V Input

Application Using Multiple Paralleled 1500µF SANYO MV-GX

Output Capacitors

L

O

(

µ

H) C

O

(

µ

F) R

C

(k

Ω

)C

C

(

µ

F) C1 (pF)

1 4500 4.3 0.022 270

1 6000 5.6 0.0047 220

1 9000 8.2 0.01 150

2.7 4500 11 0.01 100

2.7 6000 15 0.01 82

2.7 9000 22 0.01 56

5.6 4500 24 0.01 56

5.6 6000 30 0.0047 39

5.6 9000 47 0.0047 27

VID0 to VID4, PWRGD and FAULT

The digital inputs (VID0 to VID4) program the internal DAC

which in turn controls the output voltage. These digital

input controls are intended to be static and are not

designed for high speed switching. Forcing V

OUT

to step

from a high to a low voltage by changing the VID

n

pins

quickly can cause FAULT to trip.

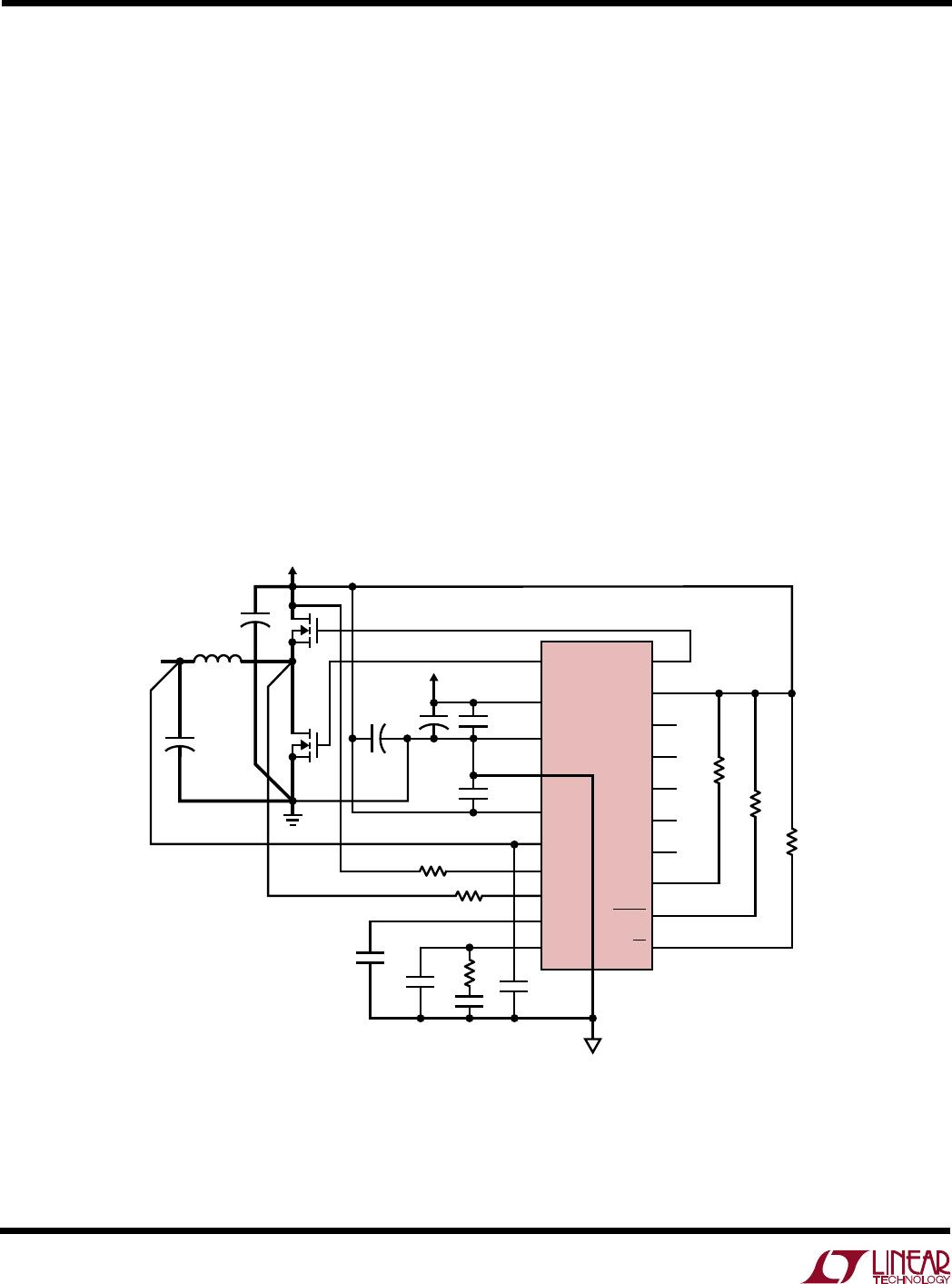

Figure 9 shows the relationship between the V

OUT

voltage,

PWRGD and FAULT. To prevent PWRGD from interrupting

the CPU unnecessarily, the LTC1553L has a built-in t

PWRBAD

delay to prevent noise at the SENSE pin from toggling

PWRGD. The internal time delay is designed to take about

500µs for PWRGD to go low and 1ms for it to recover.

Once PWRGD goes low, the internal circuitry watches for

the output voltage to exceed 115% of the rated voltage. If

RATED V

OUT

V

OUT

15%

5%

–5%

t

PWRBAD

t

PWRGD

t

FAULT

FAULT

PWRGD

1553L F09

Figure 9. PWRGD and FAULT

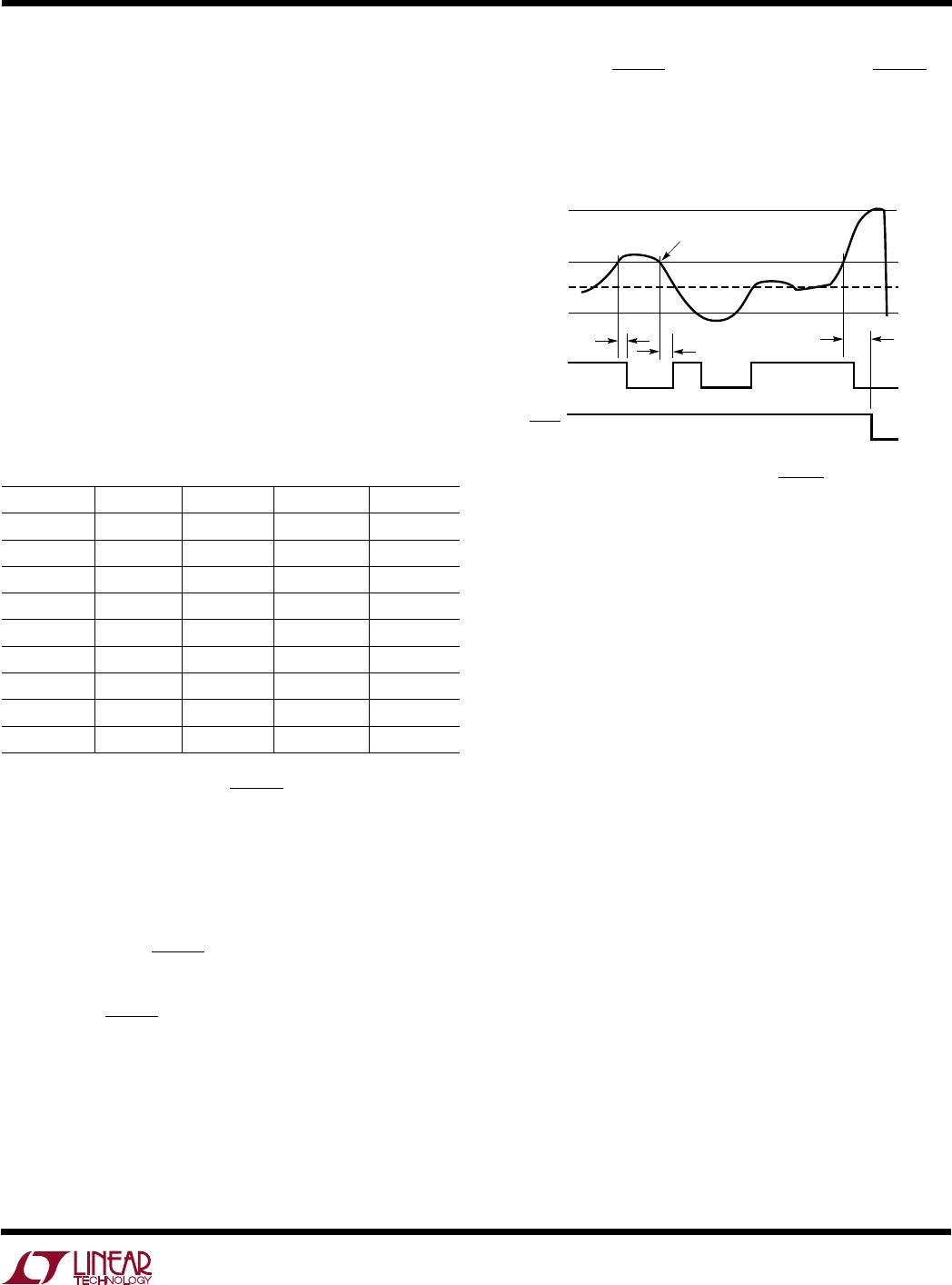

LAYOUT CONSIDERATIONS

When laying out the printed circuit board, the following

checklist should be used to ensure proper operation of the

LTC1553L. These items are also illustrated graphically in

the layout diagram of Figure 10. The thicker lines show the

high current paths. Note that at 10A current levels or

above, current density in the PC board itself is a serious

concern. Traces carrying high current should be as wide

as possible. For example, a PCB fabricated with 2oz

copper requires a minimum trace width of 0.15" to

carry 10A.

1. In general, layout should begin with the location of the

power devices. Be sure to orient the power circuitry so

that a clean power flow path is achieved. Conductor

widths should be maximized and lengths minimized.

After you are satisfied with the power path, the control

circuitry should be laid out. It is much easier to find

routes for the relatively small traces in the control

circuits than it is to find circuitous routes for high

current paths.

2. The GND and SGND pins should be shorted right at the

LTC1553L. This helps to minimize internal ground

disturbances in the LTC1553L and prevents differences

in ground potential from disrupting internal circuit

operation. This connection should then tie into the