© Semiconductor Components Industries, LLC, 2014

July, 2014 − Rev. 8

1 Publication Order Number:

MC14569B/D

MC14569B

Programmable Divide-By-N

Dual 4-Bit Binary/BCD

Down Counter

The MC14569B is a programmable divide−by−N dual 4−bit binary

or BCD down counter constructed with MOS P−Channel and

N−Channel enhancement mode devices (complementary MOS) in

a monolithic structure.

This device has been designed for use with the MC14568B phase

comparator/counter in frequency synthesizers, phase−locked loops,

and other frequency division applications requiring low power

dissipation and/or high noise immunity.

Features

• Speed−up Circuitry for Zero Detection

• Each 4−Bit Counter Can Divide Independently in BCD or Binary Mode

• Can be Cascaded With MC14526B for Frequency Synthesizer

Applications

• All Outputs are Buffered

• Schmitt Triggered Clock Conditioning

• NLV Prefix for Automotive and Other Applications Requiring

Unique Site and Control Change Requirements; AEC−Q100

Qualified and PPAP Capable

• This Device is Pb−Free and is RoHS Compliant

MAXIMUM RATINGS (Voltages Referenced to V

SS

)

Symbol

Parameter Value Unit

V

DD

DC Supply Voltage Range −0.5 to +18.0 V

V

in

, V

out

Input or Output Voltage Range

(DC or Transient)

−0.5 to V

DD

+ 0.5 V

I

in

, I

out

Input or Output Current

(DC or Transient) per Pin

±10 mA

P

D

Power Dissipation, per Package

(Note 1)

500 mW

T

A

Ambient Temperature Range −55 to +125 °C

T

stg

Storage Temperature Range −65 to +150 °C

T

L

Lead Temperature

(8−Second Soldering)

260 °C

Stresses exceeding those listed in the Maximum Ratings table may damage the

device. If any of these limits are exceeded, device functionality should not be

assumed, damage may occur and reliability may be affected.

1. Temperature Derating: “D/DW” Package: –7.0 mW/_C From 65_C To 125_C

This device contains protection circuitry to guard against damage due to high

static voltages or electric fields. However, precautions must be taken to avoid

applications of any voltage higher than maximum rated voltages to this

high−impedance circuit. For proper operation, V

in

and V

out

should be constrained

to the range V

SS

≤ (V

in

or V

out

) ≤ V

DD

.

Unused inputs must always be tied to an appropriate logic voltage level

(e.g., either V

SS

or V

DD

). Unused outputs must be left open.

http://onsemi.com

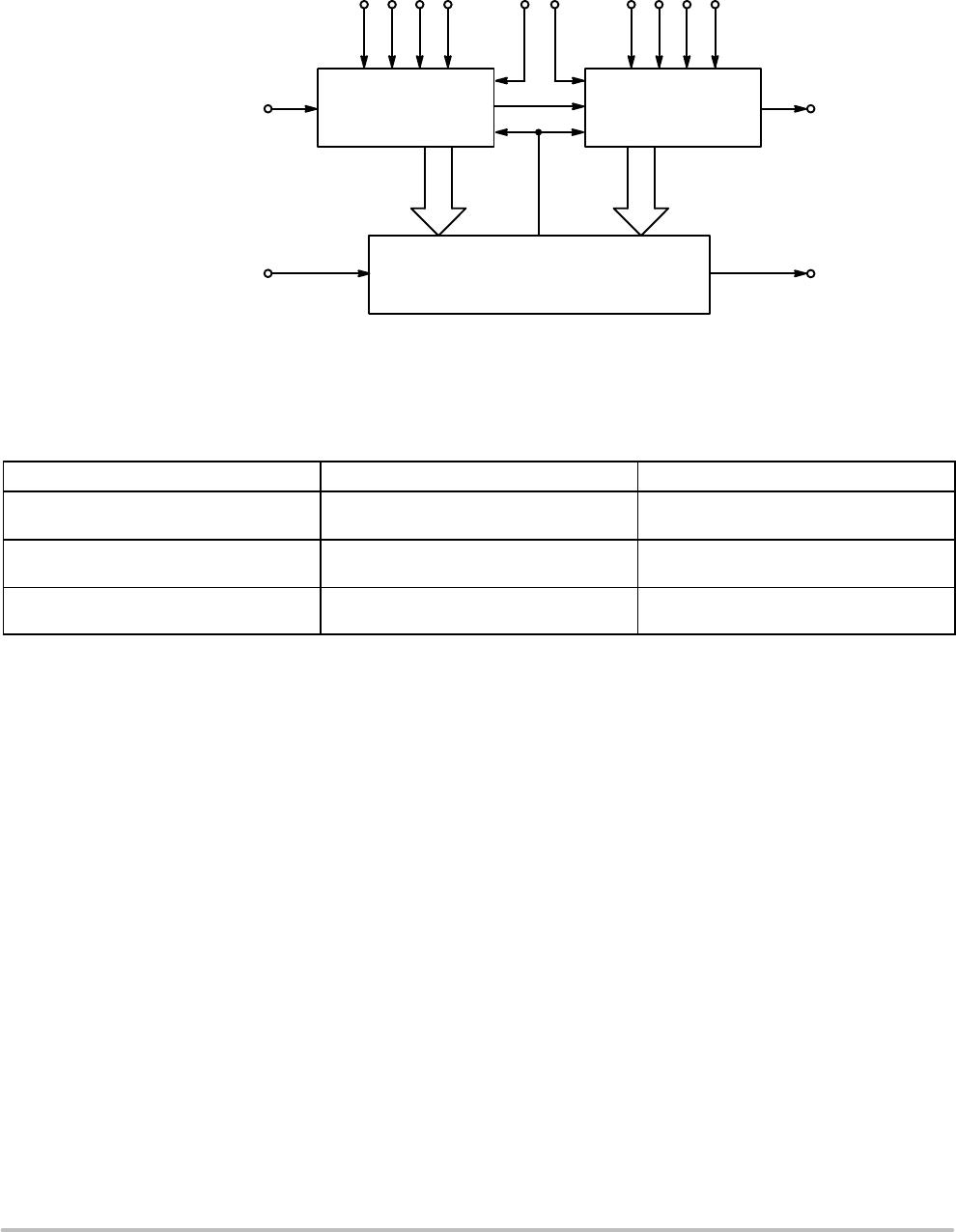

MARKING DIAGRAM

SOIC−16 WB

DW SUFFIX

CASE 751G

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb−Free Package

See detailed ordering and shipping information in the package

dimensions section on page 2 of this data sheet.

ORDERING INFORMATION

14569B

AWLYYWWG

16

1

13

14

15

16

9

10

11

125

4

3

2

1

8

7

6

P5

P6

P7

Q

V

DD

CLOCK

CTL

2

P4

P1

P0

CTL1

ZERO

DETECT

V

SS

CASCADE

FEEDBACK

P3

P2

PIN ASSIGNMENT