IDT

TM

/ICST

M

PC MAIN CLOCK 1336—06/01/09

ICS9UMS9610

PC MAIN CLOCK

15

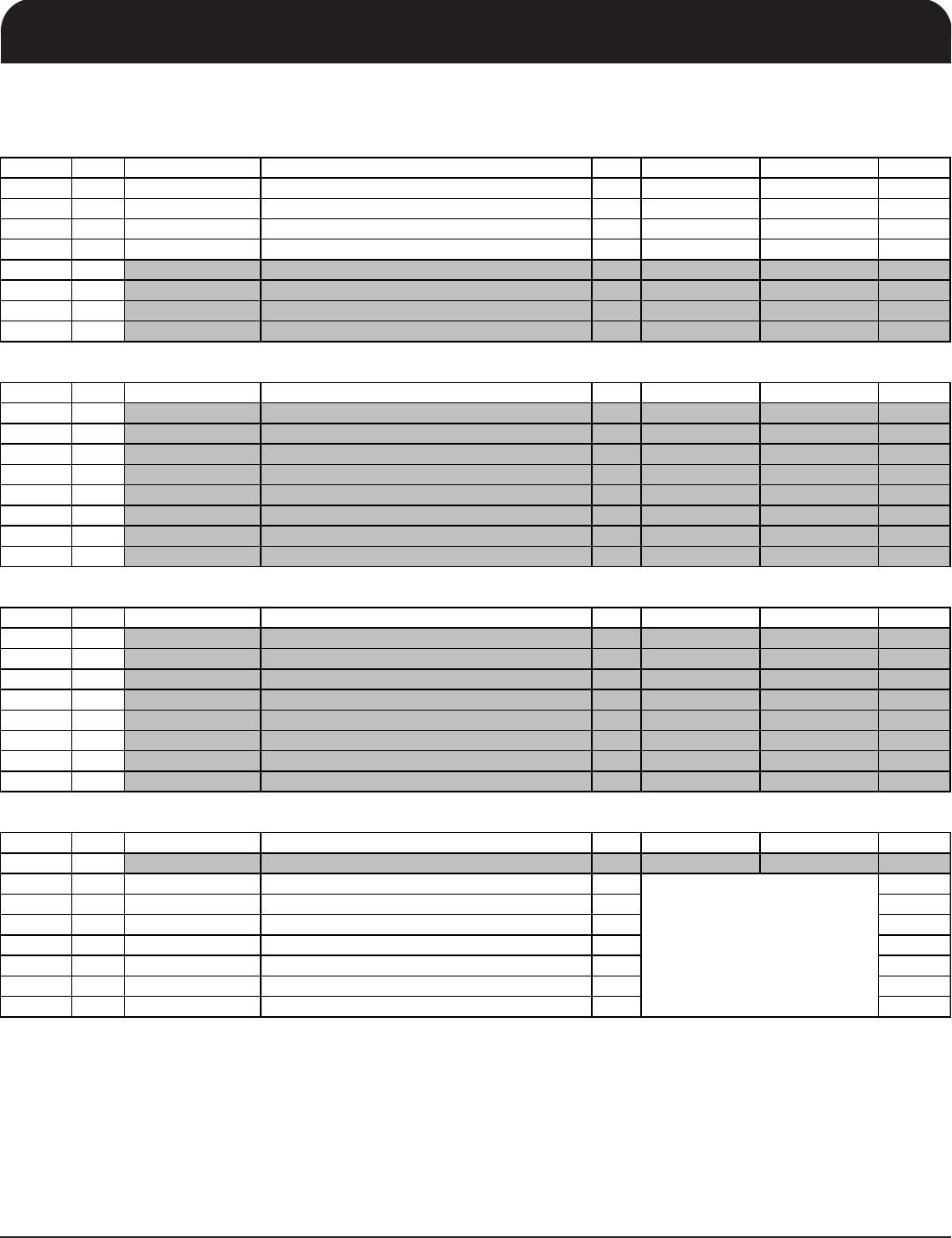

Byte 16 M/N Enable Register

Bit

s

Pin # Name Control Function T

e 0 1 Default

Bit 7

MN Enable Enables PLL MN pro

rammin

RW MN Disabled MN Enabled 0

Bit 6

Reserved 0

Bit 5

Reserved 0

Bit 4

Reserved 0

Bit 3

Reserved 0

Bit 2

Reserved 0

Bit 1

Reserved 0

Bit 0

Reserved 0

Byte 17 CPU PLL Spread Spectrum Index Register

Bit

s

Pin # Name Control Function T

e 0 1 Default

Bit 7

CPUSSP7 RW X

Bit 6

CPUSSP6 RW X

Bit 5

CPUSSP5 RW X

Bit 4

CPUSSP4 RW X

Bit 3

CPUSSP3 RW X

Bit 2

CPUSSP2 RW X

Bit 1

CPUSSP1 RW X

Bit 0

CPUSSP0 RW X

Byte 18 CPU PLL Spread Spectrum Index Register

Bit

s

Pin # Name Control Function T

e 0 1 Default

Bit 7

CPUSSP15 RW X

Bit 6

CPUSSP14 RW X

Bit 5

CPUSSP13 RW X

Bit 4

CPUSSP12 RW X

Bit 3

CPUSSP11 RW X

Bit 2

CPUSSP10 RW X

Bit 1

CPUSSP9 RW X

Bit 0

CPUSSP8 RW X

Byte 19 LCD100 PLL Spread Spectrum Index Register

Bit

s

Pin # Name Control Function T

e 0 1 Default

Bit 7

LCDSSP7 RW X

Bit 6

LCDSSP6 RW X

Bit 5

LCDSSP5 RW X

Bit 4

LCDSSP4 RW X

Bit 3

LCDSSP3 RW X

Bit 2

LCDSSP2 RW X

Bit 1

LCDSSP1 RW X

Bit 0

LCDSSP0 RW X

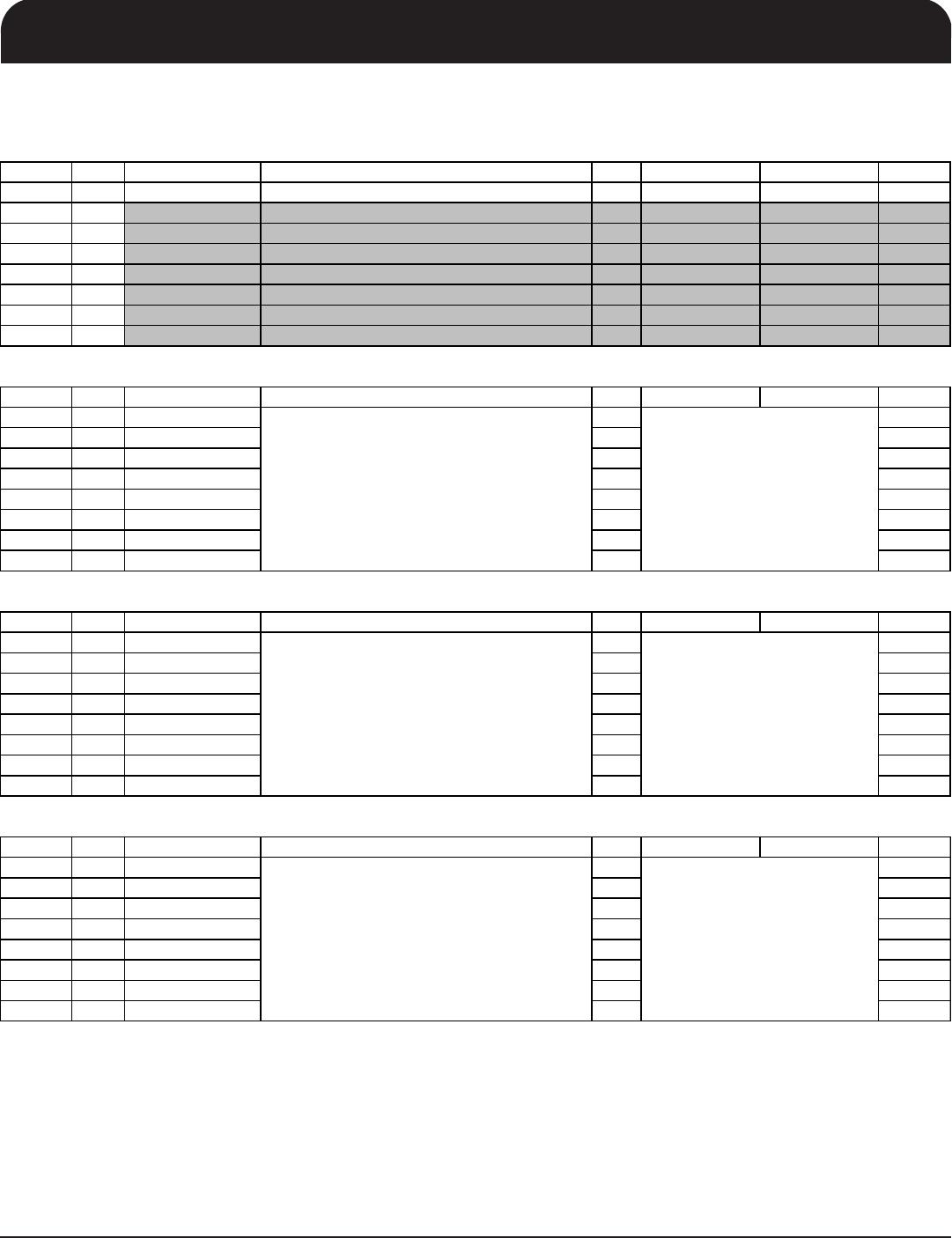

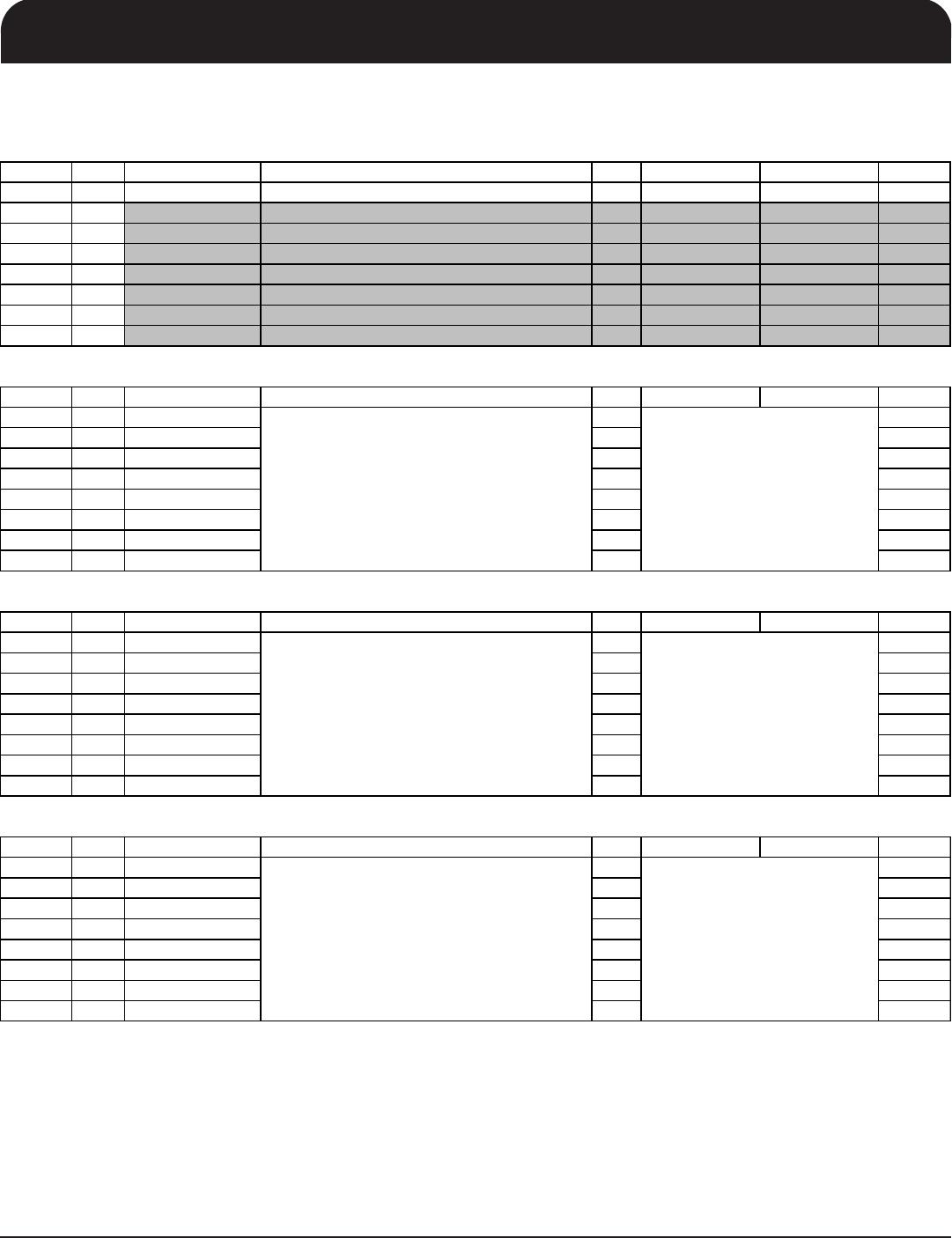

Spread Spectrum Programming bit(7:0)

Contact IDT before editing these values.

These Spread Spectrum bits in

Byte 19 and 20 will program the

spread percentage of the CPU

and SRC outputs

Spread Spectrum Programming bit(7:0)

Contact IDT before editing these values.

These Spread Spectrum bits in

Byte 17 and 18 will program the

spread percentage of the CPU

and SRC outputs

Spread Spectrum Programming bit(15:8)

Contact IDT before editing these values.

These Spread Spectrum bits in

Byte 17 and 18 will program the

spread percentage of the CPU

and SRC outputs