Innovate with IDT and accelerate your future networks. Contact:

www.IDT.com

For Sales

800-345-7015

408-284-8200

Fax: 408-284-2775

For Tech Support

408-284-6578

pcclockhelp@idt.com

Corporate Headquarters

Integrated Device Technology, Inc.

6024 Silver Creek Valley Road

San Jose, CA 95138

United States

800 345 7015

+408 284 8200 (outside U.S.)

Asia Pacific and Japan

Integrated Device Technology

Singapore (1997) Pte. Ltd.

Reg. No. 199707558G

435 Orchard Road

#20-03 Wisma Atria

Singapore 238877

+65 6 887 5505

Europe

IDT Europe, Limited

Prime House

Barnett Wood Lane

Leatherhead, Surrey

United Kingdom KT22 7DE

+44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated

Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks

or registered trademarks used to identify products or services of their respective owners.

Printed in USA

TM

ICS9UMS9610

PC MAIN CLOCK

20

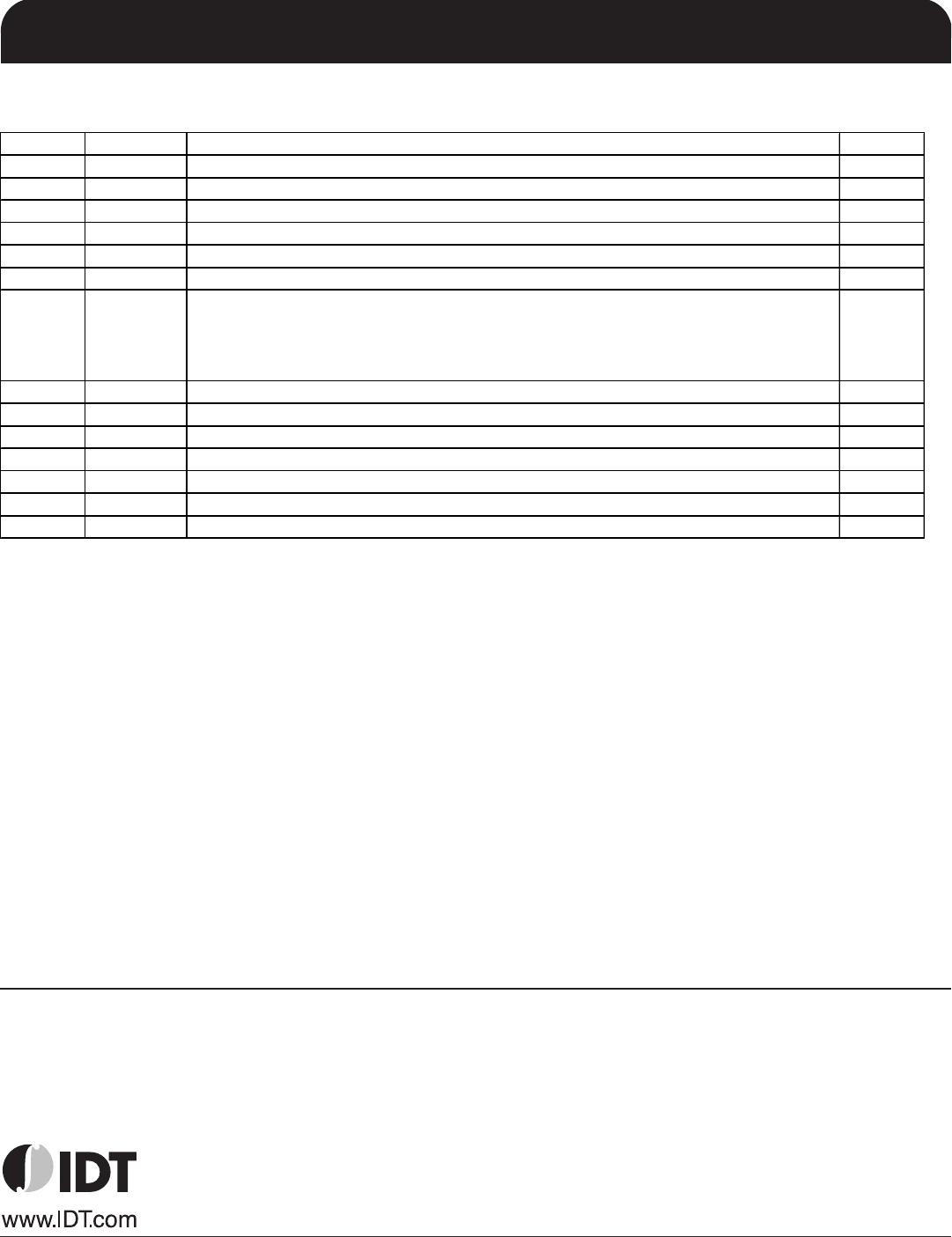

Revision History

Rev. Issue Date Description Page #

0.1 04/25/07 Initial Release -

0.15 05/03/07 Corrected CLKPWRGD#/PD polarity 1

0.2 5/18/2007 Updated Test Clarification Table with the correct voltage levels. -

0.3 8/31/2007 Updated Input Pin names to indicate maximum Input volta

e level -

0.4 9/11/2007 Added Logic Level and Input Level Tolerance Columns to Pin Descriptions. 2, 3

0.5 9/13/2007 Clarified that X1 is 1.5V only input 2

0.6 10/23/007

1. Byte Count in Byte 15 is 7 bits, not 8 bits. B15b7 is now reserved.

2. Modified PLL programming formulas in Bytes(4:9). N is 12 bits instead of 10 bits.

3. Changed REF_3.3 output name to reflect default drive strength (new name is

REF_3.3_2x). Various

0.7 11/6/2007 Updated B

tes [9:4]. 12-13

0.8 11/29/2007 Added Bytes 16-22 to the SMBUS. 15-16

0.9 2/26/2008 Added MLF Top Mark Information. 18

0.91 7/8/2008 Updated Electrical Specifications 5-7

0.92 7/21/2008 Updated Electrical Specifications 5-7

A 5/21/2009 Moved to final. -

B 6/1/2009 Updated electrical specs; TA spec in ordering information. Various