ZL40217 Data Sheet

15

Microsemi Corporation

3.4 Power Supply

This device operates employing either a 2.5V supply or 3.3V supply.

3.4.1 Sensitivity to power supply noise

Power supply noise from sources such as switching power supplies and high-power digital components such as

FPGAs can induce additive jitter on clock buffer outputs. The ZL40217 is equipped with a low drop out (LDO) linear

power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip

measures in combination with the simple recommended power supply filtering and PCB layout minimize additive

jitter from power supply noise.

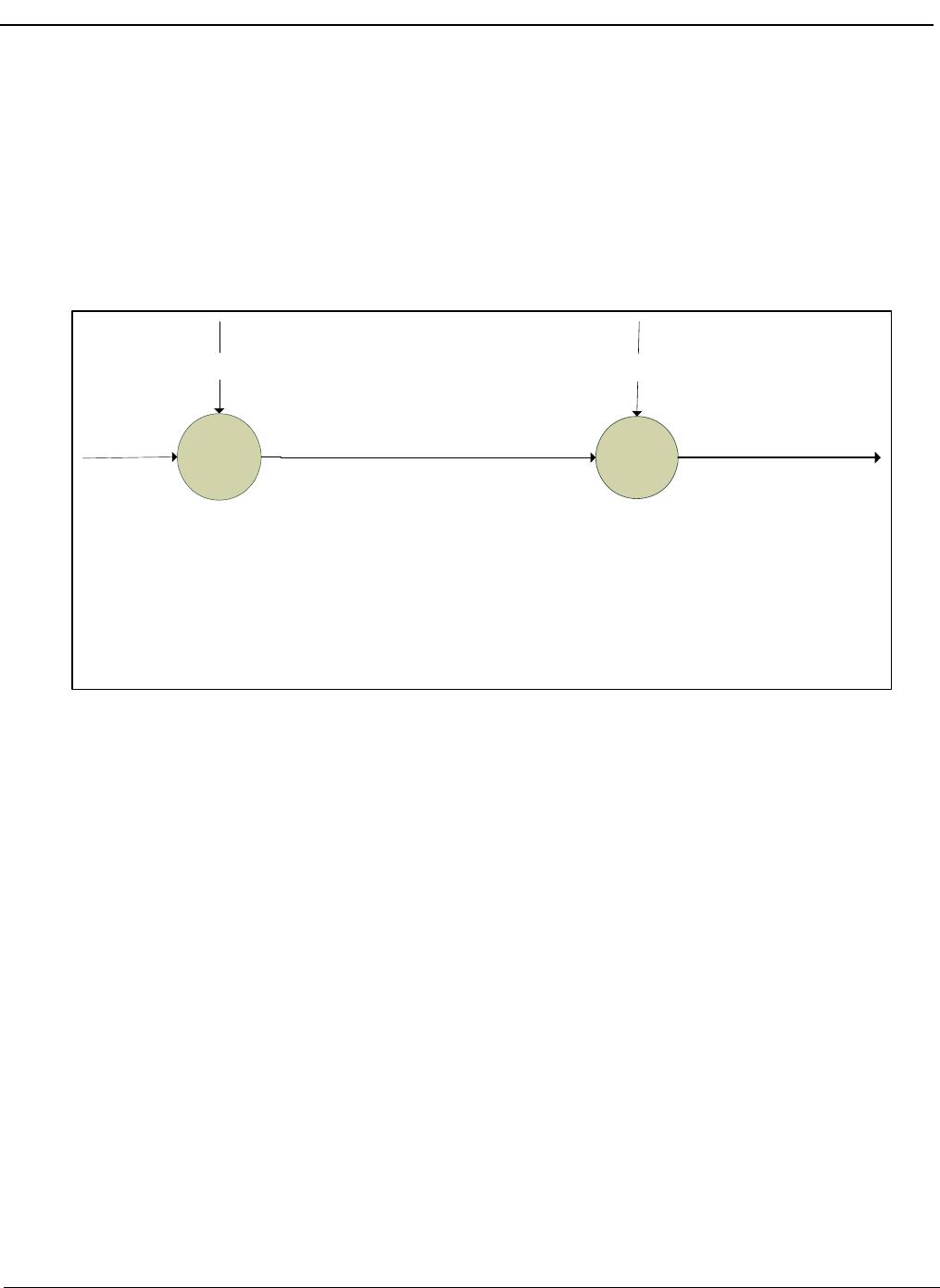

3.4.2 Power supply filtering

Jitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device

should be isolated from the power planes connected to its power supply pins as shown in Figure •.

• 10 µF capacitors should be size 0603 or size 080

5 X5R or X7R ceramic, 6.3 V minimum rating

• 0.1 µF capacitors should be

size 0402 X5R ceramic, 6.3 V minimum rating

• Capacitors should be placed next to the

connected device power pins

• A 0.3 ohm resistor is recommended

ZL40217

1

8

9

19

22

32

0.1 µF

0.1 µF

vdd_core

10 µF

0.1 µF

0.15 Ω

vdd

0.1 µF

10 µF

Figure 18 - Decoupling Connections for Power Pins

3.4.3 PCB layout considerations

The power nets in Figure 18 can be implemented either as a plane island or routed power topology without

changing the overall jitter p

erformance of the device.