ICS345

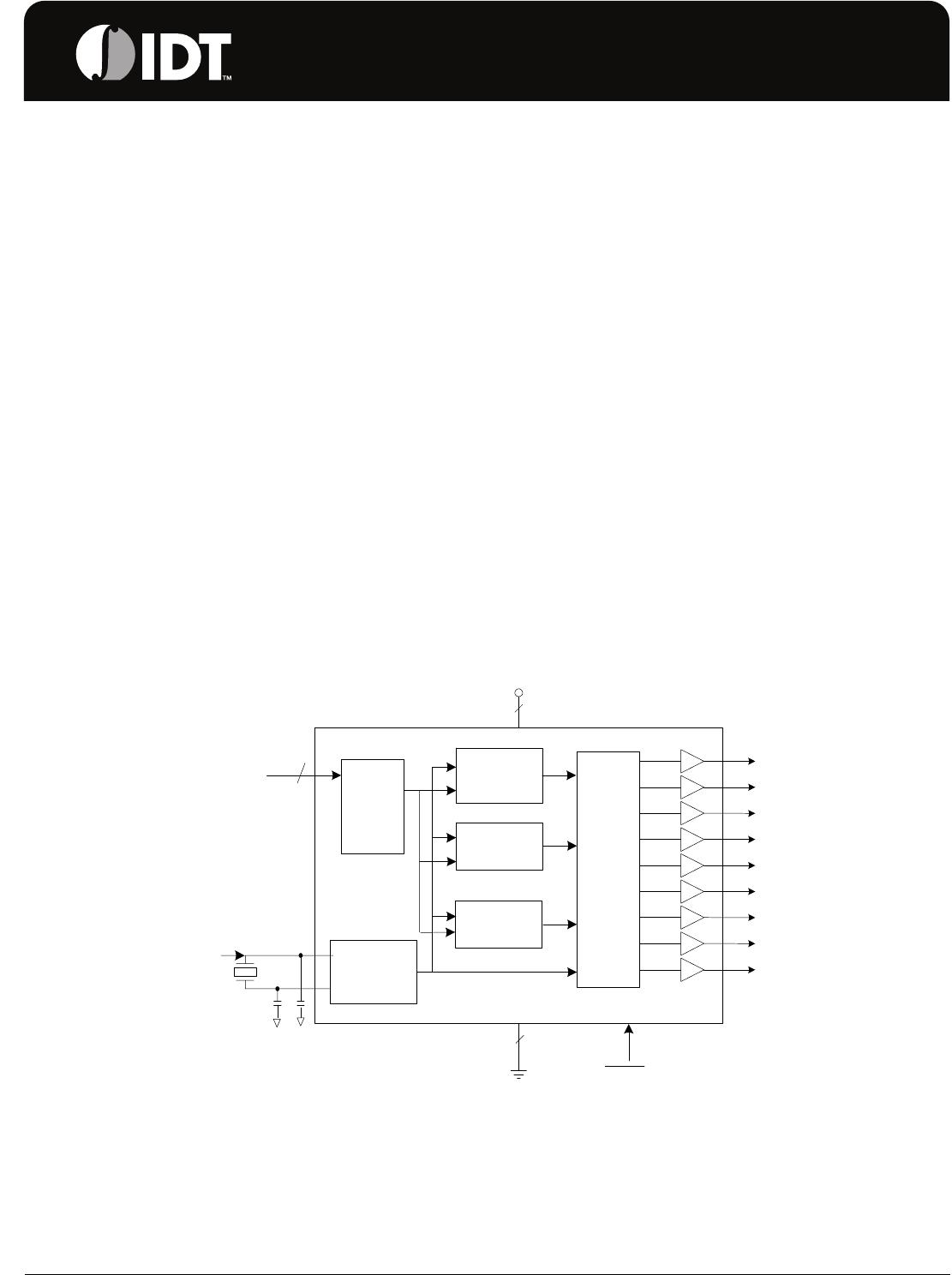

TRIPLE PLL FIELD PROGRAMMABLE SS VERSACLOCK SYNTHESIZER EPROM CLOCK SYNTHESIZER

IDT™ / ICS™

TRIPLE PLL FIELD PROGRAMMABLE SS VERSACLOCK SYNTHESIZER 3

ICS345 REV M 051310

External Components

Series Termination Resistor

Clock output traces over one inch should use series

termination. To series terminate a 50Ω trace (a commonly

used trace impedance), place a 33Ω resistor in series with

the clock line, as close to the clock output pin as possible.

The nominal impedance of the clock output is 20Ω.

Decoupling Capacitors

As with any high-performance mixed-signal IC, the ICS345

must be isolated from system power supply noise to perform

optimally.

Decoupling capacitors of 0.01µF must be connected

between each VDD and the PCB ground plane.

Crystal Load Capacitors

The device crystal connections should include pads for

small capacitors from X1 to ground and from X2 to ground.

These capacitors are used to adjust the stray capacitance of

the board to match the nominally required crystal load

capacitance. Because load capacitance can only be

increased in this trimming process, it is important to keep

stray capacitance to a minimum by using very short PCB

traces (and no vias) between the crystal and device. Crystal

capacitors must be connected from each of the pins X1 and

X2 to ground.

The value (in pF) of these crystal caps should equal (C

L

-6

pF)*2. In this equation, C

L

= crystal load capacitance in pF.

Example: For a crystal with a 16 pF load capacitance, each

crystal capacitor would be 20 pF [(16-6) x 2 = 20].

PCB Layout Recommendations

For optimum device performance and lowest output phase

noise, the following guidelines should be observed.

1) Each 0.01µF decoupling capacitor should be mounted on

the component side of the board as close to the VDD pin as

possible. No vias should be used between decoupling

capacitor and VDD pin. The PCB trace to VDD pin should

be kept as short as possible, as should the PCB trace to the

ground via.

2) The external crystal should be mounted just next to the

device with short traces. The X1 and X2 traces should not

be routed next to each other with minimum spaces, instead

they should be separated and away from other traces.

3) To minimize EMI, the 33Ω series termination resistor (if

needed) should be placed close to the clock output.

4) An optimum layout is one with all components on the

same side of the board, minimizing vias through other signal

layers.

ICS345 Configuration Capabilities

The architecture of the ICS345 allows the user to easily

configure the device to a wide range of output frequencies,

for a given input reference frequency.

The frequency multiplier PLL provides a high degree of

precision. The M/N values (the multiplier/divide values

available to generate the target VCO frequency) can be set

within the range of M = 1 to 2048 and N = 1 to 1024.

The ICS345 also provides separate output divide values,

from 2 through 20, to allow the two output clock banks to

support widely differing frequency values from the same

PLL.

Each output frequency can be represented as:

IDT VersaClock Software

IDT applies years of PLL optimization experience into a user

friendly software that accepts the user’s target reference

clock and output frequencies and generates the lowest jitter,

lowest power configuration, with only a press of a button.

The user does not need to have prior PLL experience or

determine the optimal VCO frequency to support multiple

output frequencies.

VersaClock software quickly evaluates accessible VCO

frequencies with available output divide values and provides

an easy to understand, bar code rating for the target output

frequencies. The user may evaluate output accuracy,

performance trade-off scenarios in seconds.

utputFreq

REFFreq

OutputDivide

--------------------------------------

M

N

-----

⋅=