XC2C32A CoolRunner-II CPLD

DS310 (v2.1) November 6, 2008 www.xilinx.com 9

Product Specification

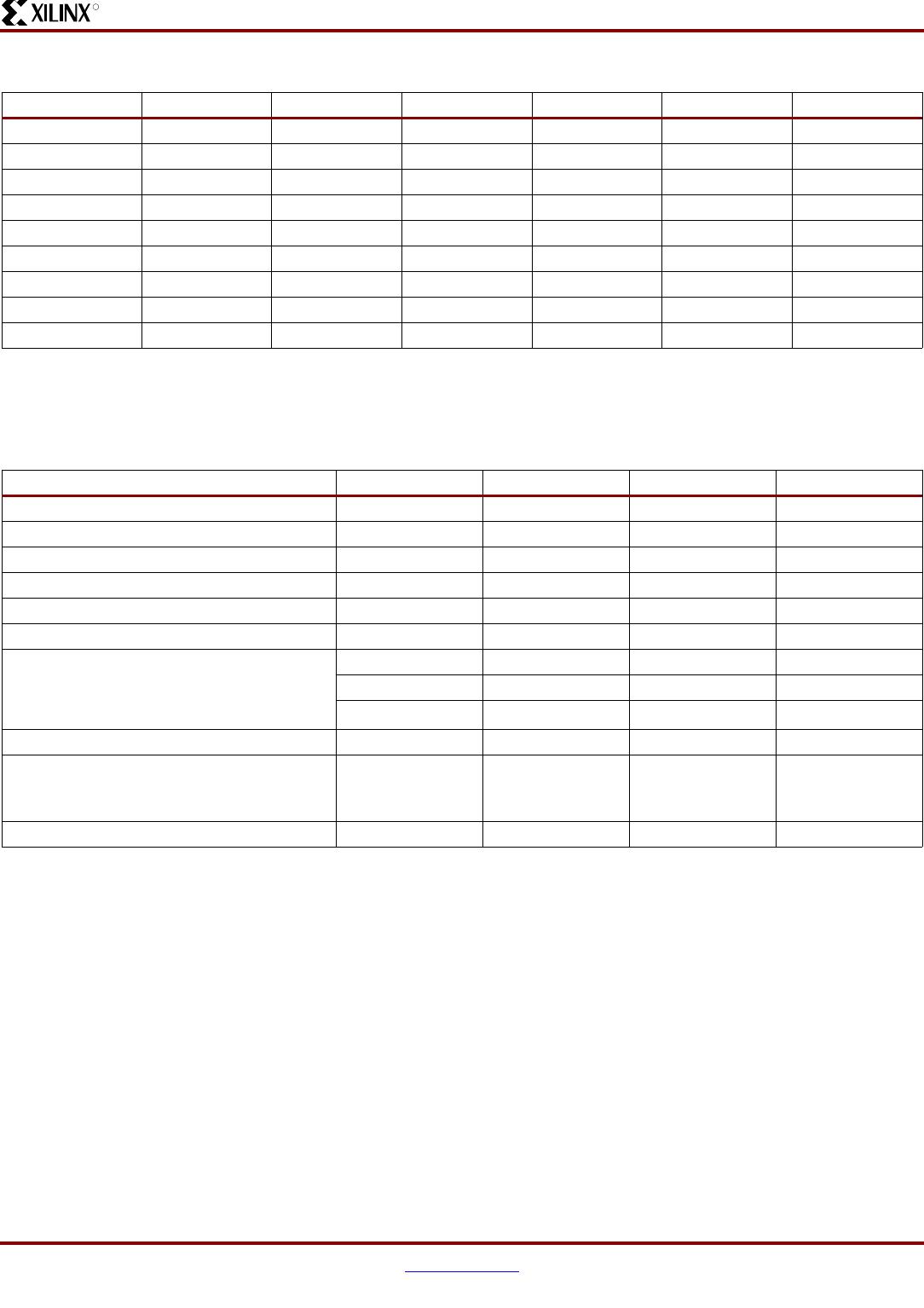

XC2C32A Global, JTAG, Power/Ground, and No Connect Pins

2 8 9 8 2 K3 Bank 1

2 9 10 9 3 H3 Bank 1

2 10 11 5 K5 Bank 1

211 126H5Bank 1

21213148H8Bank 1

2 13171812K8Bank 1

2 14181913H10Bank 1

2 15192014G10Bank 1

2 16 22 16 F10 Bank 1

Notes:

1. This is an obsolete package type. It remains here for legacy support only.

2. GTS = global output enable, GSR = global set reset, GCK = global clock.

3. GTS, GSR, and GCK pins can also be used for general purpose I/O.

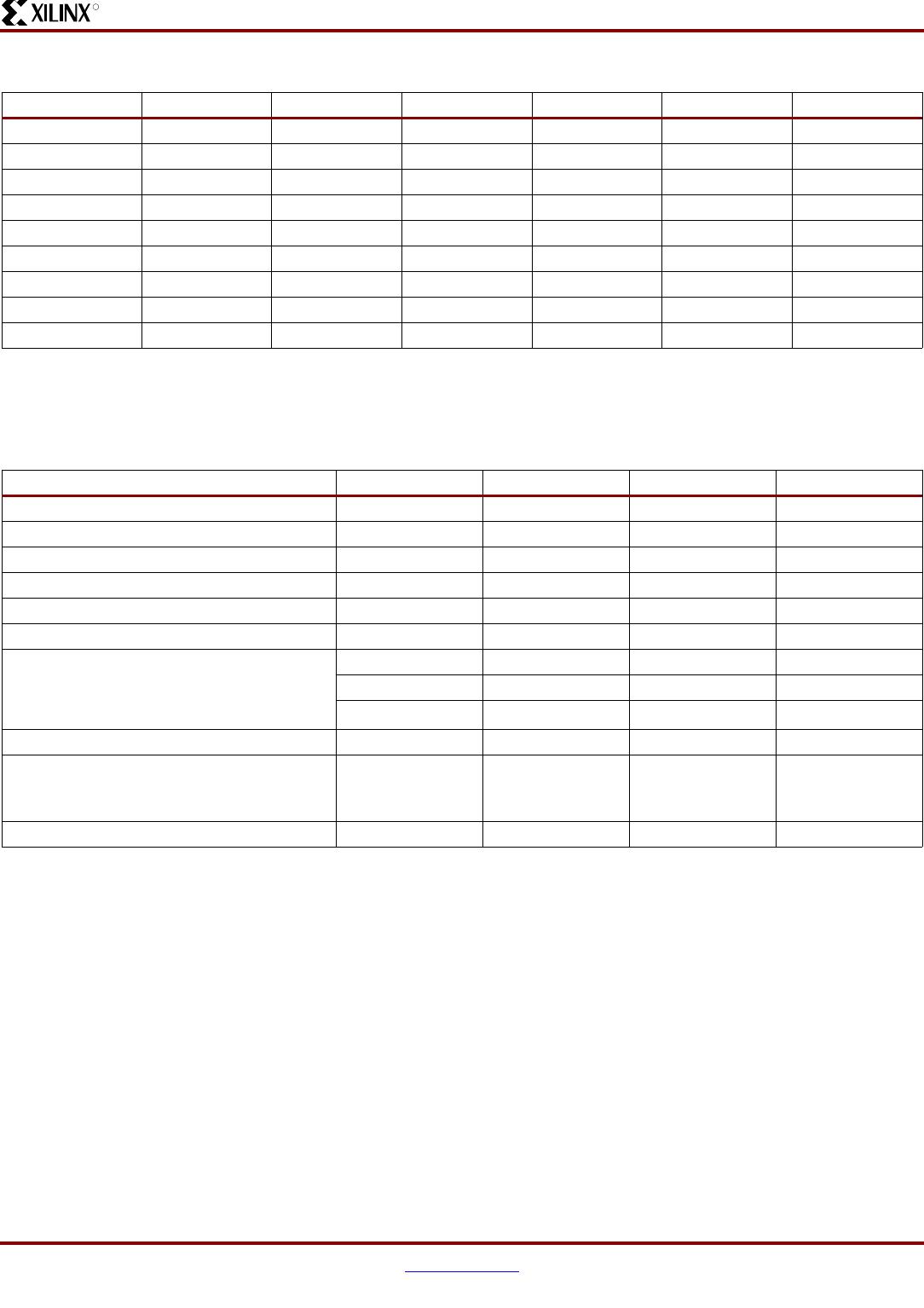

Pin Type QFG32 PC44

(1)(2)

VQ44

(2)

CP56

(2)

TCK 16 17 11 K10

TDI 14 15 9 J10

TDO 25 30 24 A6

TMS 15 16 10 K9

Input Only 22 (bank 2) 24 (bank 2) 18 (bank 2) D10 (bank 2)

V

CCAUX

(JTAG supply voltage) 4 41 35 D3

Power internal (V

CC

)

Power bank 1 I/O (V

CCIO1

)

Power bank 2 I/O (V

CCIO2

)

20 21 15 G8

12 13 7 H6

27 32 26 C6

Ground 11, 21, 26 10,23,31 4,17,25 H4, F8, C7

No connects - - K4, K6, K7, H7,

E10, A7, A9, D8,

A5, A8, A4, C3

Total user I/O (includes dual function pins) 21 33 33 33

Notes:

1. This is an obsolete package type. It remains here for legacy support only.

2. All packages pin compatible with larger macrocell densities.

Pin Descriptions (Continued)

Function Block Macrocell QFG32 PC44

(1)

VQ44 CP56 I/O Bank