Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

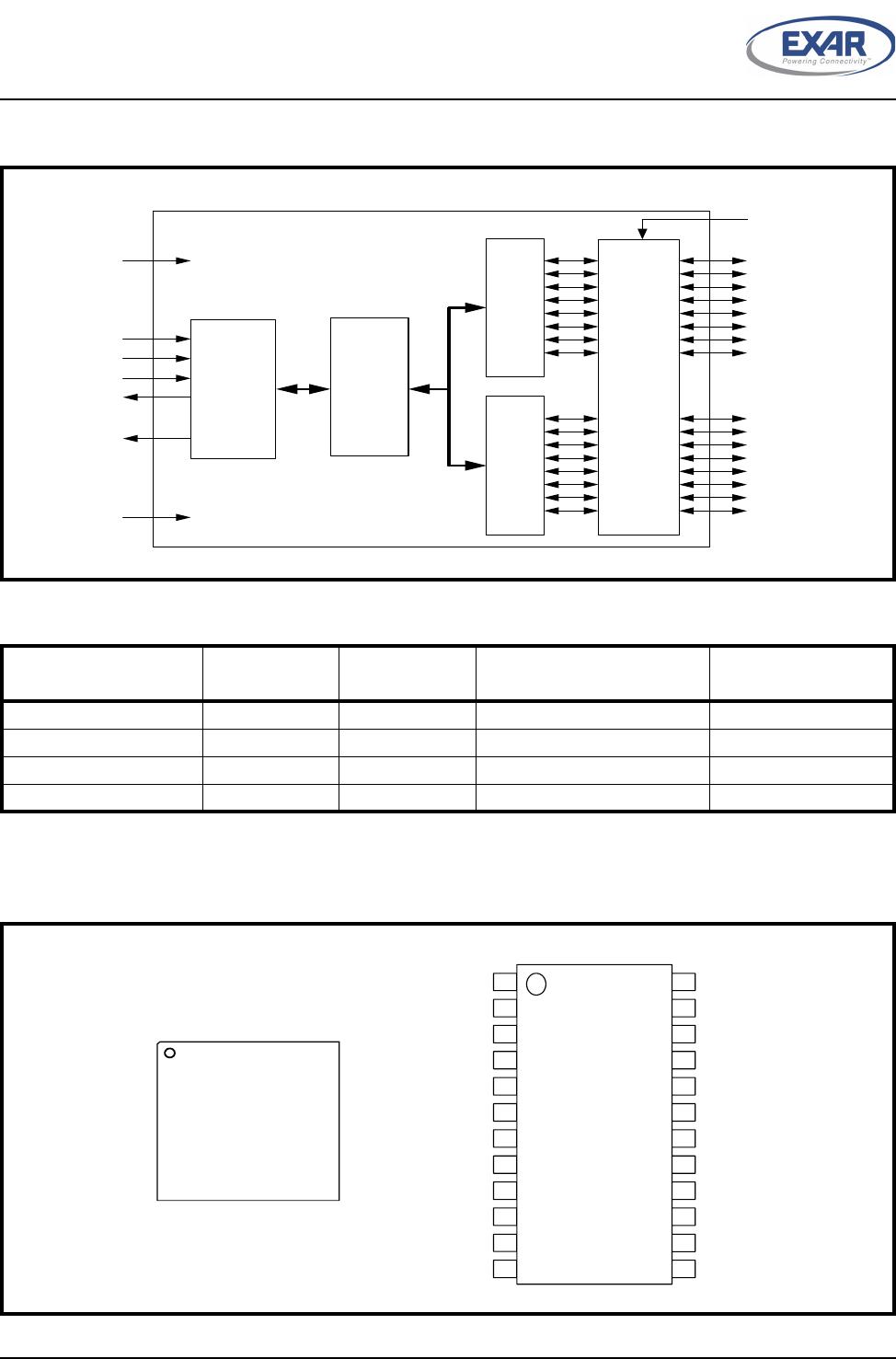

XRA1405

16-BIT SPI GPIO EXPANDER WITH INTEGRATED LEVEL SHIFTERS

SEPTEMBER 2011 REV. 1.0.0

GENERAL DESCRIPTION

The XRA1405 is an 16-bit GPIO expander with an

SPI interface. After power-up, the XRA1405 has

internal 100K ohm pull-up resistors on each I/O pin

that can be individually enabled.

In addition, the GPIOs on the XRA1405 can

individually be controlled and configured. As outputs,

the GPIOs can be outputs that are high, low or in

three-state mode. The three-state mode feature is

useful for applications where the power is removed

from the remote devices, but they may still be

connected to the GPIO expander.

As inputs, the internal pull-up resistors can be

enabled or disabled and the input polarity can be

inverted. The interrupt can be programmed for

different behaviors. The interrupts can be

programmed to generate an interrupt on the rising

edge, falling edge or on both edges. The interrupt

can be cleared if the input changes back to its original

state or by reading the current state of the inputs.

The XRA1405 is available in 24-pin QFN and 24-pin

TSSOP packages.

FEATURES

• 1.65V to 3.6V operating voltage

• 16 General Purpose I/Os (GPIOs)

• Integrated Level Shifters

• 5V tolerant inputs

• Maximum stand-by current of 1uA at +1.8V

• SPI bus interface

■ SPI Clock Frequency up to 26MHz

• Individually programmable inputs

■ Internal pull-up resistors

■ Polarity inversion

■ Individual interrupt enable

■ Rising edge and/or Falling edge interrupt

■ Input filter

• Individually programmable outputs

■ Output Level Control

■ Output Three-State Control

• Open-drain active low interrupt output

• 3kV HBM ESD protection per JESD22-A114F

• 200mA latch-up performance per JESD78B

APPLICATIONS

• Personal Digital Assistants (PDA)

• Cellular Phones/Data Devices

• Battery-Operated Devices

• Global Positioning System (GPS)

• Bluetooth