XRA1405

5

REV. 1.0.0 16-BIT SPI GPIO EXPANDER WITH INTEGRATED LEVEL SHIFTERS

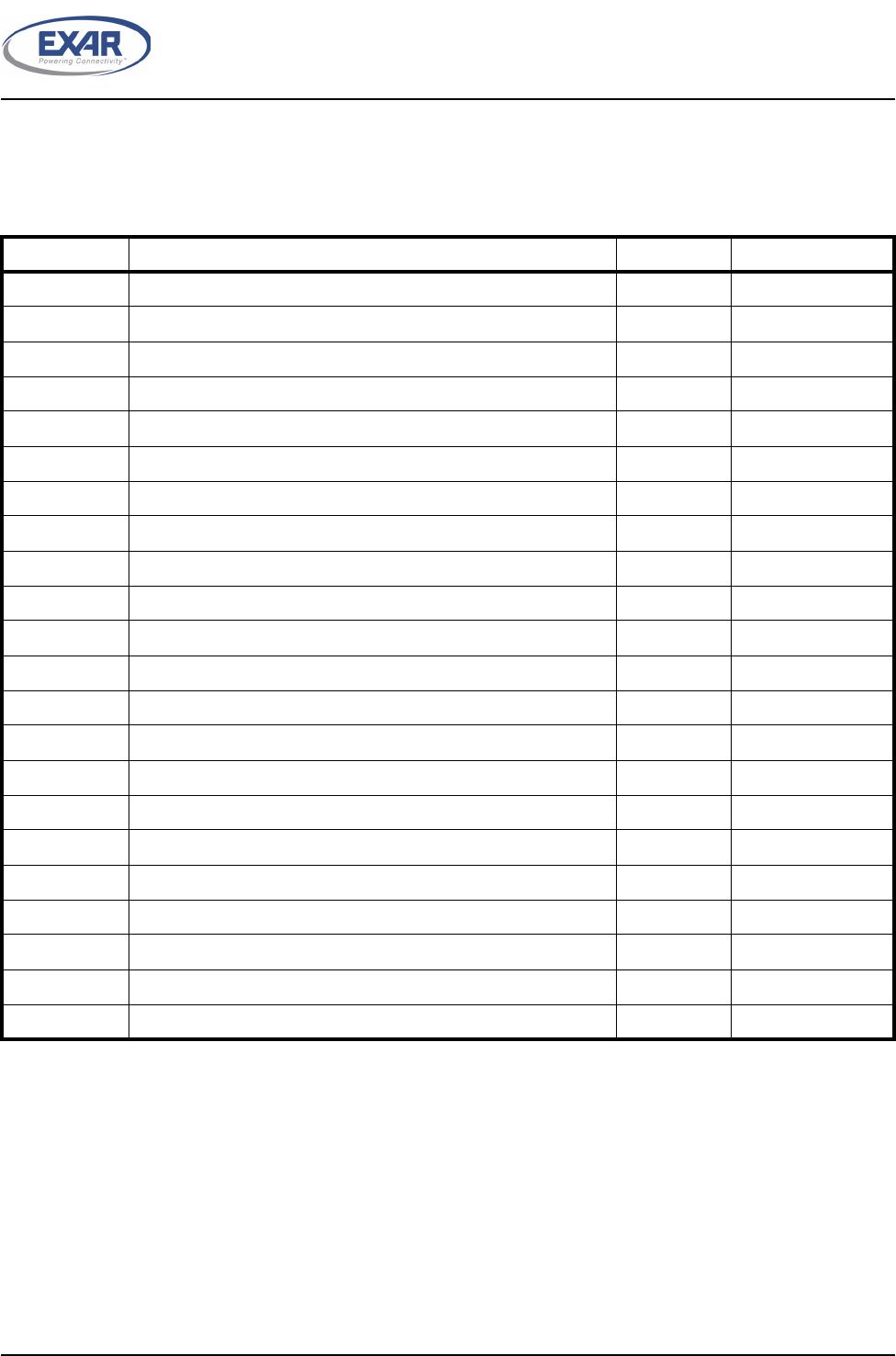

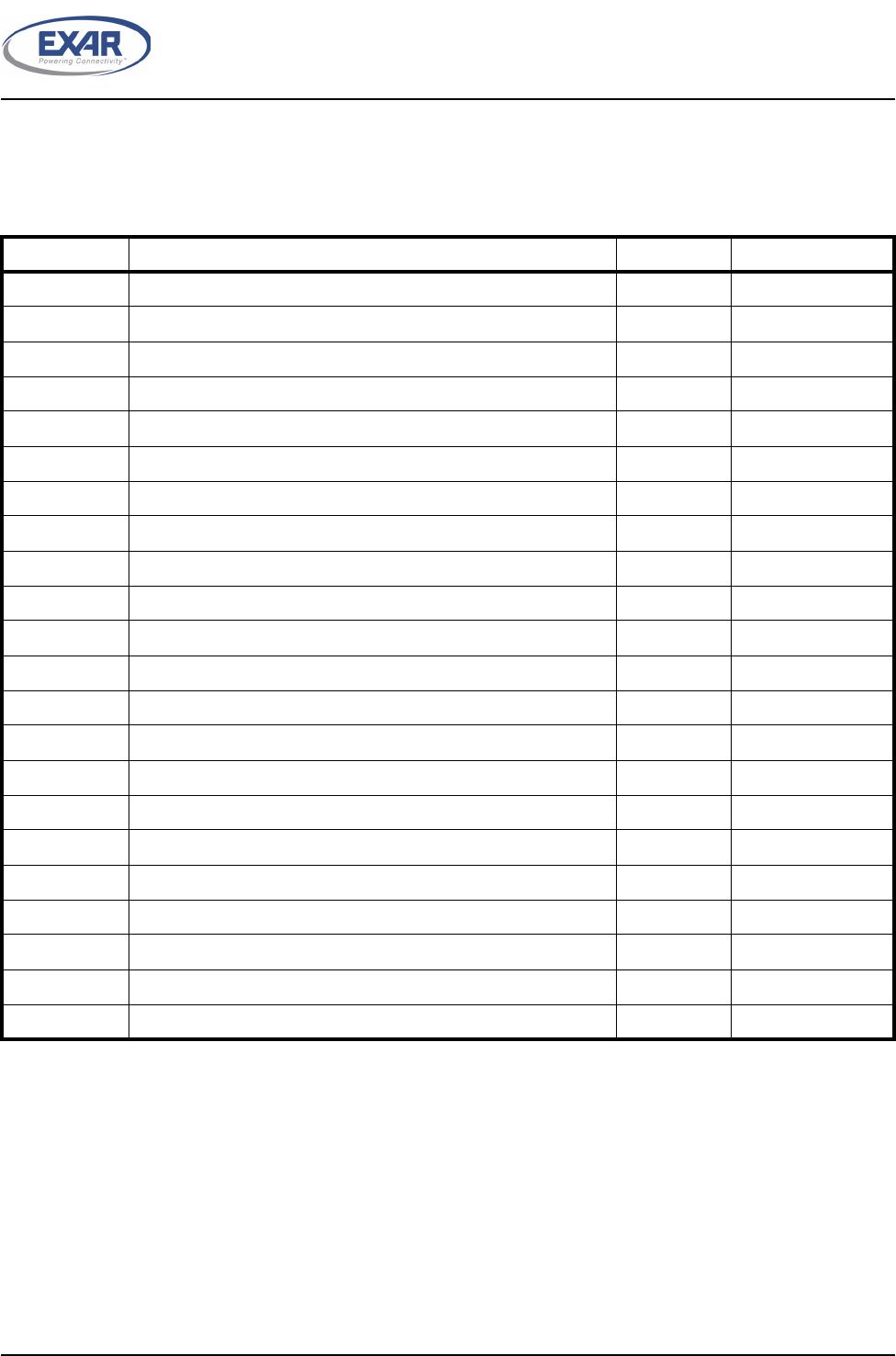

1.1.1 SPI Command Byte

An SPI command byte is sent by the SPI master following the slave address. The command byte indicates the

address offset of the register that will be accessed.

Table 2 below lists the command bytes for each register.

TABLE 2: COMMAND BYTE (REGISTER ADDRESS)

COMMAND BYTE REGISTER NAME DESCRIPTION READ/WRITE DEFAULT VALUES

0x00 GSR1 - GPIO State for P0-P7 Read-Only 0xXX

0x01 GSR2 - GPIO State for P8-P15 Read-Only 0xXX

0x02 OCR1 - Output Control for P0-P7 Read/Write 0xFF

0x03 OCR2 - Output Control for P8-P15 Read/Write 0xFF

0x04 PIR1 - Input Polarity Inversion for P0-P7 Read/Write 0x00

0x05 PIR2 - Input Polarity Inversion for P8-P15 Read/Write 0x00

0x06 GCR1 - GPIO Configuration for P0-P7 Read/Write 0xFF

0x07 GCR2 - GPIO Configuration for P8-P15 Read/Write 0xFF

0x08 PUR1 - Input Internal Pull-up Resistor Enable/Disable for P0-P7 Read/Write 0x00

0x09 PUR2 - Input Internal Pull-up Resistor Enable/Disable for P8-P15 Read/Write 0x00

0x0A IER1 - Input Interrupt Enable for P0-P7 Read/Write 0x00

0x0B IER2 - Input Interrupt Enable for P8-P15 Read/Write 0x00

0x0C TSCR1 - Output Three-State Control for P0-P7 Read/Write 0x00

0x0D TSCR2 - Output Three-State Control for P8-P15 Read/Write 0x00

0x0E ISR1 - Input Interrupt Status for P0-P7 Read 0x00

0x0F ISR2 - Input Interrupt Status for P8-P15 Read 0x00

0x10 REIR1 - Input Rising Edge Interrupt Enable for P0-P7 Read/Write 0x00

0x11 REIR2 - Input Rising Edge Interrupt Enable for P8-P15 Read/Write 0x00

0x12 FEIR1 - Input Falling Edge Interrupt Enable for P0-P7 Read/Write 0x00

0x13 FEIR2 - Input Falling Edge Interrupt Enable for P8-P15 Read/Write 0x00

0x14 IFR1 - Input Filter Enable/Disable for P0-P7 Read/Write 0xFF

0x15 IFR2 - Input Filter Enable/Disable for P8-P15 Read/Write 0xFF