LTC2605/LTC2615/LTC2625

12

2605fa

OPERATION

When the master has fi nished communicating with the

slave, it issues a STOP condition. A STOP condition is

generated by transitioning SDA from low to high while

SCL is high. The bus is then free for communication with

another I

2

C device.

Acknowledge

The Acknowledge signal is used for handshaking between

the master and the slave. An Acknowledge (active LOW)

generated by the slave lets the master know that the lat-

est byte of information was received. The Acknowledge

related clock pulse is generated by the master. The master

releases the SDA line (HIGH) during the Acknowledge

clock pulse. The slave-receiver must pull down the SDA

during the Acknowledge clock pulse so that it remains a

stable LOW during the HIGH period of this clock pulse.

The LTC2605/LTC2615/LTC2625 respond to a write by a

master in this manner. The LTC2605/LTC2615/LTC2625 do

not acknowledge a read (it retains SDA HIGH during the

period of the Acknowledge clock pulse).

Chip Address

The state of CA0, CA1 and CA2 decides the slave address

of the part. The pins CA0, CA1 and CA2 can be each set to

any one of three states: V

CC

, GND or FLOAT. This results

in 27 selectable addresses for the part. The addresses

corresponding to the states of CA0, CA1 and CA2 and the

global address are shown in Table 2.

In addition to the address selected by the address pins,

the parts also respond to a global address. This address

allows a common write to all LTC2605, LTC2615 and

LTC2625 parts to be accomplished with one 3-byte write

transaction on the I

2

C bus. The global address is a 7-bit

hard-wired address and is not selectable by CA0, CA1 and

CA2. The maximum capacitive load allowed on the address

pins (CA0, CA1 and CA2) is 10pF.

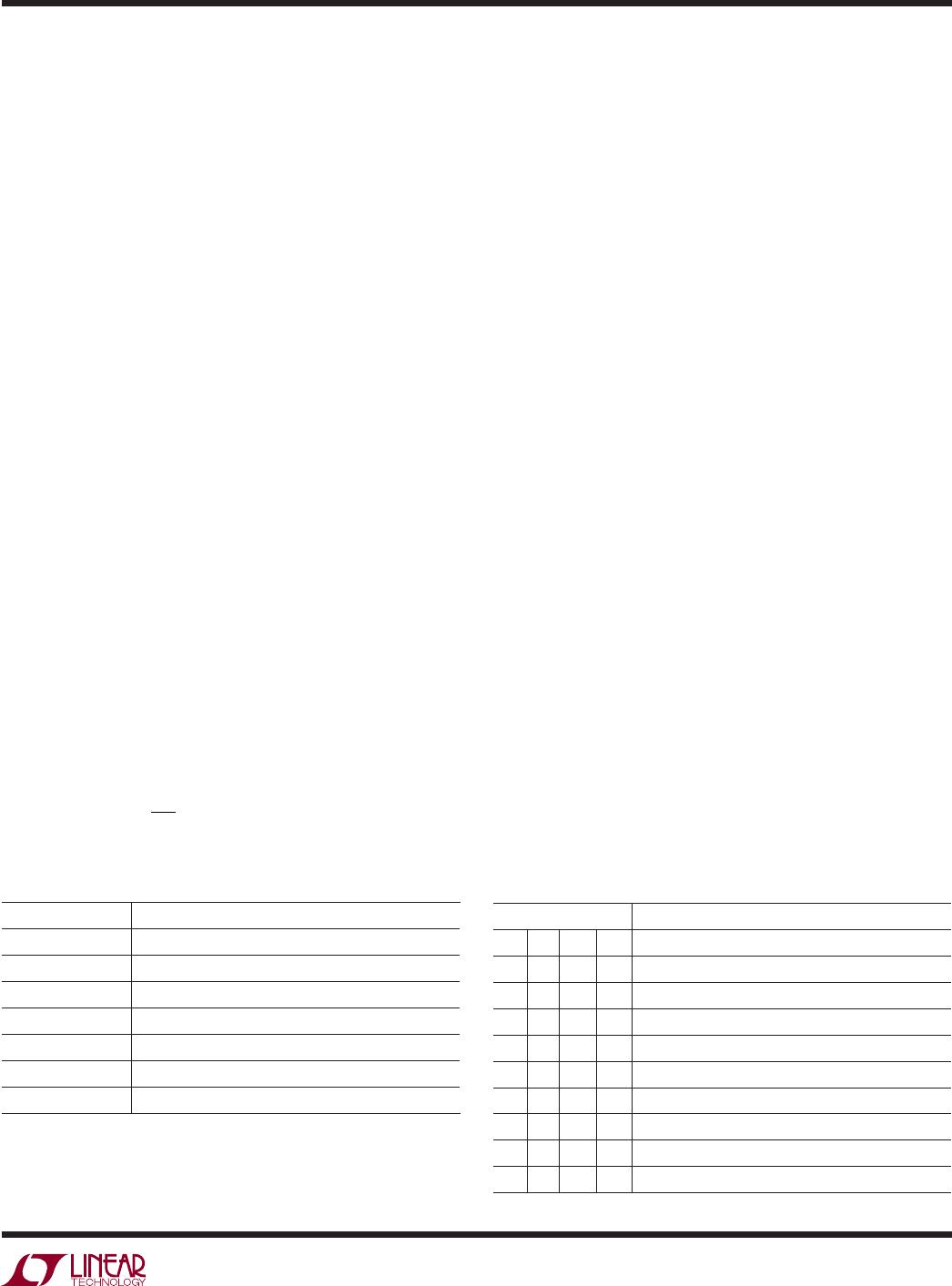

Write Word Protocol

The master initiates communication with the LTC2605/

LTC2615/LTC2625 with a START condition and a 7-bit slave

address followed by the Write bit (W) = 0. The LTC2605/

LTC2615/LTC2625 acknowledges by pulling the SDA pin

Table 2. Slave Address Map

CA2 CA1 CA0 SA6 SA5 SA4 SA3 SA2 SA1 SA0

GND GND GND 0 0 1 0 0 0 0

GNDGNDFLOAT0010001

GND GND V

CC

0010010

GNDFLOATGND0010011

GNDFLOATFLOAT0100000

GNDFLOATVCC0100001

GND V

CC

GND0100010

GND V

CC

FLOAT0100011

GND V

CC

V

CC

0110000

FLOATGNDGND0110001

FLOATGNDFLOAT0110010

FLOAT GND V

CC

0110011

FLOATFLOATGND1000000

FLOAT FLOAT FLOAT 1 0 0 0 0 0 1

FLOAT FLOAT V

CC

1000010

FLOAT V

CC

GND1000011

FLOAT V

CC

FLOAT1010000

FLOAT V

CC

V

CC

1010001

V

CC

GNDGND1010010

V

CC

GNDFLOAT1010011

V

CC

GND V

CC

1100000

V

CC

FLOATGND1100001

V

CC

FLOATFLOAT1100010

V

CC

FLOAT V

CC

1100011

V

CC

V

CC

GND1110000

V

CC

V

CC

FLOAT1110001

V

CC

V

CC

V

CC

1110010

GLOBAL ADDRESS 1 1 1 0 0 1 1

low at the 9th clock if the 7-bit slave address matches the

address of the parts (set by CA0, CA1 and CA2) or the

global address. The master then transmits three bytes of

data. The LTC2605/LTC2615/LTC2625 acknowledges each

byte of data by pulling the SDA line low at the 9th clock of

each data byte transmission. After receiving three complete

bytes of data, the LTC2605/LTC2615/LTC2625 executes the

command specifi ed in the 24-bit input word.

If more than three data bytes are transmitted after a valid

7-bit slave address, the LTC2605/LTC2615/LTC2625 do not

acknowledge the extra bytes of data (SDA is high during

the 9th clock).