LT1054/LT1054L

8

1054lfh

For more information www.linear.com/LT1054

applications inFormation

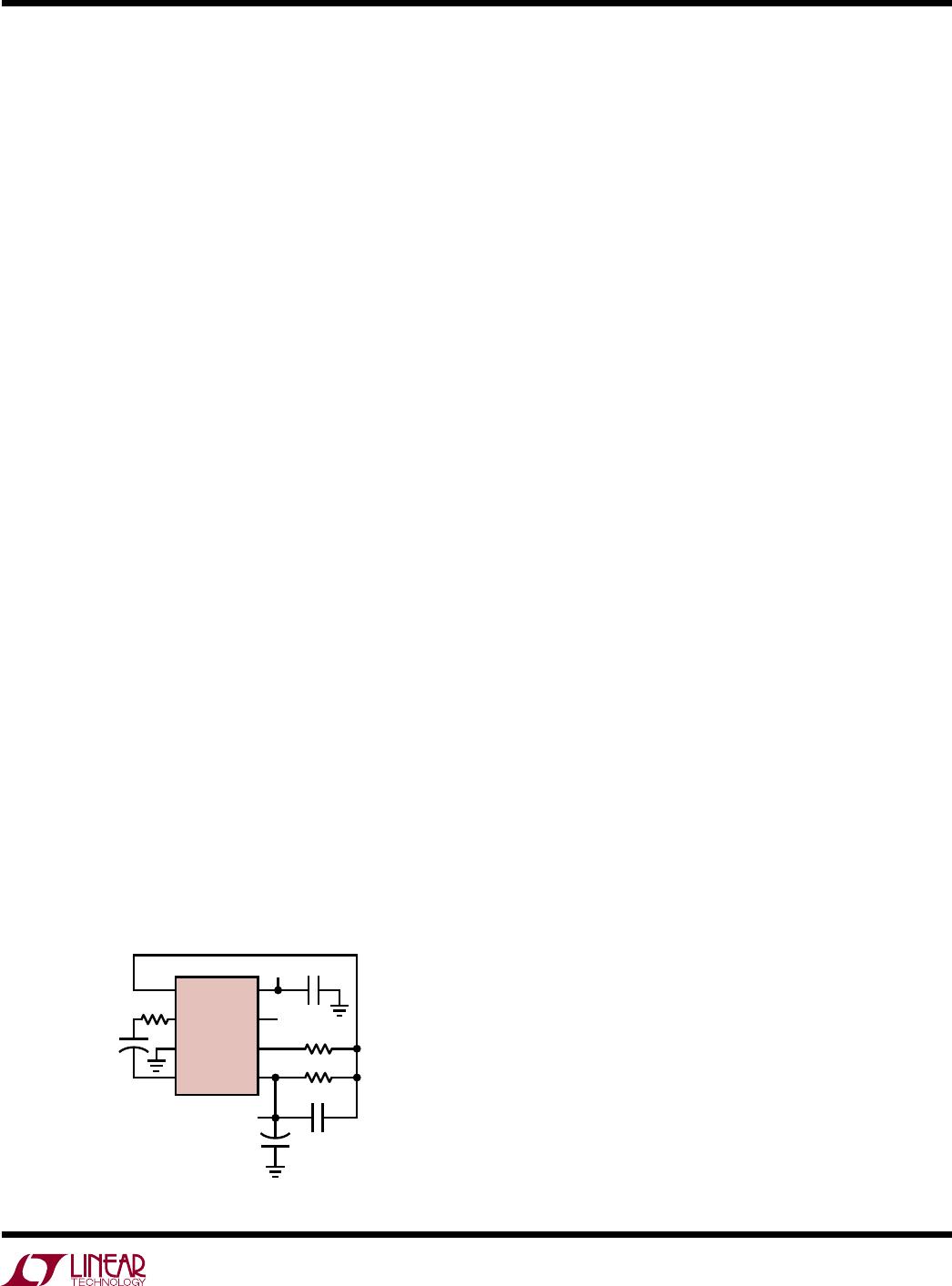

R4

RESTART SHUTDOWN

C1

R2

C

IN

10µF

TANTALUM

C

OUT

100µF

TANTALUM

V

OUT

LT1054 • F05

V

IN

R1

2.2µF

R3

= ≈+ 1

WHERE V

REF

= 2.5V NOMINAL

*CHOOSE THE CLOSEST 1% VALUE

FOR EXAMPLE: TO GET V

OUT

= –5V REFERRED TO THE GROUND

PIN OF THE LT1054, CHOOSE R1 = 20k, THEN

|V

OUT

|

)

)

V

REF

2

– 40mV

= 102.6k*

+ 1

|–5V|

)

)

2.5V

2

– 40mV

)

)

+ 1

|V

OUT

|

1.21V

LT1054

FB/SHDN

CAP

+

GND

CAP

–

V

+

OSC

V

REF

V

OUT

+

+

+

be 20k or greater because the reference output current

is limited to ≈100µA. R2 should be chosen to be in the

range of 100k to 300k. For optimum results the ratio of

C

IN

/C

OUT

is recommended to be 1/10. C1, required for

good load regulation at light load currents, should be

0.002µF for all output voltages.

A new die layout was required to fit into the physical

dimensions of the S8 package. Although the new die

of the LT1054CS8 will meet all the specifications of the

existing LT1054 data sheet, subtle differences in the

layout of the new die require consideration in some ap

-

plication circuits. In regulating mode circuits using the

1054CS8 the nominal values of the capacitors, C

IN

and

C

OUT

, must be approximately equal for proper operation

at elevated junction temperatures. This is different from

the earlier part. Mismatches within normal production

tolerances for the capacitors are acceptable. Making the

nominal capacitor values equal will ensure proper opera

-

tion at elevated junction temperatures at the cost of a

small degradation in the transient response of regulator

cir

cuits. For unregulated cir

cuits the values of C

IN

and

C

OUT

are normally equal for all packages. For S8 applica-

tions assistance in unusual applications circuits, please

consult the factory

.

It can be seen from the circuit block diagram that the

maximum regulated output voltage is limited by the supply

voltage. For the basic configuration,

|V

OUT

| referred to the

ground pin of the LT1054 must be less than the total of the

supply voltage minus the voltage loss due to the switches.

The voltage loss versus output current due to the switches

can be found in Typical Performance Characteristics. Other

configurations such as the negative doubler can provide

higher output voltages at reduced output currents (see

Typical Applications).

Capacitor Selection

For unregulated circuits the nominal values of C

IN

and C

OUT

should be equal. For regulated circuits see the section on

Regulation. While the exact values of C

IN

and C

OUT

are

noncritical, good quality, low ESR capacitors such as solid

tantalum are necessary to minimize voltage losses at high

currents. For C

IN

the effect of the ESR of the capacitor will

be multiplied by four due to the fact that switch currents

are approximately two times higher than output current and

losses will occur on both the charge and discharge cycle.

This means that using a capacitor with 1Ω of ESR for C

IN

will have the same effect as increasing the output imped-

ance of the LT1054 by 4Ω. This represents a significant

increase in the voltage losses. For C

OUT

the affect of ESR is

less dramatic. C

OUT

is alternately charged and discharged

at a current approximately equal to the output current and

the ESR of the capacitor will cause a step function to oc

-

cur in the output ripple at the switch transitions. This step

function will degrade the output regulation for changes

in output load current and should be avoided. Realizing

that large value tantalum capacitors can be expensive, a

technique that can be used is to parallel a smaller tantalum

capacitor with a large aluminum electrolytic capacitor to

gain both low ESR and reasonable cost. Where physical

size is a concern some of the newer chip type surface

mount tantalum capacitors can be used. These capacitors

are normally rated at working voltages in the 10V to 20V

range and exhibit very low ESR (in the range of 0.1Ω).

Output Ripple

The peak-to-peak output ripple is determined by the value

of the output capacitor and the output current. Peak-to-

peak output ripple may be approximated by the formula:

dV =

OUT

2fC

OUT

Figure 5