OP249 Data Sheet

Rev. I | Page 14 of 18

10

0%

100

90

50mV

1µs

00296-042

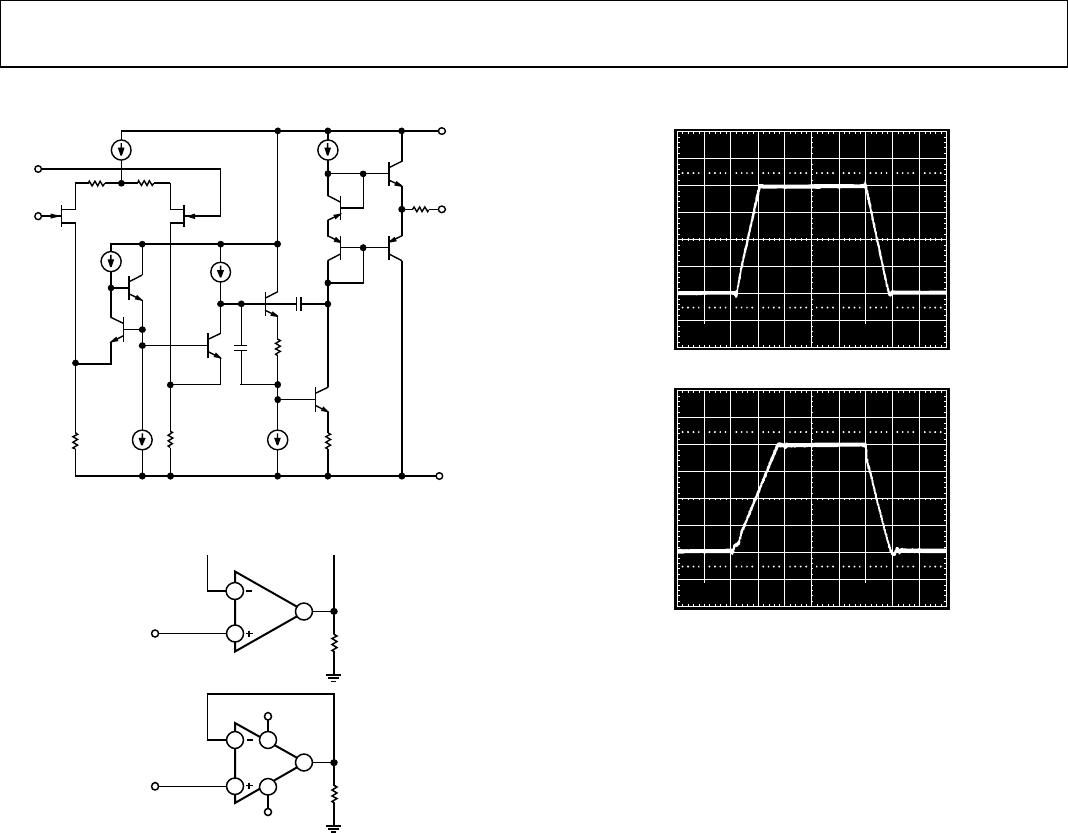

Figure 42. Small-Signal Transient Response,

A

V

= 1, Z

L

= 2 kΩ||100 pF, No Compensation, V

S

= ±15 V

As with most JFET input amplifiers, the output of the OP249

can undergo phase inversion if either input exceeds the specified

input voltage range. Phase inversion does not damage the

amplifier, nor does it cause an internal latch-up condition.

Supply decoupling should be used to overcome inductance and

resistance associated with supply lines to the amplifier. A 0.1 µF

and a 10 µF capacitor should be placed between each supply pin

and ground.

OPEN-LOOP GAIN LINEARITY

The OP249 has both an extremely high open-loop gain of

1 kV/mV minimum and constant gain linearity, which enhances its

dc precision and provides superb accuracy in high closed-loop

gain applications. Figure 43 illustrates the typical open-loop

gain linearity—high gain accuracy is assured, even when

driving a 600 Ω load.

OFFSET VOLTAGE ADJUSTMENT

The inherent low offset voltage of the OP249 makes offset

adjustments unnecessary in most applications. However, where

a lower offset error is required, balancing can be performed

with simple external circuitry, as shown in Figure 44 and Figure 45.

HORIZONTAL 5V/DIV

OUTPUT CHARGE

VERTICAL 50µV/DIV

INPUT VARIATION

00296-043

Figure 43. Open-Loop Gain Linearity; Variation in Open-Loop Gain Results in

Errors in High Closed-Loop Gain Circuits; R

L

= 600 Ω, V

S

= ±15 V

+V

R3

R4

R2

R1

V

OS

ADJUST RANGE = ±V

V

OUT

V

IN

–V

1/2

OP249

R2

31Ω

R5

50kΩ

R1

200kΩ

00296-044

Figure 44. Offset Adjustment for Inverting Amplifier Configuration

+V

R5

V

OS

ADJUST RANGE = ±V

R2

R1

1 +

R5

R4

IF R2 << R4

R5

R4 + R2

R4

V

OUT

–V

V

IN

R3

50kΩ

R2

33Ω

R1

200kΩ

1/2

OP249

GAIN =

= 1 +

V

OUT

V

IN

=

00296-045

Figure 45. Offset Adjustment for Noninverting Amplifier Configuration

In Figure 44, the offset adjustment is made by supplying a small

voltage at the noninverting input of the amplifier. Resistors R1

and R2 attenuate the potentiometer voltage, providing a ±2.5 mV

(with V

S

= ±15 V) adjustment range, referred to the input.

Figure 45 shows the offset adjustment for the noninverting

amplifier configuration, also providing a ±2.5 mV adjustment

range. As shown in the equations in Figure 45, if R4 is not much

greater than R2, a resulting closed-loop gain error must be

accounted for.

SETTLING TIME

The settling time is the time between when the input signal begins

to change and when the output permanently enters a prescribed

error band. The error bands on the output are 5 mV and 0.5 m V,

respectively, for 0.1% and 0.01% accuracy.

Figure 46 shows the settling time of the OP249, which is typically

870 ns. Moreover, problems in settling response, such as thermal

tails and long-term ringing, are nonexistent.

10

0%

100

90

500ns10mV

870ns

00296-046

Figure 46. Settling Characteristics of the OP249 to 0.01%