Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774 1

Rev. G

06/02/2014

Copyright © 2014 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without

notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest

version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reason-

ably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications

unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

IS61WV102416ALL

IS61WV102416BLL

IS64WV102416BLL

1M x 16 HIGH-SPEED ASYNCHRONOUS

CMOS STATIC RAM WITH 3.3V SUPPLY

JUNE 2014

FEATURES

• High-speedaccesstimes:

8, 10, 20 ns

• High-performance,low-powerCMOSprocess

• Multiplecenterpowerandgroundpinsforgreater

noise immunity

• EasymemoryexpansionwithCE and OE op-

tions

• CE power-down

• Fullystaticoperation:noclockorrefresh

required

• TTLcompatibleinputsandoutputs

• Singlepowersupply

V

dd1.65Vto2.2V(IS61WV102416ALL)

speed = 20ns for V

dd 1.65V to 2.2V

V

dd2.4Vto3.6V(IS61/64WV102416BLL)

speed = 10ns for V

dd 2.4V to 3.6V

speed = 8ns for V

dd 3.3V + 5%

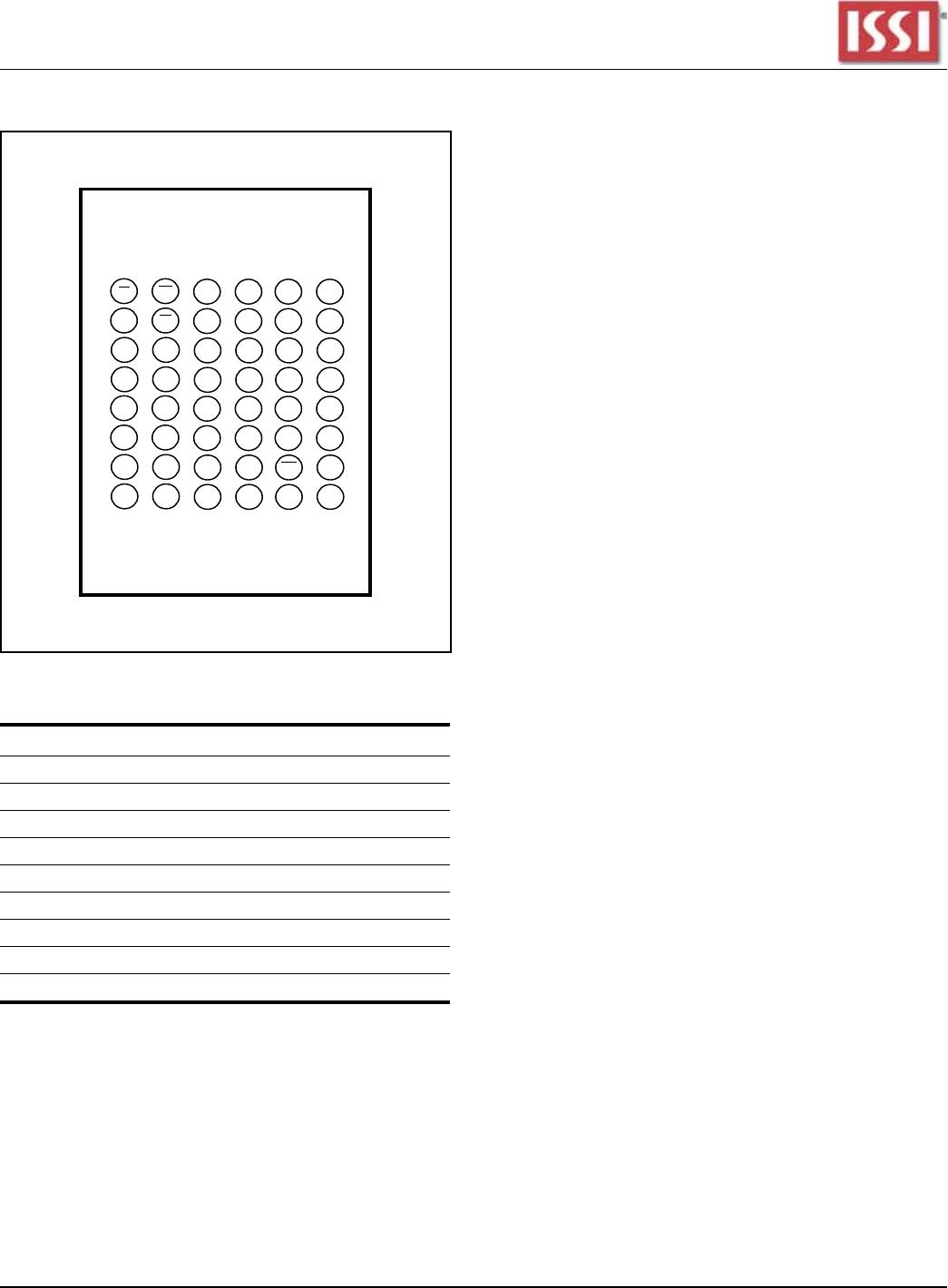

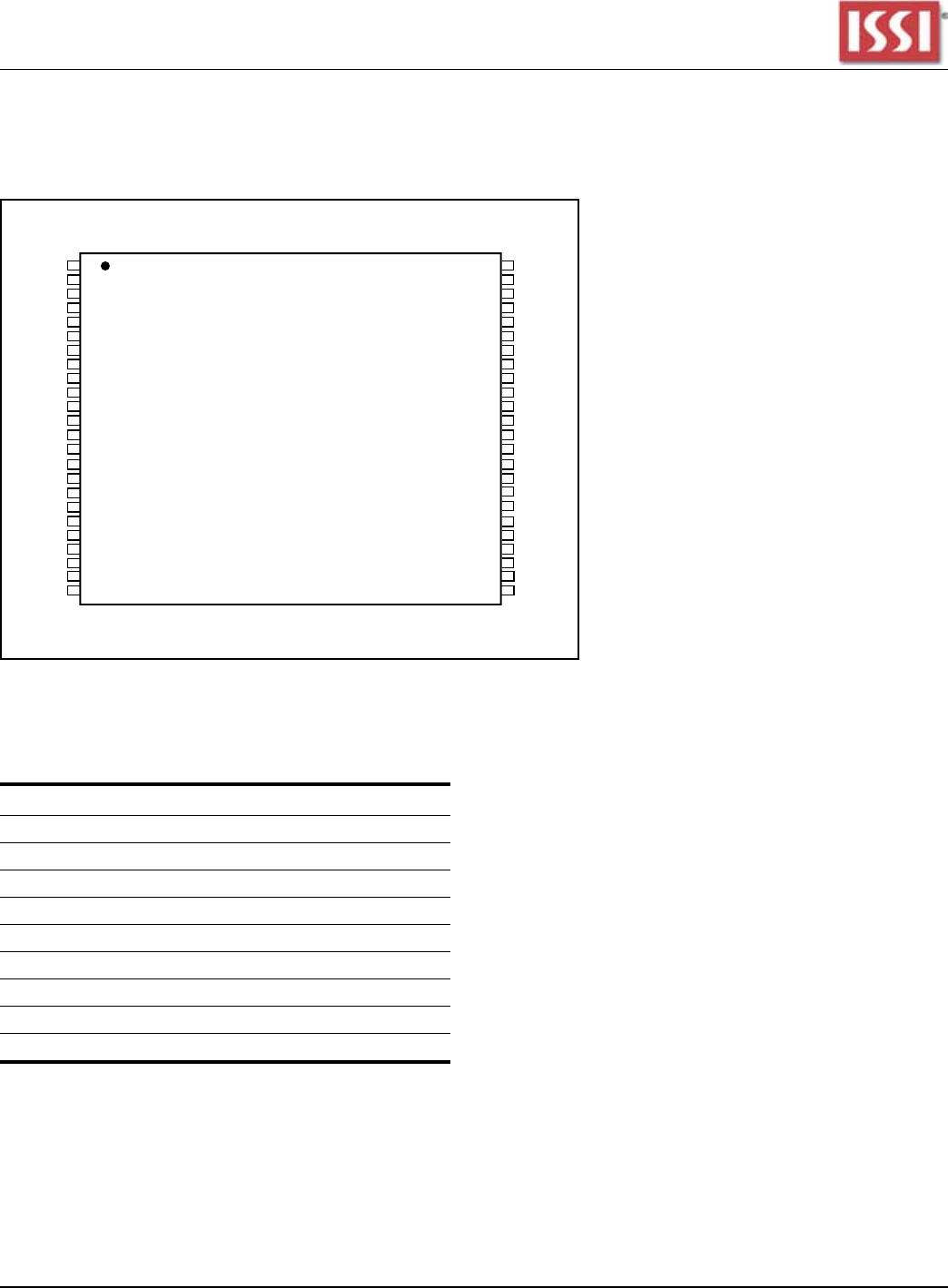

• Packagesavailable:

–

48-ball miniBGA (9mm x 11mm)

–48-pinTSOP(TypeI)

• IndustrialandAutomotiveTemperatureSupport

• Lead-freeavailable

• Datacontrolforupperandlowerbytes

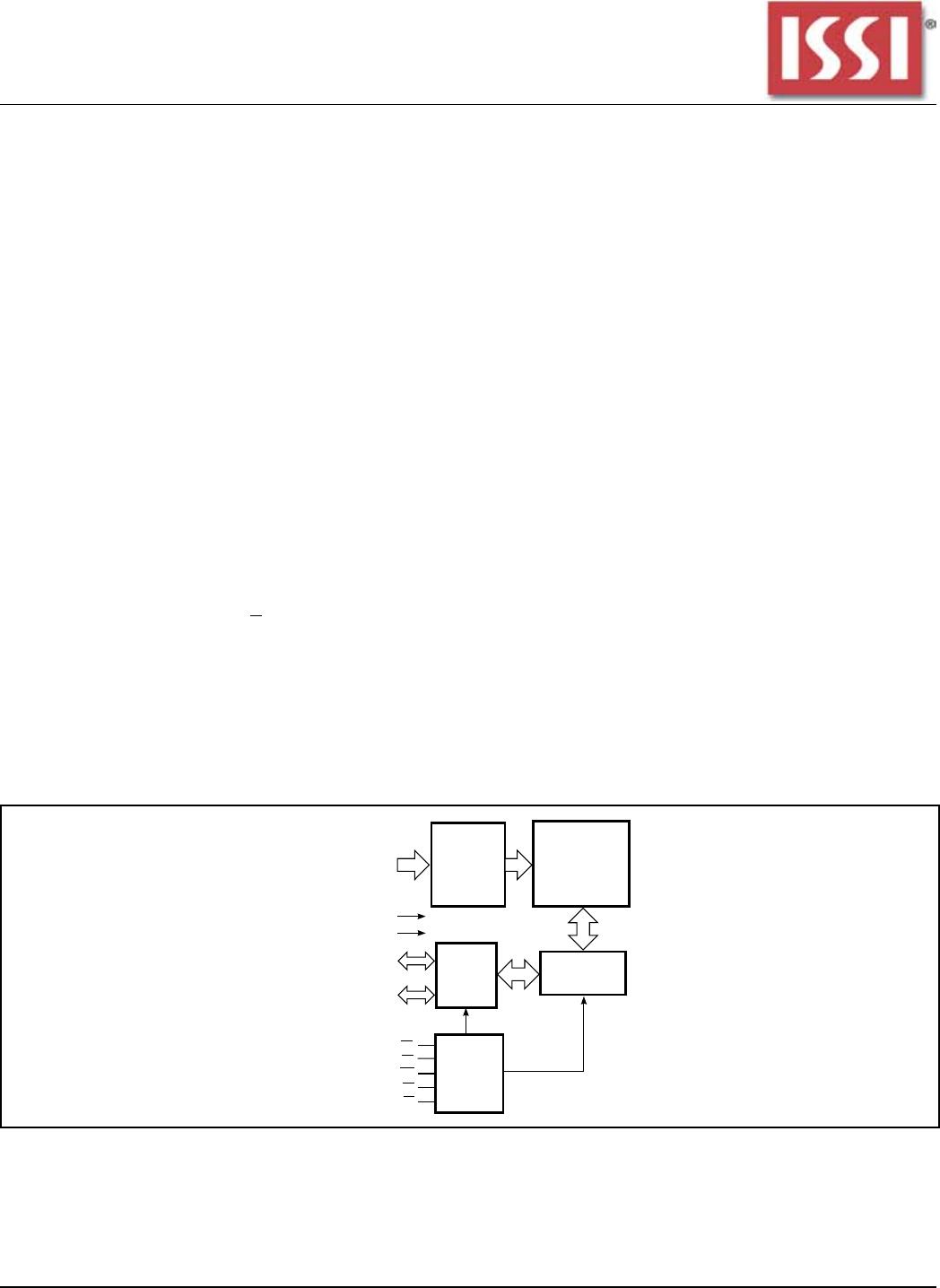

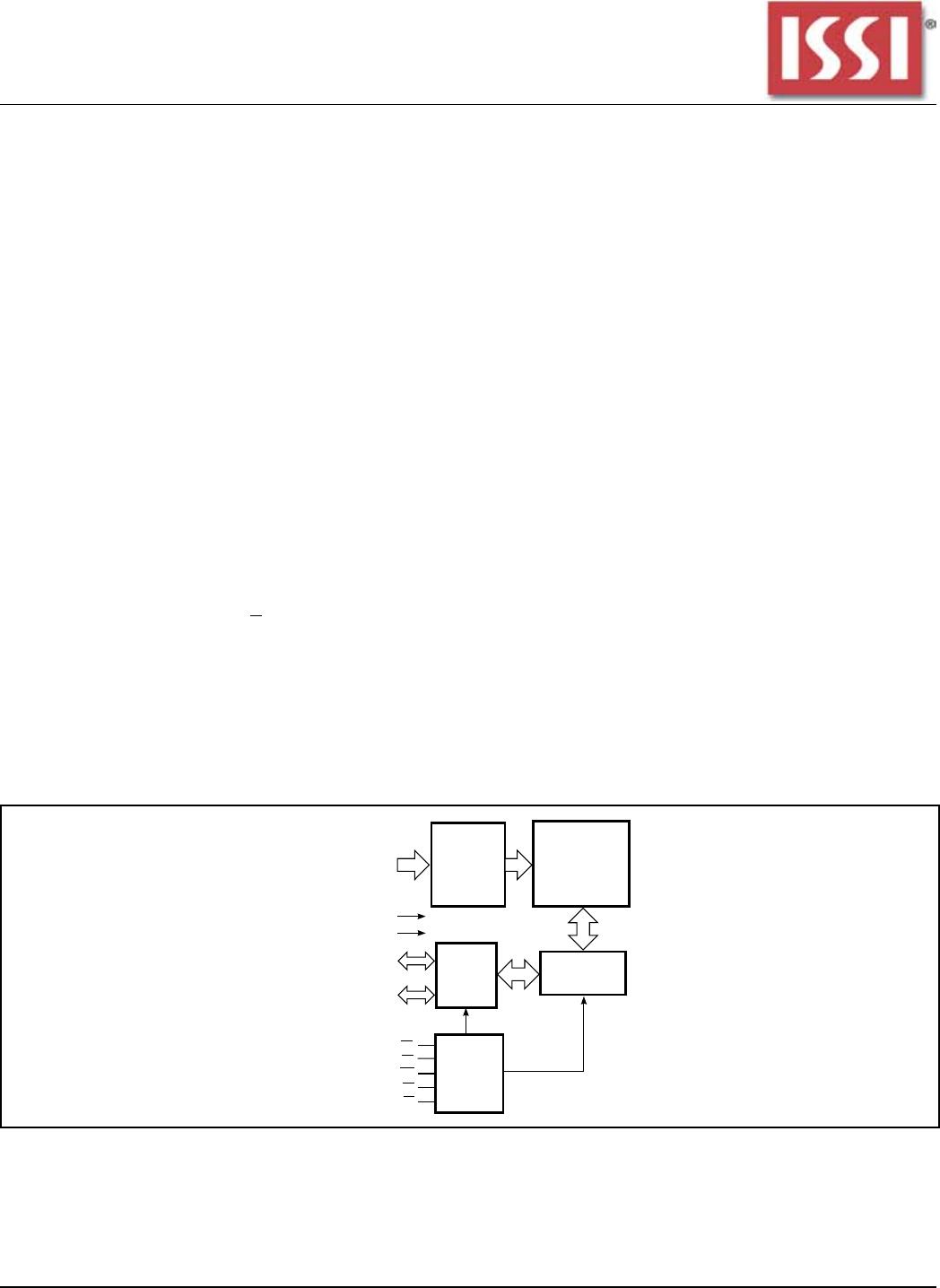

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION

TheISSIIS61WV102416ALL/BLLandIS64WV102416BLL

arehigh-speed,16M-bitstaticRAMsorganizedas1024K

words by 16 bits. It is fabricated using ISSI's high-perfor-

mance CMOS technology. This highly reliable process

coupled with innovative circuit design techniques, yields

high-performance and low power consumption devices.

When CE is HIGH (deselected), the device assumes a

standby mode at which the power dissipation can be re-

duceddownwithCMOSinputlevels.

EasymemoryexpansionisprovidedbyusingChipEnable

andOutputEnableinputs,CE and OE.TheactiveLOW

WriteEnable(WE) controls both writing and reading of the

memory. A data byte allows Upper Byte (UB)andLower

Byte (LB) access.

The device is packagedin the JEDEC standard 48-pin

TSOPTypeIand48-pinMiniBGA(9mmx11mm).

A0-A19

CE

OE

WE

1024K x 16

MEMORY ARRAY

DECODER

COLUMN I/O

CONTROL

CIRCUIT

GND

VDD

I/O

DATA

CIRCUIT

I/O0-I/O7

Lower Byte

I/O8-I/O15

Upper Byte

UB

LB