ESD7361, SZESD7361

www.onsemi.com

5

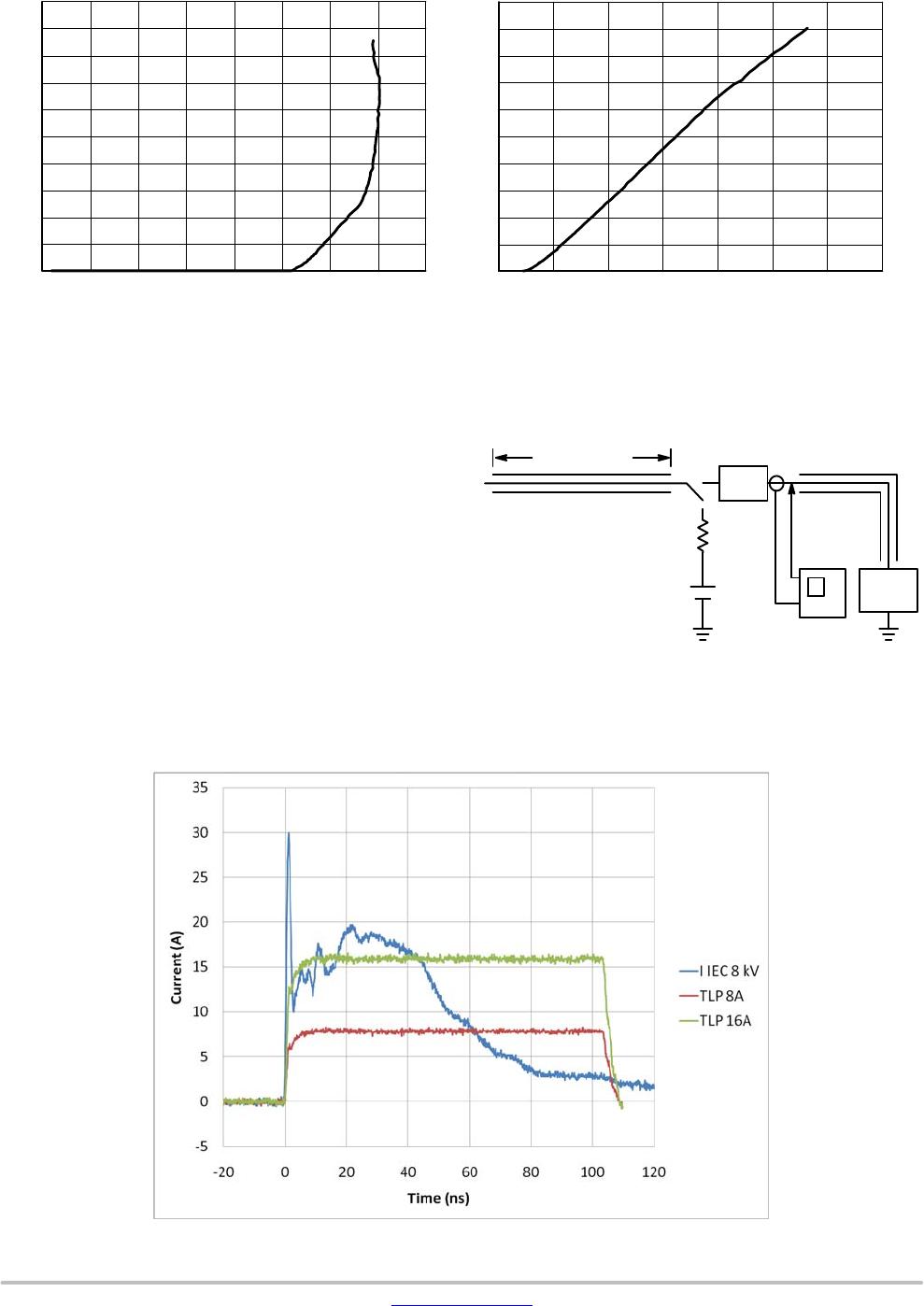

Figure 11. Positive TLP I−V Curve

Figure 12. Negative TLP I−V Curve

TLP CURRENT (A)

V

C

, VOLTAGE (V)

25

040353051015 2520

TLP CURRENT (A)

V

C

, VOLTAGE (V)

−25

0 −14−12−10−2 −4 −6 −8

NOTE: TLP parameter: Z

0

= 50 W, t

p

= 100 ns, t

r

= 300 ps, averaging window: t

1

= 30 ns to t

2

= 60 ns. V

IEC

is the equivalent voltage

stress level calculated at the secondary peak of the IEC 61000−4−2 waveform at t = 30 ns with 2 A/kV. See TLP description

below for more information.

20

15

10

5

0

−20

−15

−10

−5

0

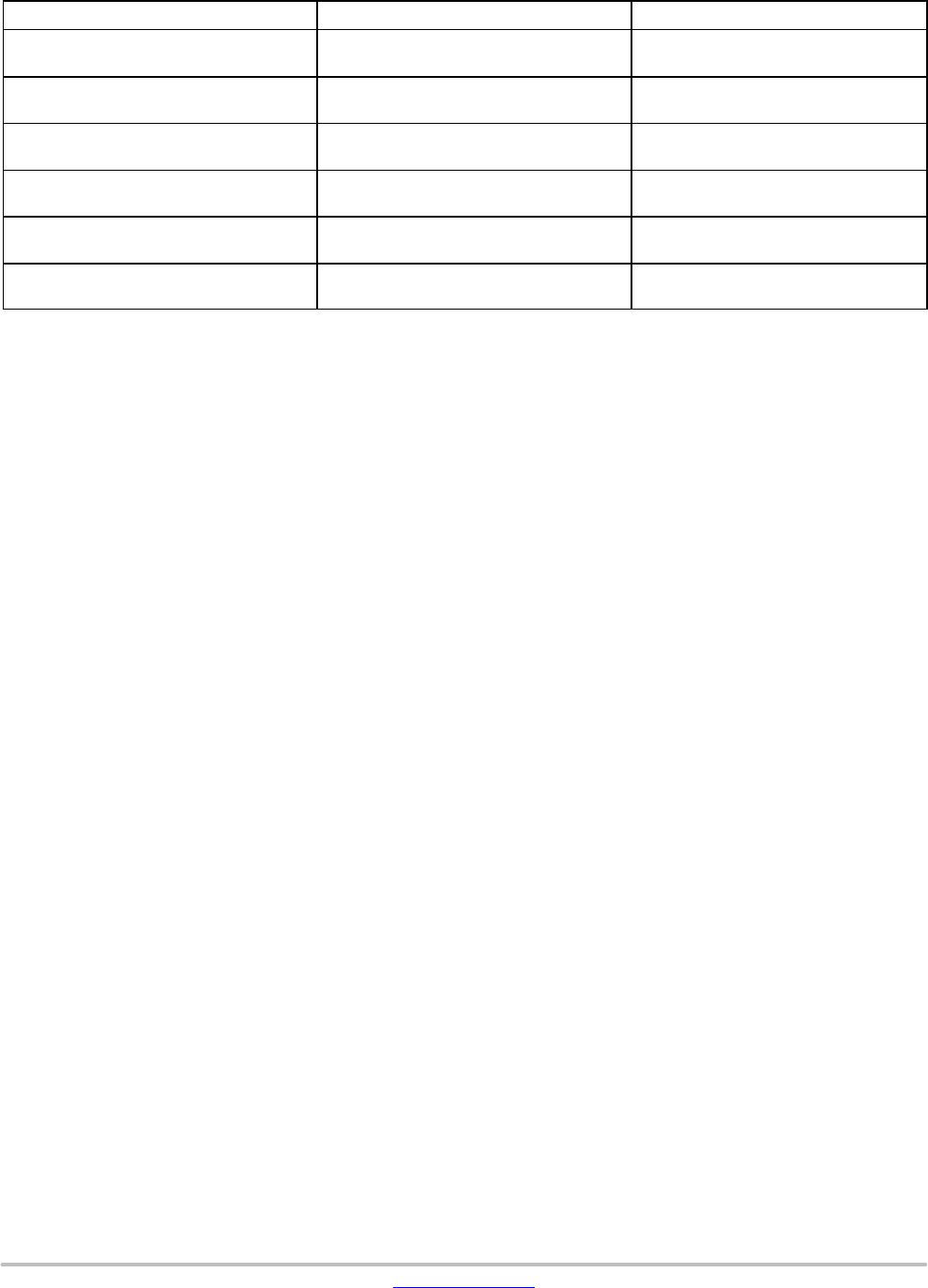

Transmission Line Pulse (TLP) Measurement

Transmission Line Pulse (TLP) provides current versus

voltage (I−V) curves in which each data point is obtained

from a 100 ns long rectangular pulse from a charged

transmission line. A simplified schematic of a typical TLP

system is shown in Figure 13. TLP I−V curves of ESD

protection devices accurately demonstrate the product’s

ESD capability because the 10s of amps current levels and

under 100 ns time scale match those of an ESD event. This

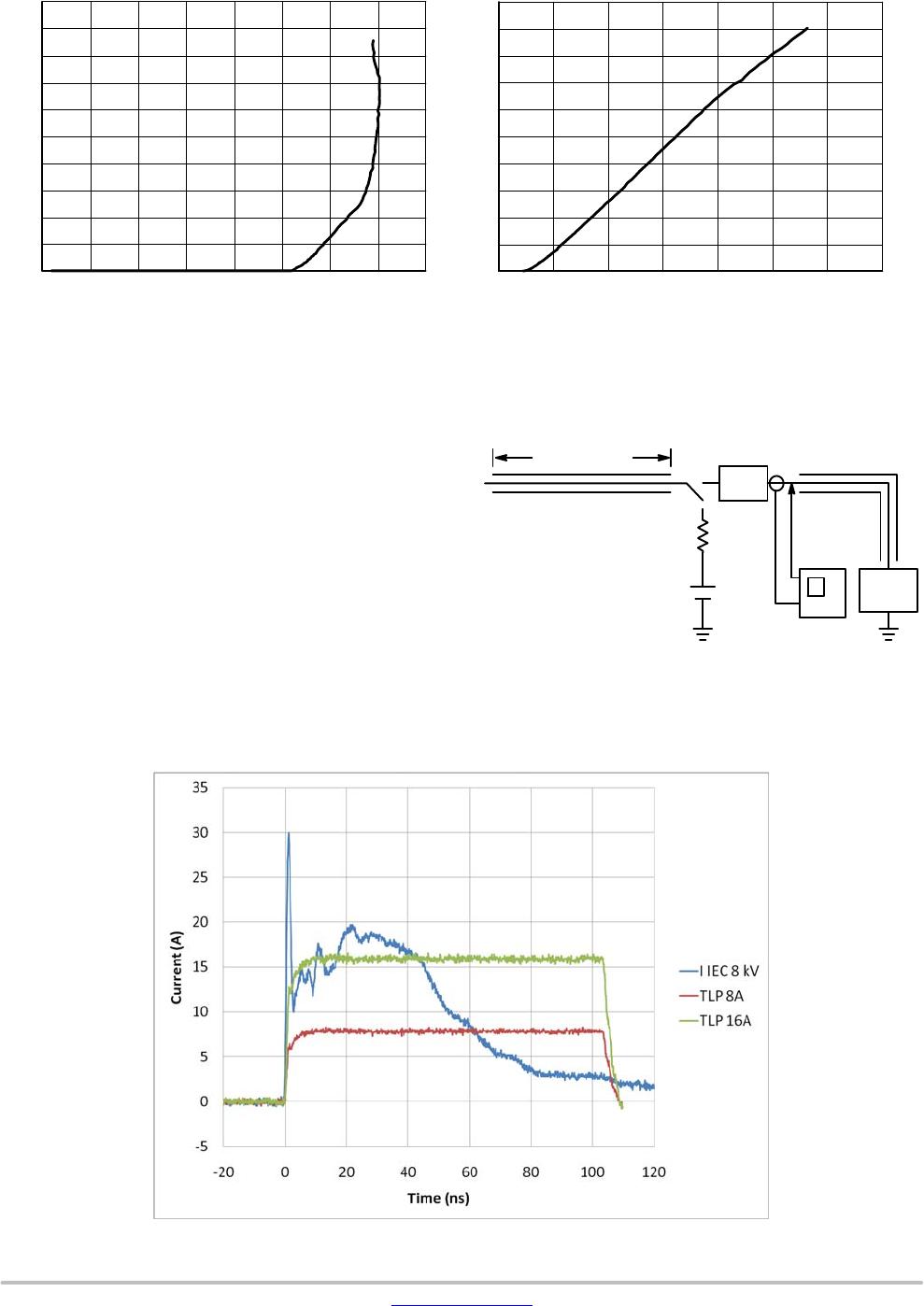

is illustrated in Figure 14 where an 8 kV IEC 61000−4−2

current waveform is compared with TLP current pulses at

8 A and 16 A. A TLP I−V curve shows the voltage at which

the device turns on as well as how well the device clamps

voltage over a range of current levels.

Figure 13. Simplified Schematic of a Typical TLP

System

DUT

L

S

÷

Oscilloscope

Attenuator

10 MW

V

C

V

M

I

M

50 W Coax

Cable

50 W Coax

Cable

Figure 14. Comparison Between 8 kV IEC 61000−4−2 and 8 A and 16 A TLP Waveforms