REV. E–16–

AD7701

Asynchronous Communications (AC) Mode

The AC mode (MODE pin tied to –5 V) offers a UART com-

patible interface that allows the AD7701 to transmit data

asynchronously from remote locations. An external SCLK sets

the baud rate and data is transmitted in two bytes in UART

compatible format. Using the AC mode, the AD7701 can be

interfaced directly to microprocessors with UART interfaces,

such as the 8051 and TMS70X2.

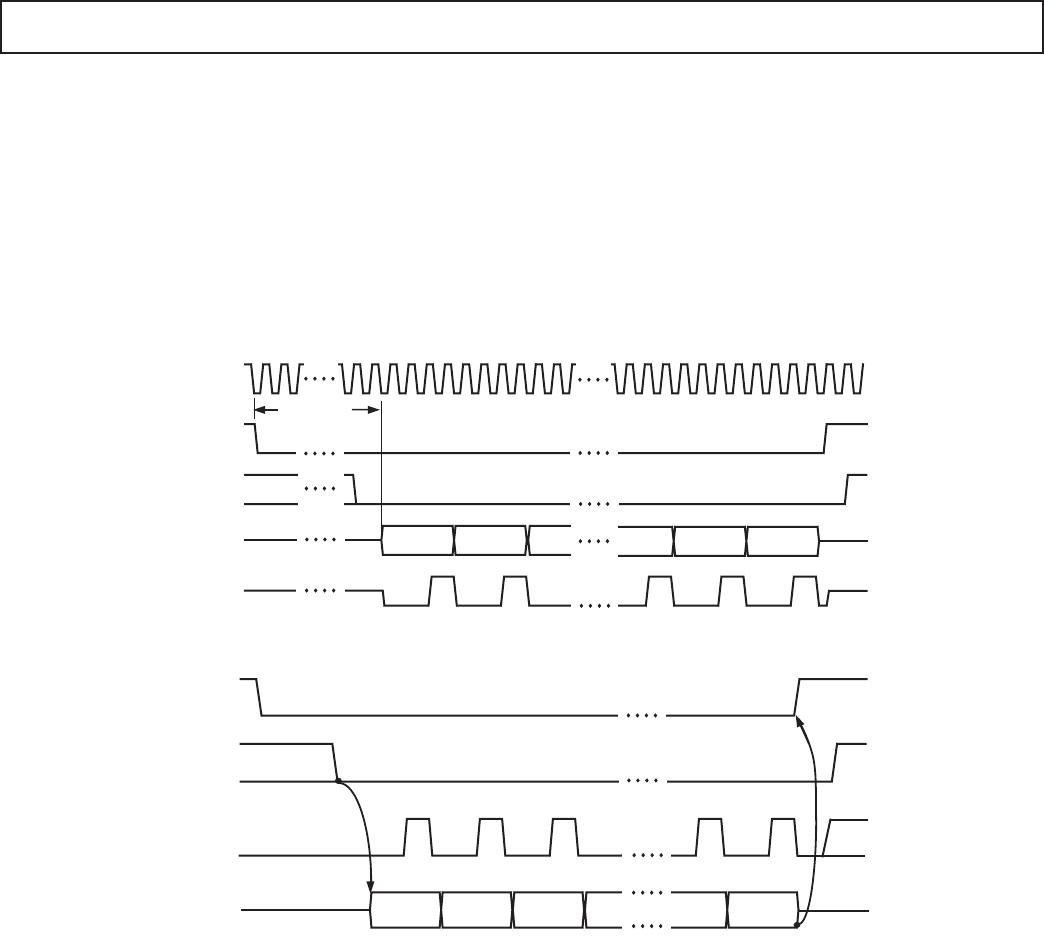

Data transmission is initiated by CS going low. If CS is low on a

falling edge of SCLK, the AD7701 begins transmitting an 8-bit

data byte (DB8 to DB15) with one start bit and two stop bits,

as in Figure 21. The SDATA output will then go three-state.

The second byte is transmitted by bringing CS low again and

DB0 to DB7 are transmitted in the same format as the first byte.

UART baud rates are typically low compared to the AD7701’s

4 kHz output update rate. If CS is low and data is still being

transmitted when a new data-word becomes available, the new

data will be ignored. However, if CS has been taken high between

bytes, when a new data-word becomes available, the AD7701

could update the output register before the second byte is trans-

mitted. In this case, the UART would receive the first byte of

the new word instead of the second byte of the old word. When

using the AC mode, care must obviously be taken to ensure that

this does not occur.

DIGITAL NOISE AND OUTPUT LOADING

As mentioned earlier, the AD7701 divides its internal timing

into two distinct phases, analog sampling and settling and digi-

tal computation. In the SSC mode, data is transmitted only

during the digital computation periods to minimize the effects

of digital noise on analog performance. In the SEC and AC

modes, data transmission is externally controlled, so this auto-

matic safeguard does not exist.

Whatever mode of operation is used, resistive and capacitive

loads on digital outputs should be minimized in order to reduce

crosstalk between analog and digital portions of the circuit. For

this reason, connection to low power CMOS logic such as one

of the 4000 series or 74C families is recommended.

It is especially important to minimize the load on SDATA in the

AC mode, as transmission in this mode is inherently asynchro-

nous. In the SEC mode, the AD7701 should be synchronized to

the digital system clock via CLKIN.

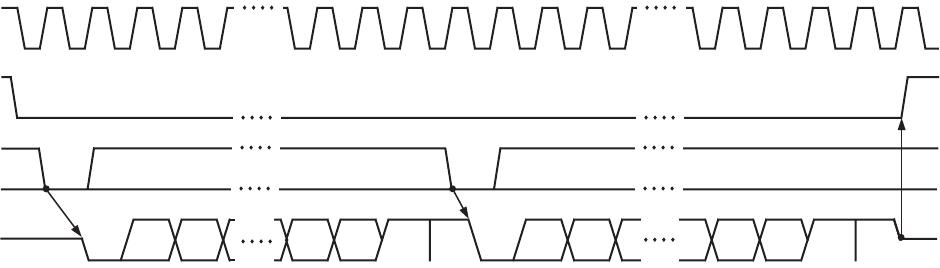

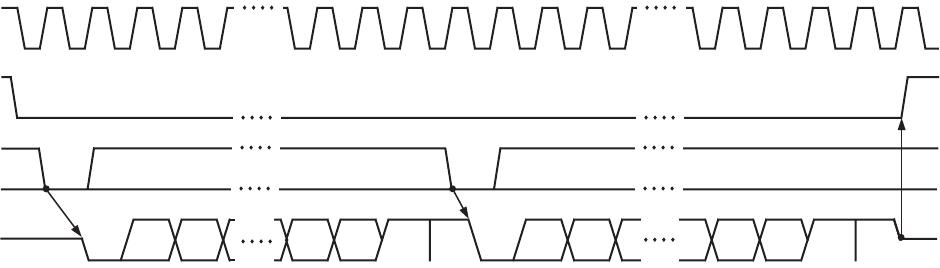

SCLK (I)

SDATA (O)

DB9

START

BIT

DB8

DB14 DB15

STOP

BIT

DB0 DB1

DB6

DB7

HI-Z

STOP

BIT

START

BIT

STOP

BIT

STOP

BIT

DRDY (O)

CS (I)

Figure 21. Timing Diagram for Asynchronous Communications Mode