7

3392F–CNFG–2/08

AT17F16

6. FPGA Master Serial Mode Summary

The I/O and logic functions of any SRAM-based FPGA are established by a configuration pro-

gram. The program is loaded either automatically upon power-up, or on command, depending

on the state of the FPGA mode pins. In Master mode, the FPGA automatically loads the config-

uration program from an external memory. The AT17F Serial Configuration PROM has been

designed for compatibility with the Master Serial mode.

This document discusses the Atmel AT40K, AT40KAL and AT94KAL applications as well as Xil-

inx applications.

7. Control of Configuration

Most connections between the FPGA device and the AT17F Serial Configurator PROM are sim-

ple and self-explanatory.

• The DATA output of the AT17F Series Configurator drives DIN of the FPGA devices.

• The master FPGA CCLK output drives the CLK input of the AT17F Series Configurator.

• The CEO

output of any AT17F Series Configurator drives the CE input of the next

Configurator in a cascade chain of configurator devices.

•SER_EN

must be connected to V

CC

or allowed to float to logic High via the internal pull-up

resistor (except during ISP).

• The READY pin is available as an open-collector indicator of the device’s reset status; it is

driven Low while the device is in its power-on reset cycle and released (tri-stated) when the

cycle is complete.

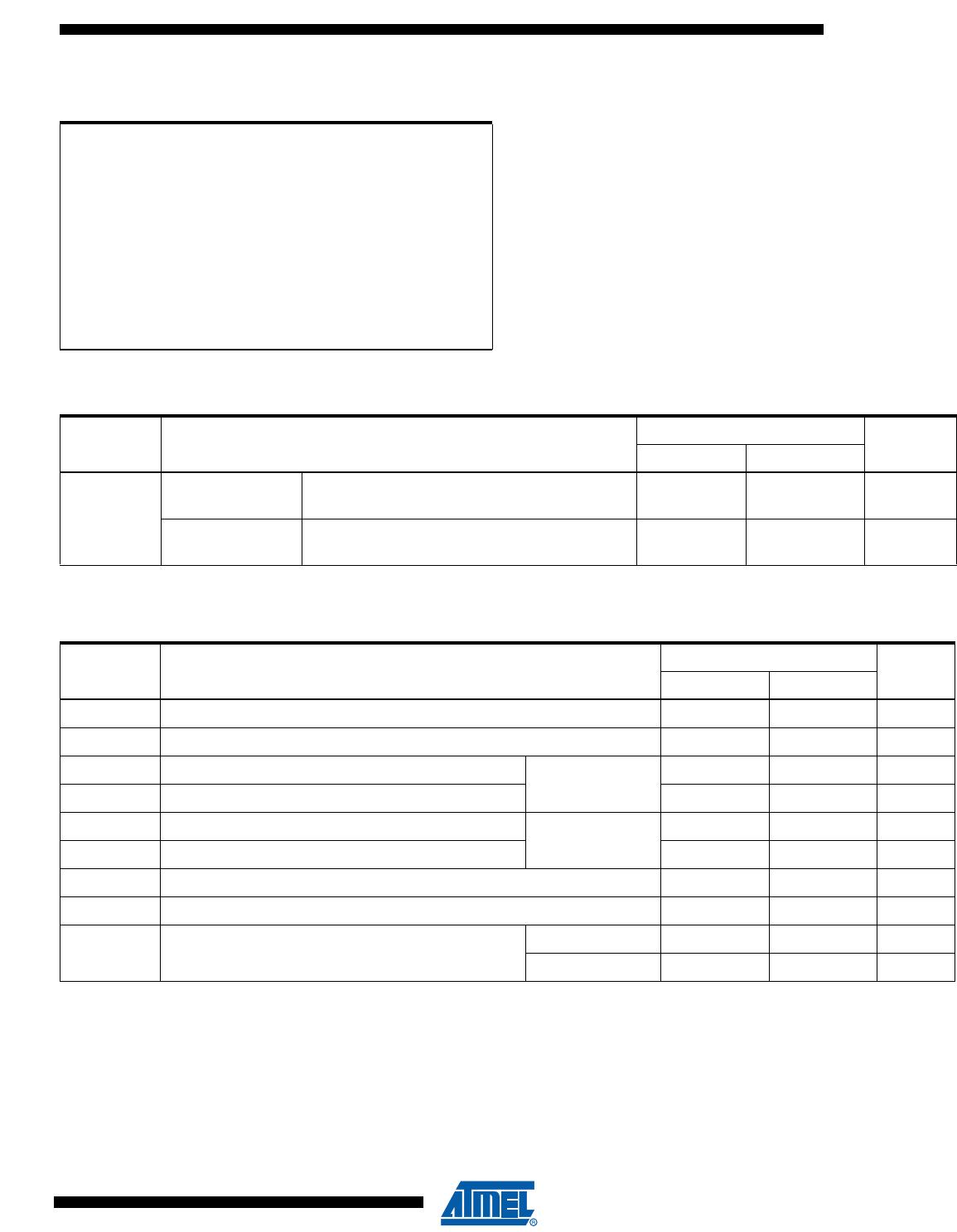

• PAGE_EN must be held Low if download paging is not desired. The PAGESEL[1:0] inputs

must be tied off High or Low. If paging is desired, PAGE_EN must be High and the PAGESEL

pins must be set to High or Low such that the desired page is selected, see Table 5-2 on

page 5.

8. Cascading Serial Configuration Devices

For multiple FPGAs configured as a daisy-chain, or for FPGAs requiring larger configuration

memories, cascaded configurators provide additional memory.

After the last bit from the first configurator is read, the clock signal to the configurator asserts its

CEO

output Low and disables its DATA line driver. The second configurator recognizes the Low

level on its CE input and enables its DATA output.

After configuration is complete, the address counters of all cascaded configurators are reset if

the RESET

/OE on each configurator is driven to its active (Low) level.

If the address counters are not to be reset upon completion, then the RESET/OE input can be

tied to its inactive (High) level.