LTC2942-1

9

29421f

applicaTions inFormaTion

The hard-coded bit A[7] of the status register enables the

host to distinguish the LTC2942-1 from the pin compat-

ible LTC2941, allowing the same software to be used with

both devices.

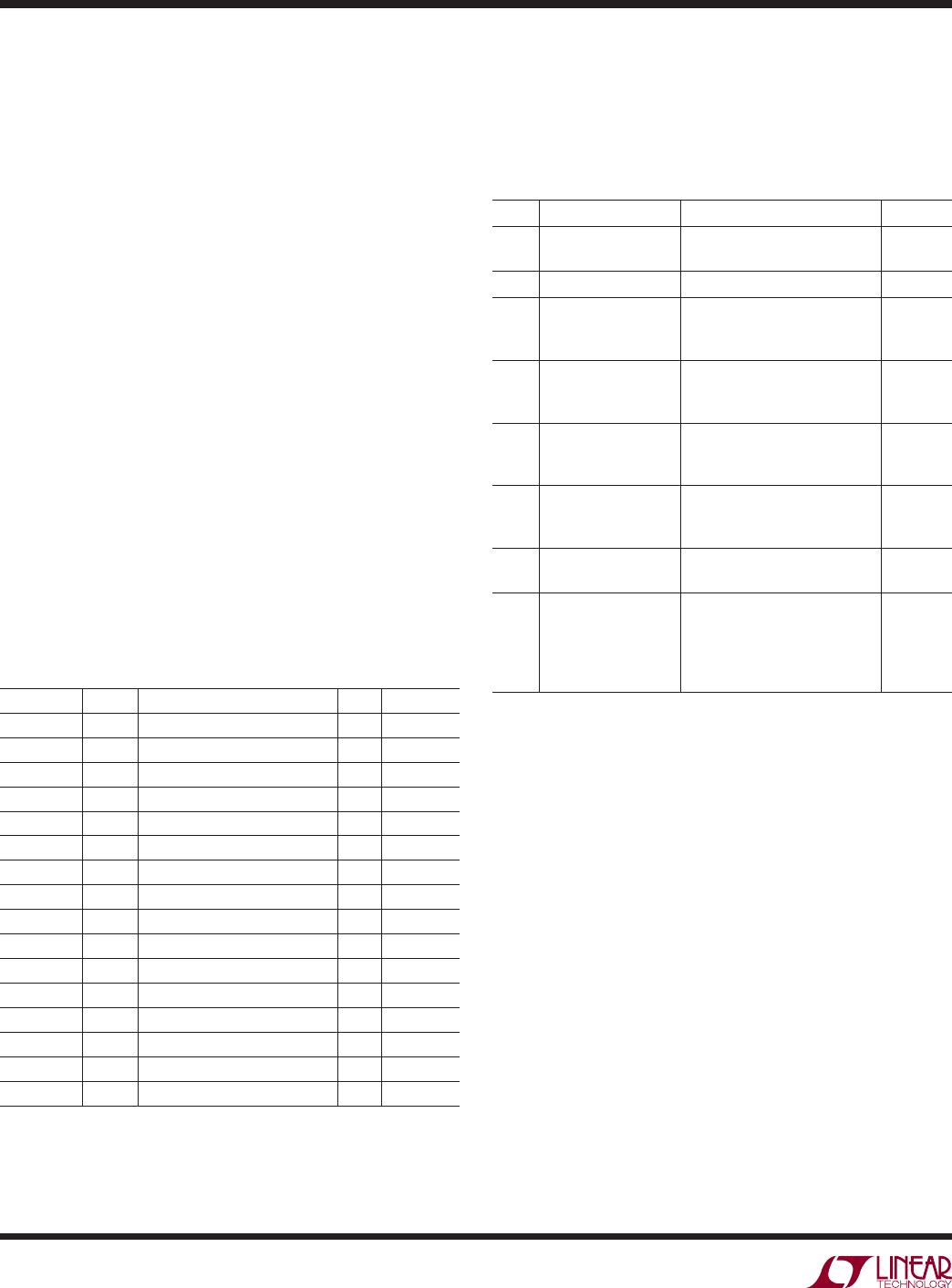

Control Register (B)

The operation of the LTC2942-1 is controlled by program-

ming the control register. Table 3 shows the organization

of the 8-bit control register B[7:0].

Table 3. Control Register B

BIT NAME OPERATION Default

B[7:6] ADC Mode [11] Automatic Mode.

Performs voltage and temperature

conversion every second.

[10] Manual Voltage Mode.

Performs single voltage

conversion, then sleeps.

[01] Manual Temperature Mode.

Performs single temperature

conversion, then sleeps.

[00] Sleep.

[00]

B[5:3] Prescaler M Sets coulomb counter prescaling

factor M between 1 and 128.

Default is 128.

M = 2

(4 • B[5] + 2 • B[4] + B[3])

[111]

B[2:1] AL/CC Configure Configures the AL/CC pin.

[10] Alert Mode.

Alert functionality enabled.

Pin becomes logic output.

[01] Charge Complete Mode.

Pin becomes logic input and

accepts “charge complete” signal

(e.g., from a charger) to set

accumulated charge register (C,D)

to FFFFh.

[00] AL/CC pin disabled.

[11] Not allowed.

[10]

B[0] Shutdown Shut down analog section to

reduce I

SUPPLY

.

[0]

Power Down B[0]

Programming the last bit B[0] of the control register to 1

sets the analog parts of the LTC2942-1 in power down and

the current consumption drops typically below 1µA. All

analog circuits are disabled while the values in the registers

are retained. Note that any charge flowing while B[0] is 1

is not measured and the charge information below 1LSB

of the accumulated charge register is lost.

Alert/Charge Complete Configuration B[2:1]

The AL/CC pin is a dual function pin configured by the

control register. By setting bits B[2:1] to [10] (default)

the AL/CC pin is configured as an alert pin following the

SMBus protocol. In this configuration the AL/CC pin is a

digital output and is pulled low if one of the three mea-

sured quantities (charge, voltage, temperature) exceeds

its high or low threshold or if the value of the accumulated

charge register overflows or underflows. An alert response

procedure started by the master resets the alert at the

AL/CC pin. For further information see the Alert Response

Protocol section.

Setting the control bits B[2:1] to [01] configures the AL/CC

pin as a digital input. In this mode, a high input on the

AL/CC pin communicates to the LTC2942-1 that the bat-

tery is full and the accumulated charge register is set to

its maximum value FFFFh. Columb counting starts when

the AL/CC pin returns to low level.

If neither the alert nor the charge complete functionality

is desired, bits B[2:1] should be set to [00]. The AL/CC

pin is then disabled and should be tied to GND.

Avoid setting B[2:1] to [11] as it enables the alert and the

charge complete modes simultaneously.

Choosing Coulomb Counter Prescaler ‘M’ B[5:3]

To use as much of the range of the accumulated charge

register as possible the prescaler factor M is chosen based

on battery capacity Q

BAT

:

M

Q

mAh

Ah

Q

BAT

BAT

≥ =128

2 0 085

23

16

•

• .

•

M can be set to 1, 2, 4, 8,... 128 by programming B[5:3] of

the control register as M = 2

(4 • B[5] + 2 • B[4] + B[3])

. The default

value after power up is M = 128 = 2

7

(B[5:3] = 111). The

maximum battery capacity supported within the prescaler

range is 5.5Ah with M = 128. See the section Extending

Coulomb Counter Range if battery capacity is higher.

Depending on the choice of prescaler factor M, the charge

LSB of the accumulated charge register becomes:

q mAh

M

LSB

= 0 085

128

. •