AD8314

Rev. B | Page 14 of 20

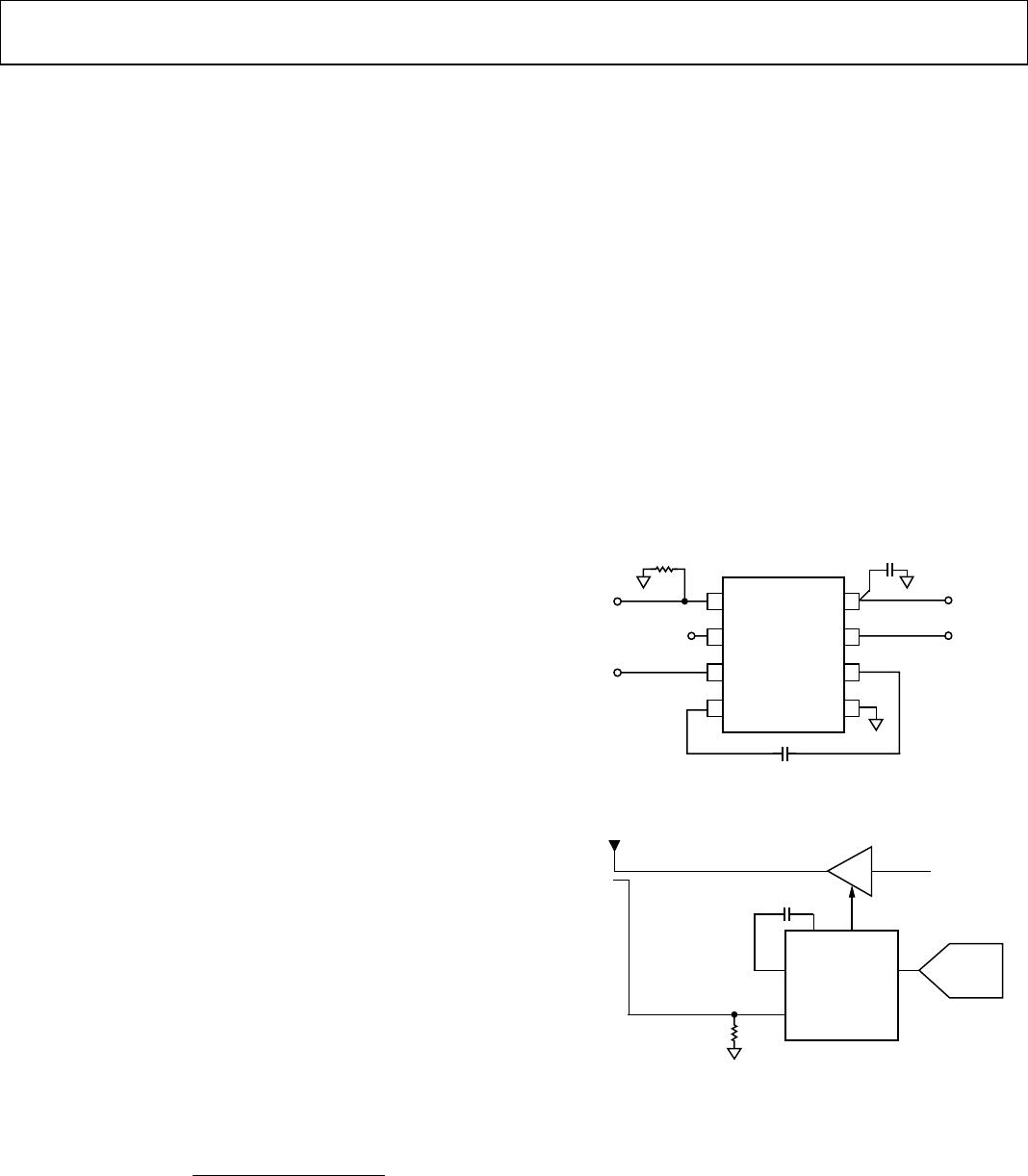

When connected in a PA control loop, as shown in Figure 34,

the voltage V

UP

is not explicitly used but is implicated in again

setting up the required averaging time, by choice of C

F

.

However, now the effective loop response time is a much more

complicated function of the PA’s gain-control characteristics,

which are very nonlinear. A complete solution requires specific

knowledge of the power amplifier.

The transient response of this control loop is determined by the

filter capacitor, C

F.

When this is large, the loop is unconditionally

stable (by virtue of the dominant pole generated by this

capacitor), but the response is sluggish. The minimum value

ensuring stability should be used, requiring full attention to the

particulars of the power amplifier control function. Because this

is invariably nonlinear, the choice must be made for the worst-

case condition, which usually corresponds to the smallest

output from the PA, where the gain function is steepest. In

practice, an improvement in loop dynamics can often be

achieved by adding a response zero, formed by a resistor in

series with C

F

.

POWER-ON AND ENABLE GLITCH

As previously mentioned, the AD8314 can be put into a low

power mode by pulling the ENBL pin to ground. This reduces

the quiescent current from 4.5 mA to 20 µA. Alternatively, the

supply can be turned off to eliminate the quiescent current.

Figure 16 and Figure 26 show the behavior of the V_DN output

under these two conditions (in

Figure 26, ENBL is tied to

VPOS). The glitch that results in both cases can be reduced by

loading the V_DN output.

INPUT COUPLING OPTIONS

The internal 5 pF coupling capacitor of the AD8314, along with

the low frequency input impedance of 3 kΩ, gives a high-pass

input corner frequency of approximately 16 MHz. This sets the

minimum operating frequency.

Figure 35 through Figure 37

show three options for input coupling. A broadband resistive

match can be implemented by connecting a shunt resistor to

ground at RFIN (see

Figure 35). This 52.3 Ω resistor (other

values can also be used to select different overall input

impedances) combines with the input impedance of the

AD8314 (3 kΩ||2 pF) to give a broadband input impedance of

50 Ω. While the input resistance and capacitance (CIN and

RIN) varies by approximately ±20% from device to device, the

dominance of the external shunt resistor means that the variation

in the overall input impedance is close to the tolerance of the

external resistor.

At frequencies above 2 GHz, the input impedance drops below

250 Ω (see

Figure 12), so it is appropriate to use a larger value

shunt resistor. This value is calculated by plotting the input

impedance (resistance and capacitance) on a Smith Chart and

choosing the best value shunt resistor to bring the input

impedance closest to the center of the chart. At 2.5 GHz, a

shunt resistor of 165 Ω is recommended.

A reactive match can also be implemented as shown in

Figure 36.

This is not recommended at low frequencies as device

tolerances dramatically varies the quality of the match because

of the large input resistance. For low frequencies,

Figure 35 or

Figure 37 is recommended.

In

Figure 36, the matching components are drawn as general

reactances. Depending on the frequency, the input impedance at

that frequency, and the availability of standard value components,

either a capacitor or an inductor is used. As in the previous

case, the input impedance at a particular frequency is plotted on

a Smith Chart and matching components are chosen (shunt or

Series L, shunt or Series C) to move the impedance to the center

of the chart.

Table 5 gives standard component values for some

popular frequencies. Matching components for other frequencies

can be calculated using the input resistance and reactance data

over frequency, which is given in

Figure 12. Note that the

reactance is plotted as though it appears in parallel with the

input impedance (which it does because the reactance is

primarily due to input capacitance).

The impedance matching characteristics of a reactive matching

network provide voltage gain ahead of the AD8314; this increases

the device sensitivity (see

Table 5). The voltage gain is calculated by

1

2

log20

10

R

R

GainVoltage

dB

=

where R2 is the input impedance of the AD8314, and R1 is the

source impedance to which the AD8314 is being matched. Note

that this gain is only achieved for a perfect match. Component

tolerances and the use of standard values tend to reduce gain.

50Ω SOURCE

R

SHUNT

52.3Ω

50Ω

C

IN

R

IN

C

C

AD8314

RFIN

V

BIAS

01086-035

Figure 35. Broadband Resistive

50Ω SOURCE

X2

X1

50Ω

C

IN

R

IN

C

C

AD8314

RFIN

V

BIAS

01086-036

Figure 36. Narrowband Reactive

STRIPLINE

C

IN

R

IN

C

C

AD8314

RFIN

V

BIAS

50Ω

R

ATTN

01086-037

Figure 37. Series Attenuation