DATA SHEET

1:2, Differential-to-LVCMOS/LVTTL Zero

Delay Clock Generator

87002-02

87002-02 Rev C 7/13/15 1 ©2015 Integrated Device Technology, Inc.

General Description

The 87002-02 is a highly versatile 1:2 Differential-to-

LVCMOS/LVTTL Clock Generator. The 87002-02 has a differential

clock input. The CLK, nCLK pair can accept most standard

differential input levels. Internal bias on the nCLK input allows the

CLK input to accept LVCMOS/LVTTL. The 87002-02 has a fully

integrated PLL and can be configured as zero delay buffer, multiplier

or divider and has an input and output frequency range of

15.625MHz to 250MHz. The reference divider, feedback divider and

output divider are each programmable, thereby allowing for the

following output-to-input frequency ratios: 8:1, 4:1, 2:1, 1:1, 1:2, 1:4,

1:8. The external feedback allows the device to achieve “zero delay”

between the input clock and the output clocks. The PLL_SEL pin can

be used to bypass the PLL for system test and debug purposes. In

bypass mode, the reference clock is routed around the PLL and into

the internal output dividers.

Features

• Two LVCMOS/LVTTL outputs, 7 typical output impedance

• CLK, nCLK pair can accept the following differential

input levels: LVPECL, LVDS, HSTL, HCSL, SSTL

• Internal bias on nCLK to support LVCMOS/LVTTL levels on CLK

input

• Output frequency range: 15.625MHz to 250MHz

• Input frequency range: 15.625MHz to 250MHz

• VCO range: 250MHz to 500MHz

• External feedback for “zero delay” clock regeneration

with configurable frequencies

• Programmable dividers allow for the following output-to-input

frequency ratios: 8:1, 4:1, 2:1, 1:1, 1:2, 1:4, 1:8

• Fully integrated PLL

• Cycle-to-cycle jitter: 45ps (maximum)

• Output skew: 35ps (maximum)

• Static phase offset: -10ps ± 150ps (3.3V ± 5%)

• Full 3.3V or 2.5V operating supply

• 5V tolerant inputs

• 0°C to 70°C ambient operating temperature

• Available in lead-free (RoHS 6) package

• Industrial temperature information available upon request

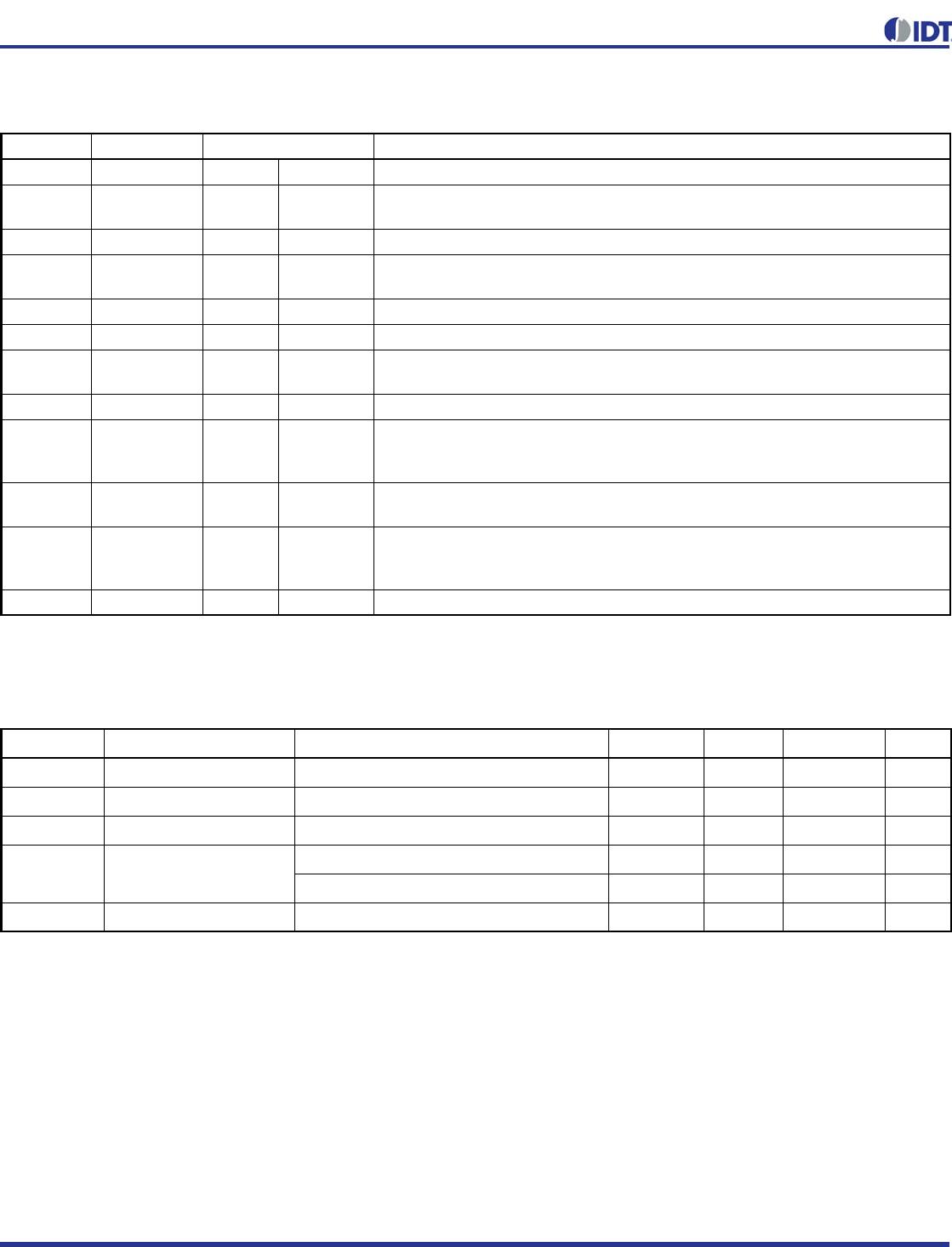

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

CLK

V

DD

SEL3

SEL2

SEL1

SEL0

V

DDO

Q0

GND

nCLK

V

DDO

Q1

GND

V

DDO

nc

MR

FB_IN

PLL_SEL

VDDA

GND

87002-02

20-Lead TSSOP

6.50mm x 4.40mm x 0.925mm package body

G Package

Top View

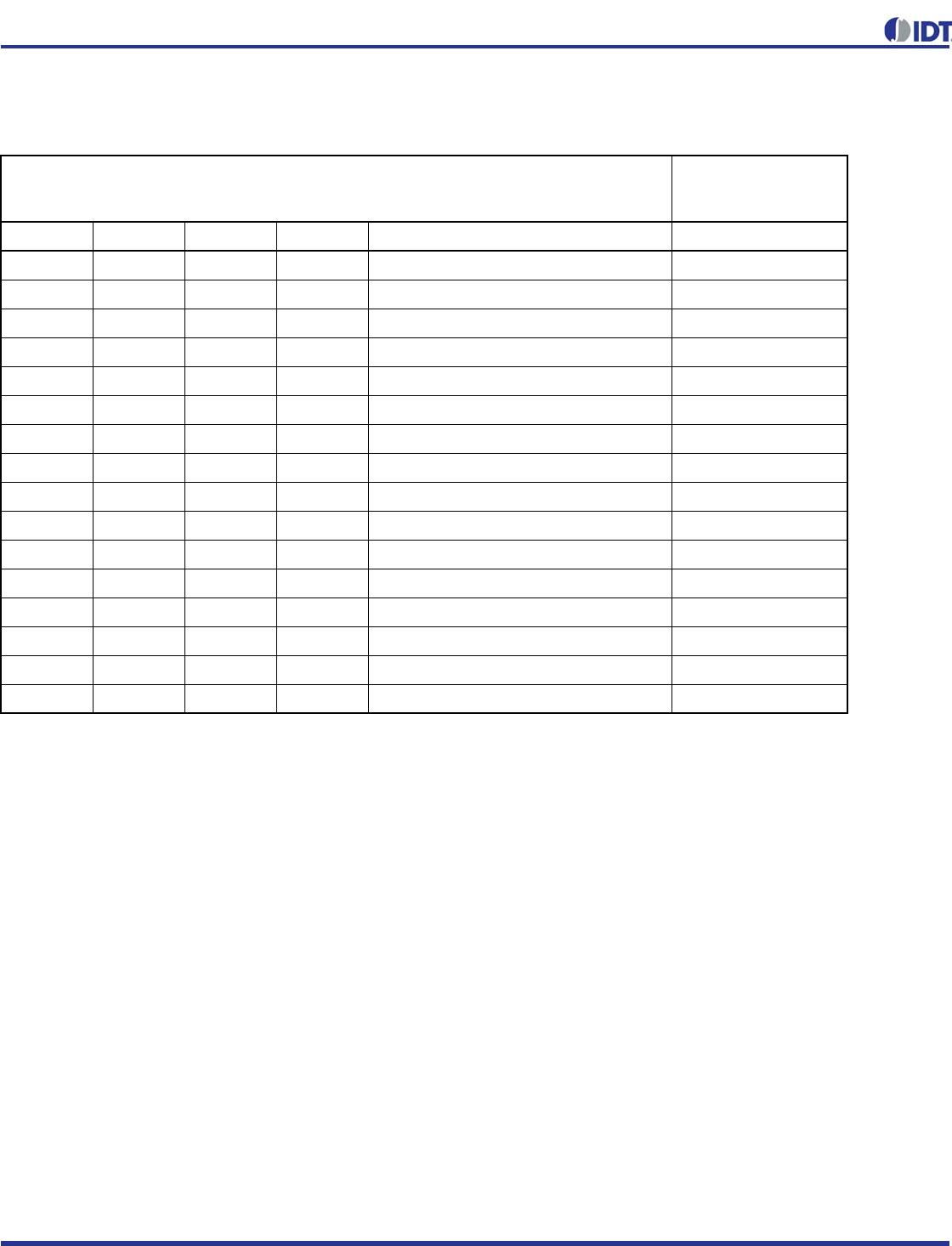

Block Diagram

0

1

Q0

Q1

PLL_SEL

FB_IN

SEL0

SEL1

SEL2

SEL3

MR

CLK

nCLK

PLL

8:1, 4:1, 2:1, 1:1,

1:2, 1:4, 1:8

÷2, ÷4, ÷8, ÷16

÷32, ÷64, ÷128

Pullup/Pulldown

Pulldown

Pulldown

Pulldown

Pullup

Pulldown

Pulldown

Pulldown

Pulldown

Pin Assignment