© Semiconductor Components Industries, LLC, 2014

July, 2018 − Rev. 6

1 Publication Order Number:

NUP4114/D

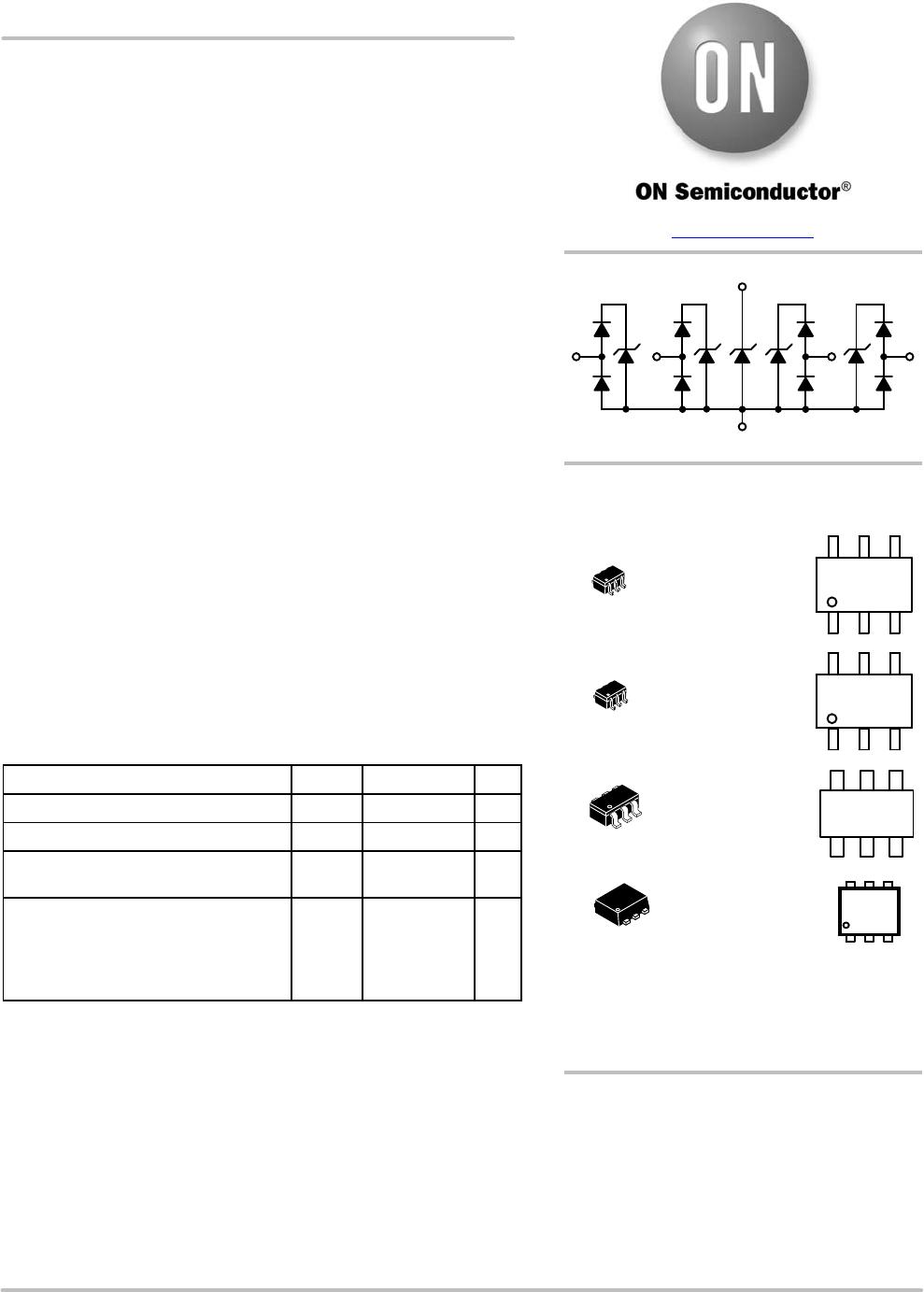

NUP4114 Series

ESD Protection Diode

Low Clamping Voltage

The NUP4114 ESD protection diode array is designed to protect

high speed data lines from ESD. Ultra−low capacitance and high level

of ESD protection make these devices well suited for use in USB 2.0

high speed applications.

Features

• Low Clamping Voltage

• Low Capacitance (<0.6 pF Typical, I/O to GND)

• Low Leakage

• Response Time is Typically < 1.0 ns

• IEC61000−4−2 Level 4 ESD Protection

• SZ Prefix for Automotive and Other Applications Requiring Unique

Site and Control Change Requirements; AEC−Q101 Qualified and

PPAP Capable

• These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS

Compliant

Typical Applications

• LVDS

• USB 2.0 High Speed Data Line and Power Line Protection

• Digital Video Interface (DVI) and HDMI

• Gigabit Ethernet

• Monitors and Flat Panel Displays

• Notebook Computers

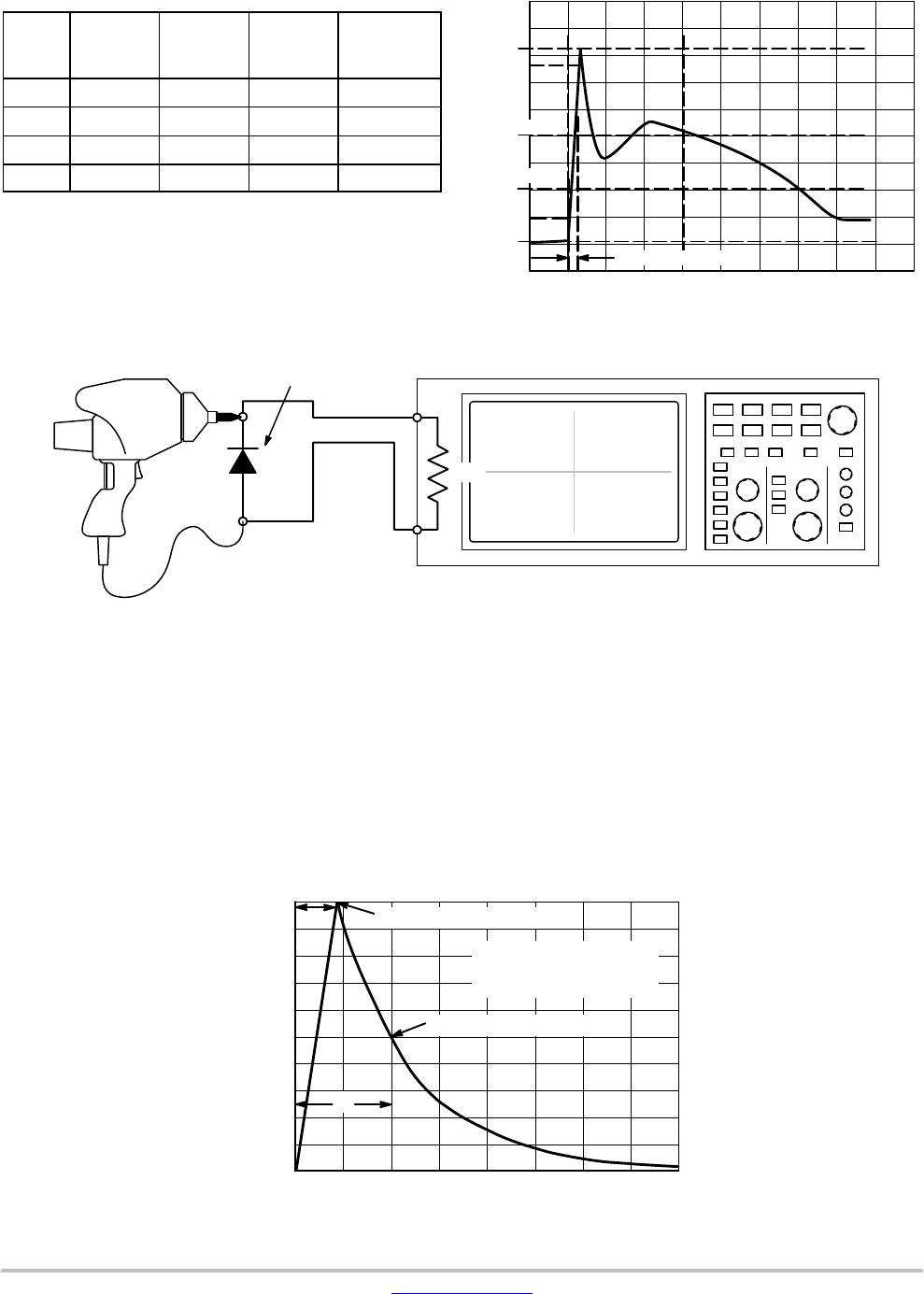

MAXIMUM RATINGS (T

J

= 25°C unless otherwise noted)

Rating

Symbol Value Unit

Operating Junction Temperature Range T

J

−40 to +125 °C

Storage Temperature Range T

stg

−55 to +150 °C

Lead Solder Temperature −

Maximum (10 Seconds)

T

L

260 °C

IEC 61000−4−2 Contact

IEC 61000−4−2 Air

ISO 10605 330 pF / 330 W Contact

ISO 10605 330 pF / 2 kW Contact

ISO 10605 150 pF / 2 kW Contact

ESD ±8

±15

±10

±21

±30

kV

Stresses exceeding those listed in the Maximum Ratings table may damage the

device. If any of these limits are exceeded, device functionality should not be

assumed, damage may occur and reliability may be affected.

See Application Note AND8308/D for further description of survivability specs.

www.onsemi.com

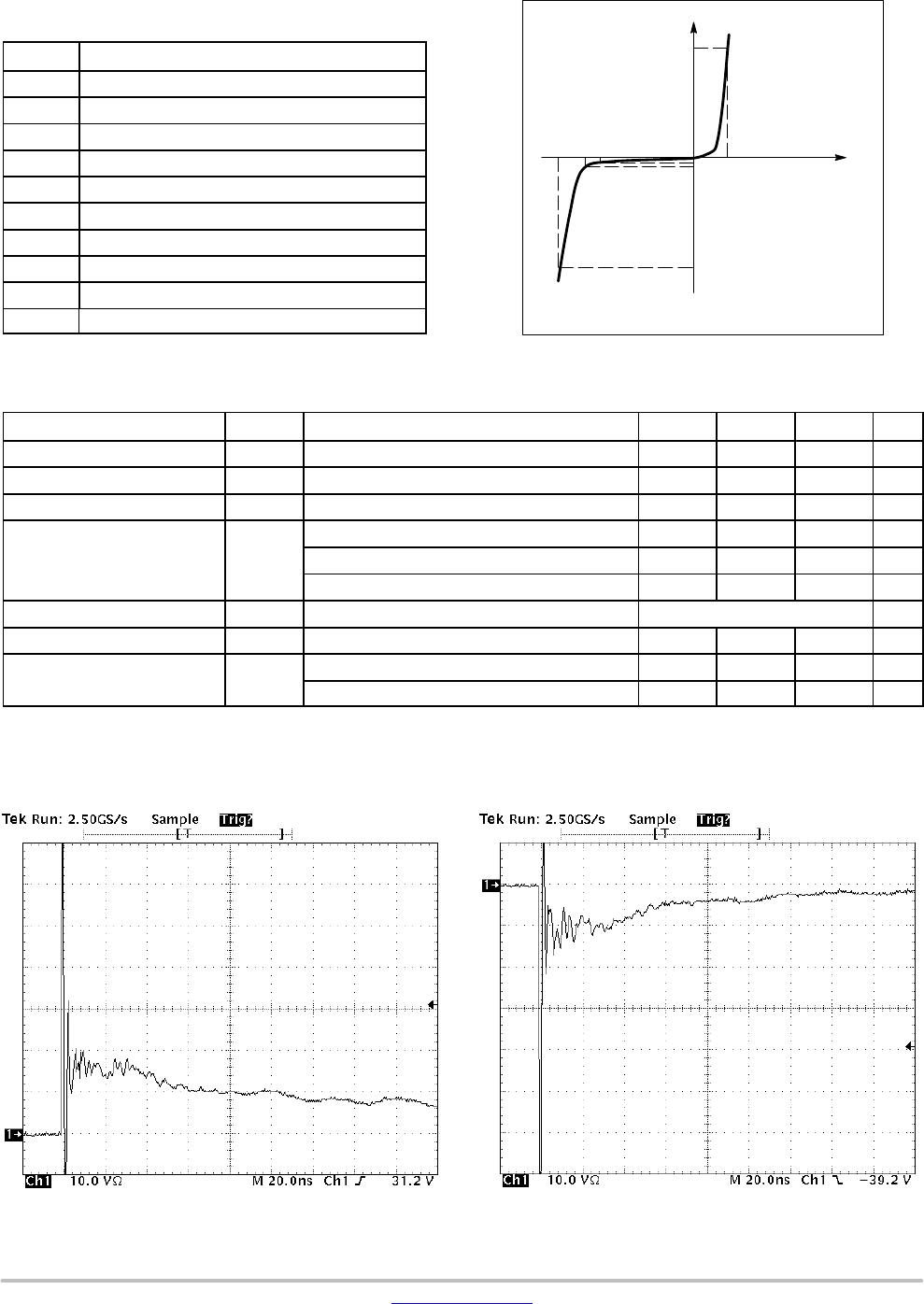

MARKING

DIAGRAMS

X2 MG

G

XXX = Specific Device Code

M = Date Code

G = Pb−Free Package

1

6

1

SC−88

W1 SUFFIX

CASE 419B

(Note: Microdot may be in either location)

5

3

6

2

1

4

X4 MG

G

1

6

1

SC−88

W1 SUFFIX

CASE 419B

P4H

MG

G

1

6

TSOP−6

CASE 318G

STYLE 12

1

SOT−563

CASE 463A

P4MG

G

1

1

6

See detailed ordering and shipping information in the package

dimensions section on page 4 of this data sheet.

ORDERING INFORMATION