NUP4114 Series

www.onsemi.com

5

APPLICATIONS INFORMATION

The new NUP4114 is a low capacitance ESD diode array

designed to protect sensitive electronics such as

communications systems, computers, and computer

peripherals against damage due to ESD events or transient

overvoltage conditions. Because of its low capacitance, it

can be used in high speed I/O data lines. The integrated

design of the NUP4114 offers low capacitance steering

diodes and an ESD diode integrated in a single package

(TSOP−6). If a transient condition occurs, the steering

diodes will drive the transient to the positive rail of the

power supply or to ground. This device protects the power

line against overvoltage conditions to avoid damage to the

power supply and any downstream components.

NUP4114 Configuration Options

The NUP4114 is able to protect up to four data lines

against transient overvoltage conditions by driving them to

a fixed reference point for clamping purposes. The steering

diodes will be forward biased whenever the voltage on the

protected line exceeds the reference voltage (V

f

or

V

CC

+ V

f

). The diodes will force the transient current to

bypass the sensitive circuit.

Data lines are connected at pins 1, 3, 4 and 6. The negative

reference is connected at pin 2. This pin must be connected

directly to ground by using a ground plane to minimize the

PCB’s ground inductance. It is very important to reduce the

PCB trace lengths as much as possible to minimize parasitic

inductances.

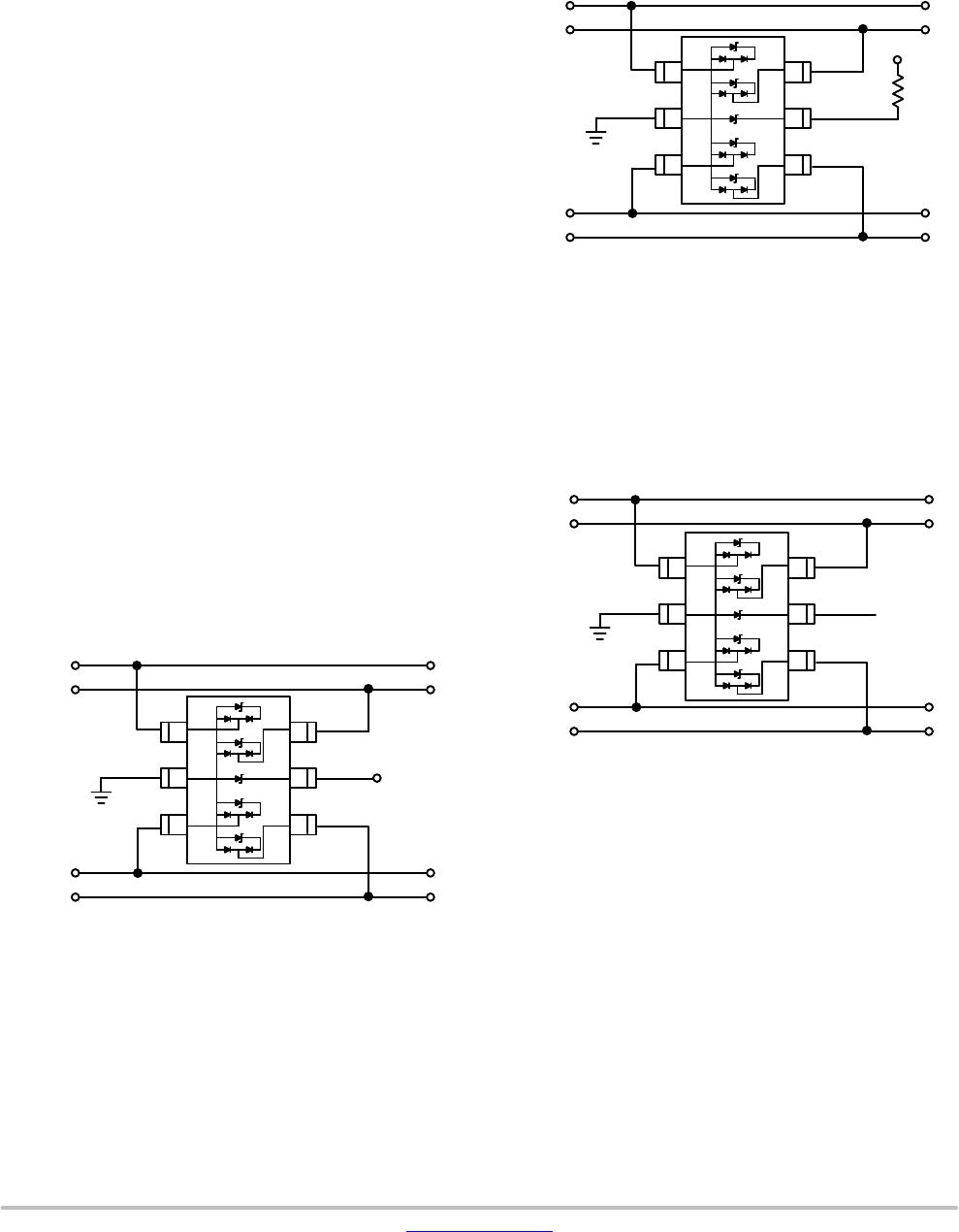

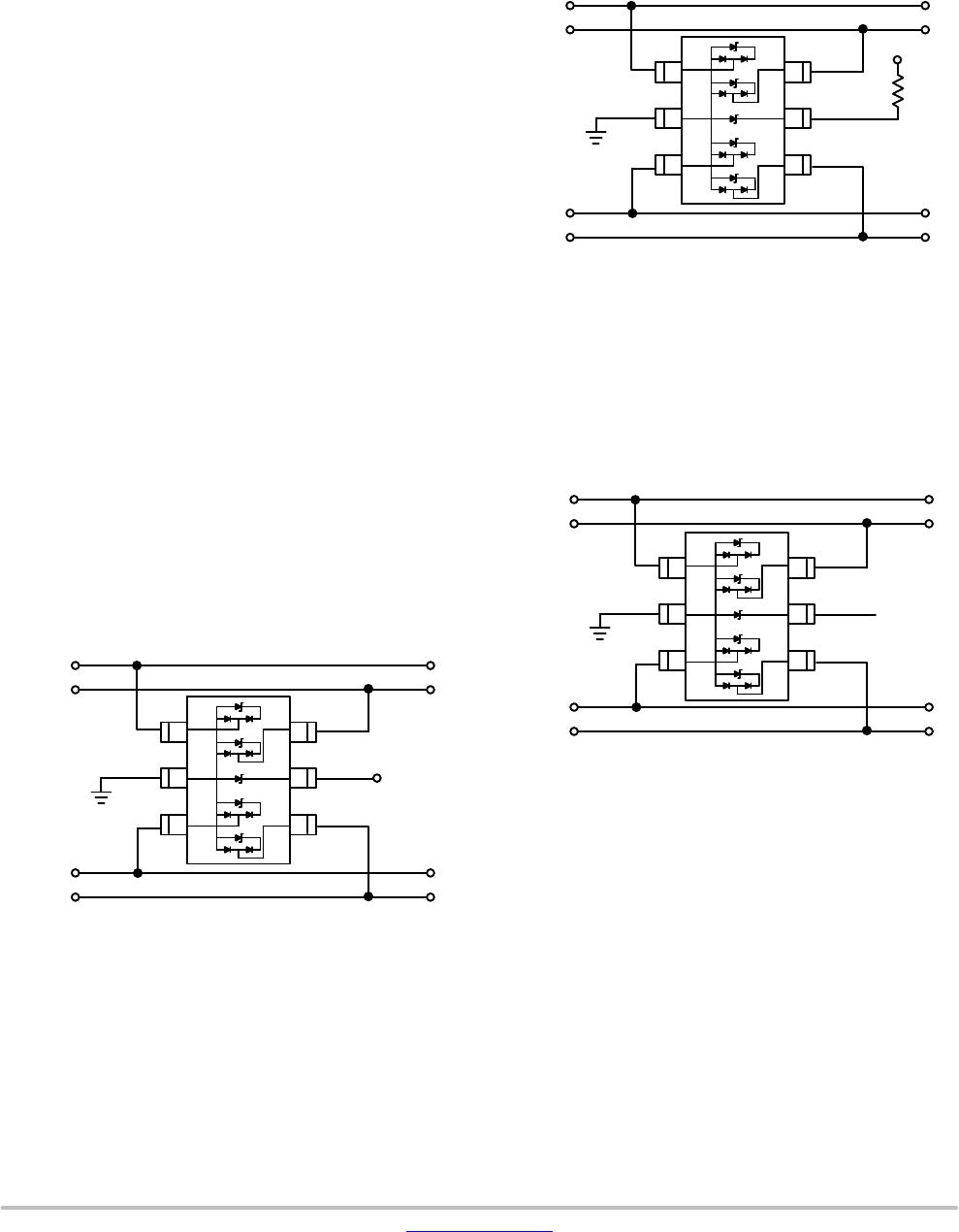

Option 1

Protection of four data lines and the power supply using

V

CC

as reference.

I/O 1

I/O 2

I/O 3

I/O 4

V

CC

6

5

4

1

2

3

For this configuration, connect pin 5 directly to the

positive supply rail (V

CC

), the data lines are referenced to

the supply voltage. The internal ESD diode prevents

overvoltage on the supply rail. Biasing of the steering diodes

reduces their capacitance.

Option 2

Protection of four data lines with bias and power supply

isolation resistor.

V

CC

10 k

I/O 1

I/O 2

I/O 3

I/O 4

6

5

4

1

2

3

The NUP4114 can be isolated from the power supply by

connecting a series resistor between pin 5 and V

CC

. A 10 kW

resistor is recommended for this application. This will

maintain a bias on the internal ESD and steering diodes,

reducing their capacitance.

Option 3

Protection of four data lines using the internal ESD diode

as reference.

I/O 1

I/O 2

I/O 3

I/O 4

NC

6

5

4

1

2

3

In applications lacking a positive supply reference or

those cases in which a fully isolated power supply is

required, the internal ESD can be used as the reference. For

these applications, pin 5 is not connected. In this

configuration, the steering diodes will conduct whenever the

voltage on the protected line exceeds the working voltage of

the ESD plus one diode drop (V

C

= V

f

+ VESD).

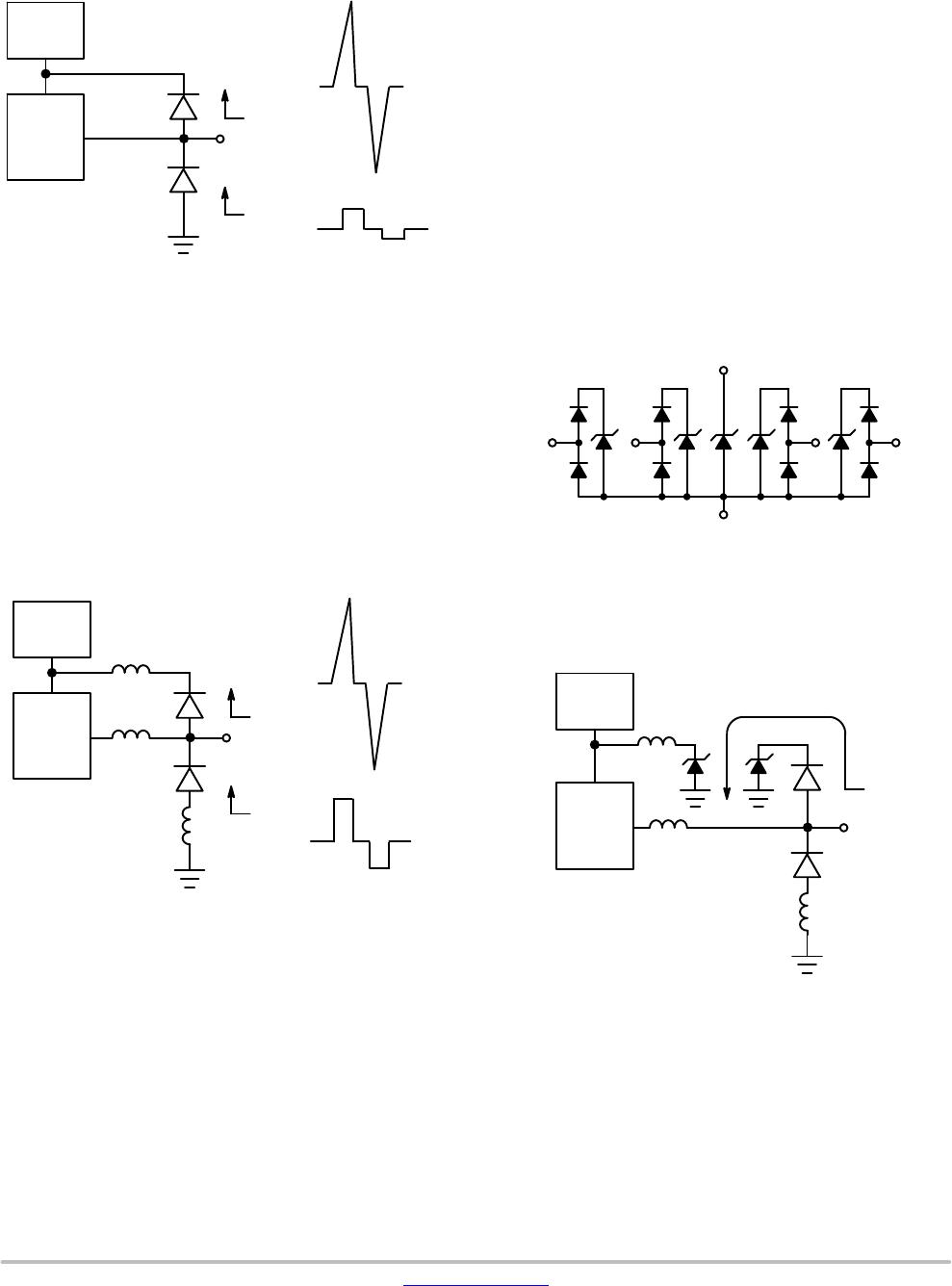

ESD Protection of Power Supply Lines

When using diodes for data line protection, referencing to

a supply rail provides advantages. Biasing the diodes

reduces their capacitance and minimizes signal distortion.