6.4210

IDT71V67703, IDT71V67903, 256K x 36, 512K x 18, 3.3V Synchronous SRAMS with

3.3V I/O, Flow-Through Outputs, Single Cycle Deselect Commercial and Industrial Temperature Ranges

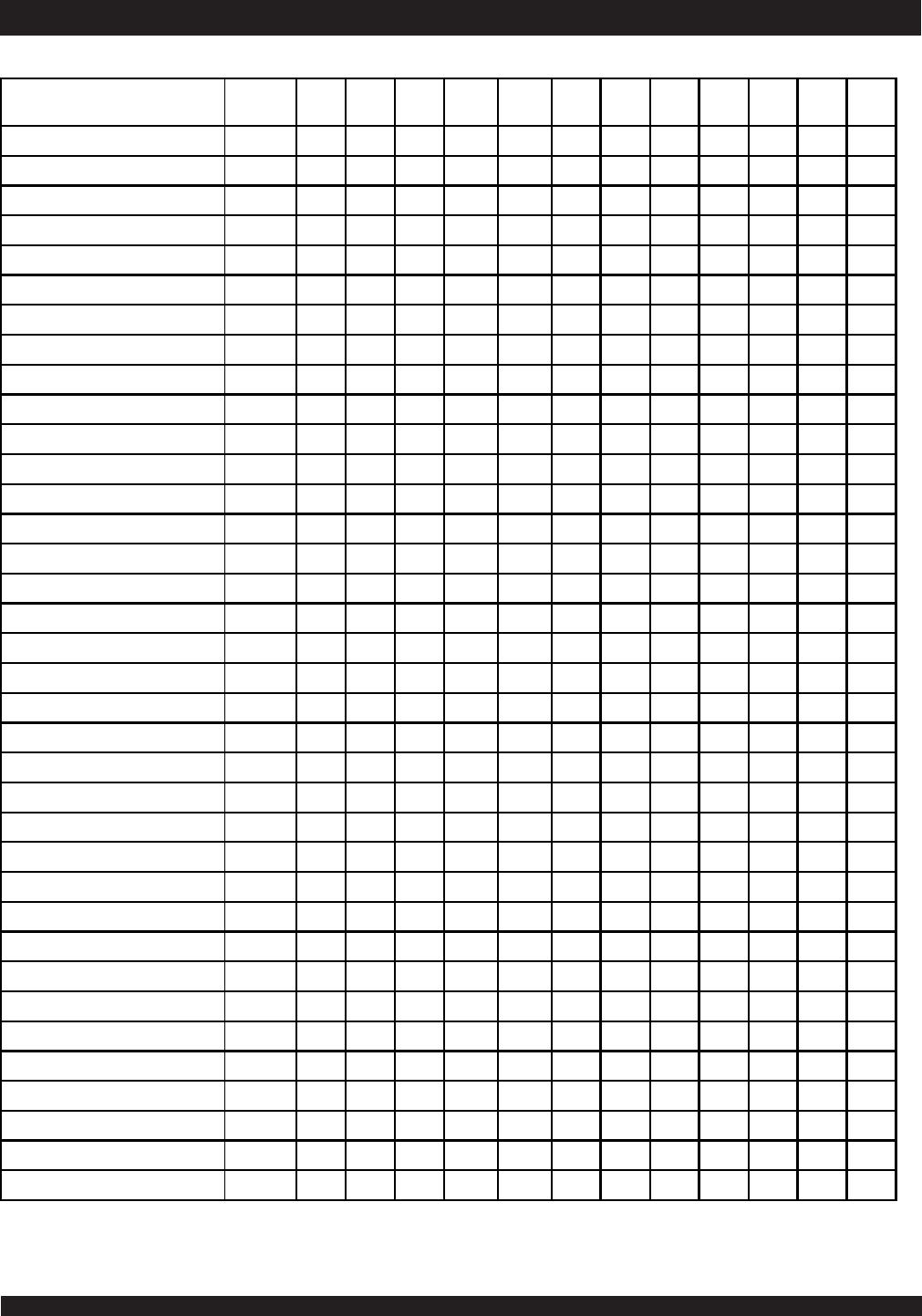

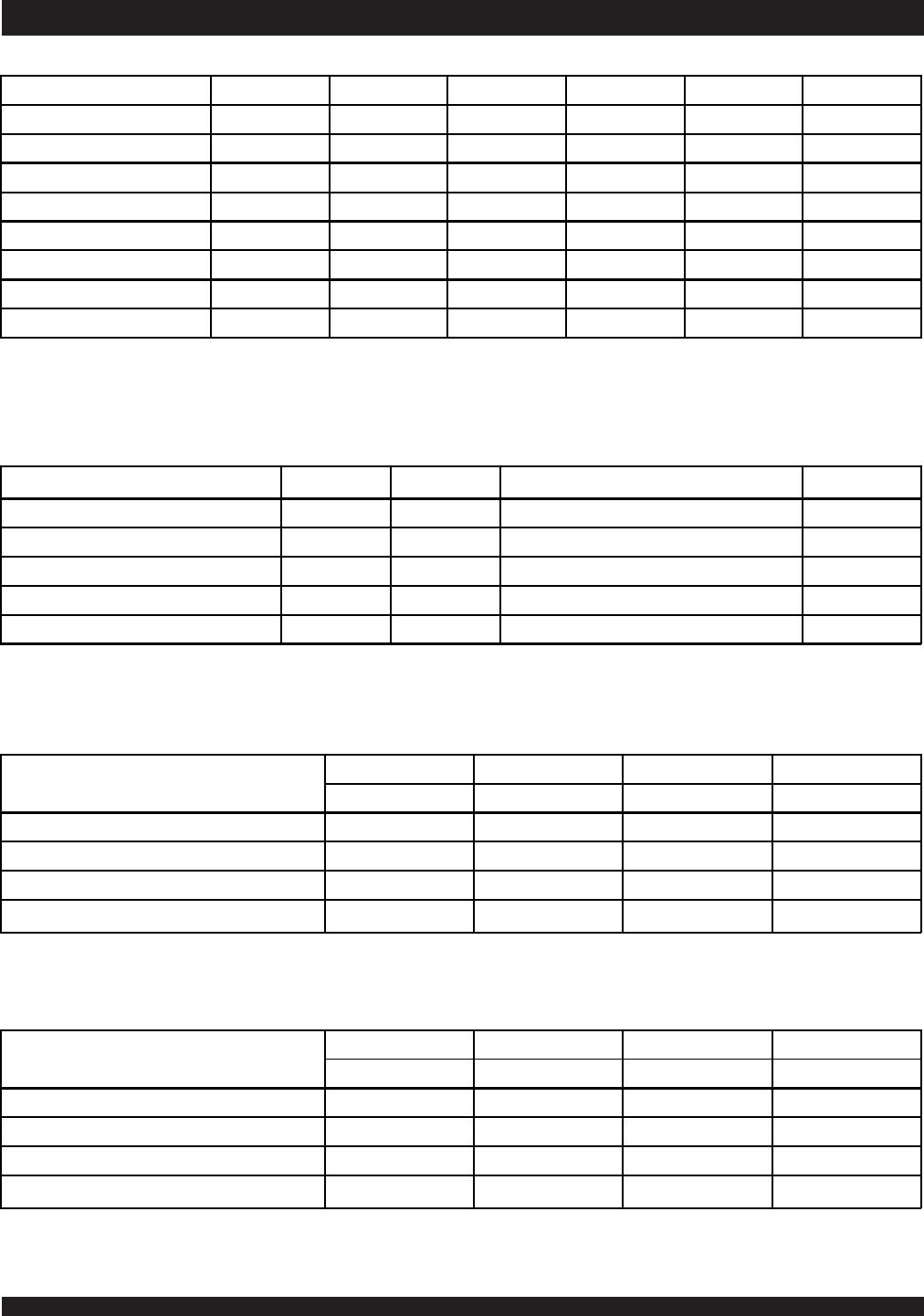

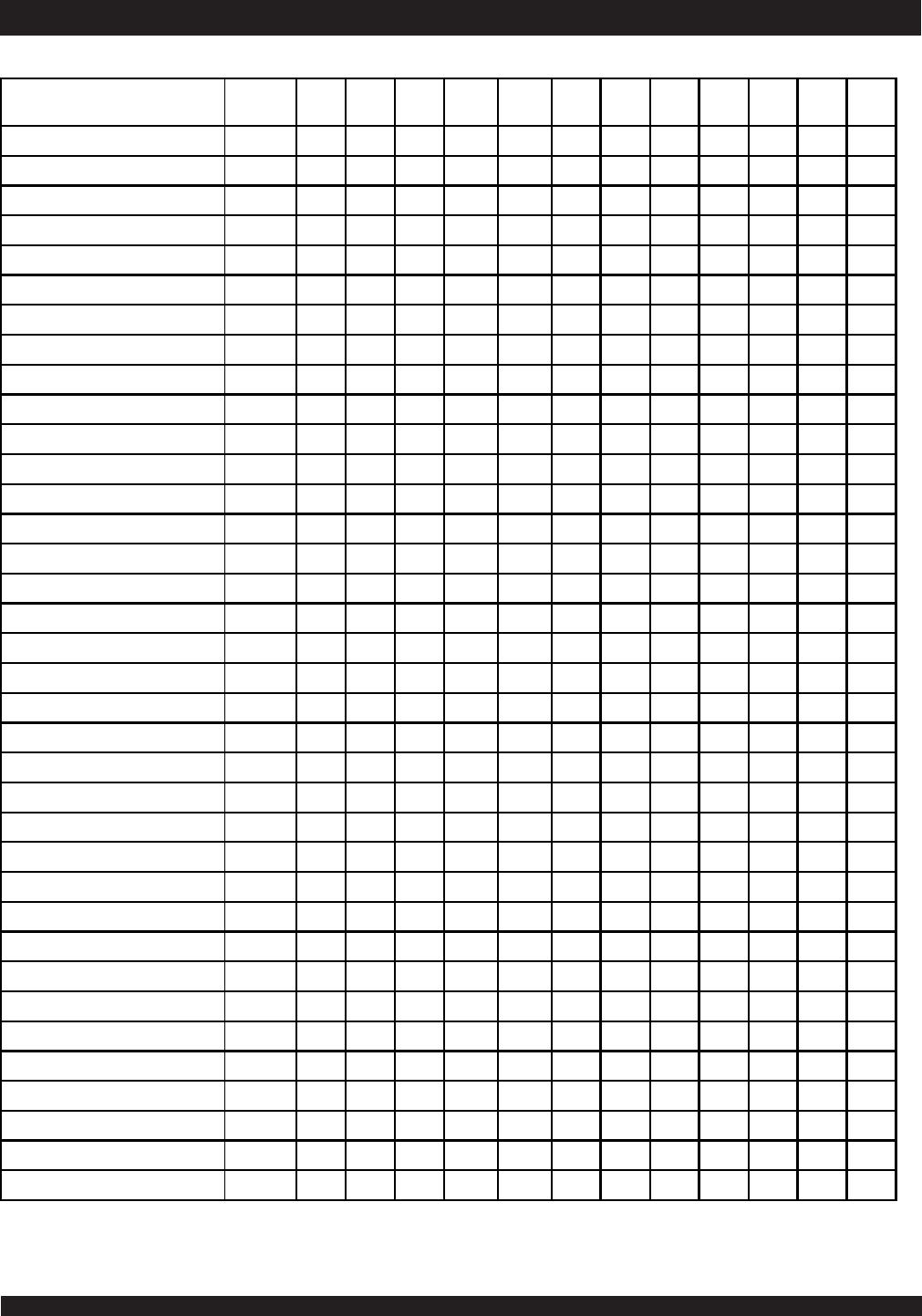

Synchronous Truth Table

(1,3)

NOTES:

1. L = VIL, H = VIH, X = Don’t Care.

2. OE is an asynchronous input.

3. ZZ - low for the table.

Operation Address

Used

CE

CS

0

CS

1

ADSP ADSC ADV GW BWE BWx OE

(2 )

CLK I/O

Deselected Cycle, Power Down None H X X X L X X X X X ↑ HI-Z

Deselected Cycle, Power Down None L X H L X X X X X X ↑ HI-Z

Deselected Cycle, Power Down None L L X L X X X X X X ↑ HI-Z

Deselected Cycle, Power Down None L X H X L X X X X X ↑ HI-Z

Deselected Cycle, Power Down None L L X X L X X X X X ↑ HI-Z

Read Cycle, Begin Burst External L H L L X X X X X L ↑ D

OUT

Read Cycle, Begin Burst External L H L L X X X X X H

↑

HI-Z

Read Cycle, Begin Burst External L H L H L X H H X L ↑ D

OUT

Read Cycle, Begin Burst External L H L H L X H L H L ↑ D

OUT

Read Cycle, Begin Burst External L H L H L X H L H H ↑ HI-Z

Write Cycle, Begin Burst External L H L H L X H L L X ↑ D

IN

Write Cycle, Begin Burst External L H L H L X L X X X ↑ D

IN

Read Cycle, Continue Burst Next X X X H H L H H X L ↑ D

OUT

Read Cycle, Continue Burst Next X X X H H L H H X H ↑ HI-Z

Read Cycle, Continue Burst Next X X X H H L H X H L ↑ D

OUT

Read Cycle, Continue Burst Next X X X H H L H X H H ↑ HI-Z

Read Cycle, Continue Burst Next H X X X H L H H X L ↑ D

OUT

Read Cycle, Continue Burst Next H X X X H L H H X H ↑ HI-Z

Read Cycle, Continue Burst Next H X X X H L H X H L

↑

D

OUT

Read Cycle, Continue Burst Next H X X X H L H X H H ↑ HI-Z

Write Cycle, Continue Burst Next X X X H H L H L L X ↑ D

IN

Write Cycle, Continue Burst Next X X X H H L L X X X ↑ D

IN

Write Cycle, Continue Burst Next H X X X H L H L L X ↑ D

IN

Write Cycle, Continue Burst Next H X X X H L L X X X ↑ D

IN

Read Cycle, Suspend Burst Current X X X H H H H H X L

↑

D

OUT

Read Cycle, Suspend Burst Current X X X H H H H H X H ↑ HI-Z

Read Cycle, Suspend Burst Current X X X H H H H X H L ↑ D

OUT

Read Cycle, Suspend Burst Current X X X H H H H X H H ↑ HI-Z

Read Cycle, Suspend Burst Current H X X X H H H H X L ↑ D

OUT

Read Cycle, Suspend Burst Current H X X X H H H H X H ↑ HI-Z

Read Cycle, Suspend Burst Current H X X X H H H X H L

↑

D

OUT

Read Cycle, Suspend Burst Current H X X X H H H X H H ↑ HI-Z

Write Cycle, Suspend Burst Current X X X H H H H L L X ↑ D

IN

Write Cycle, Suspend Burst Current X X X H H H L X X X ↑ D

IN

Write Cycle, Suspend Burst Current H X X X H H H L L X ↑ D

IN

Write Cycle, Suspend Burst Current H X X X H H L X X X ↑ D

IN

5309 tbl 11