MC10EP32, MC100EP32

www.onsemi.com

3

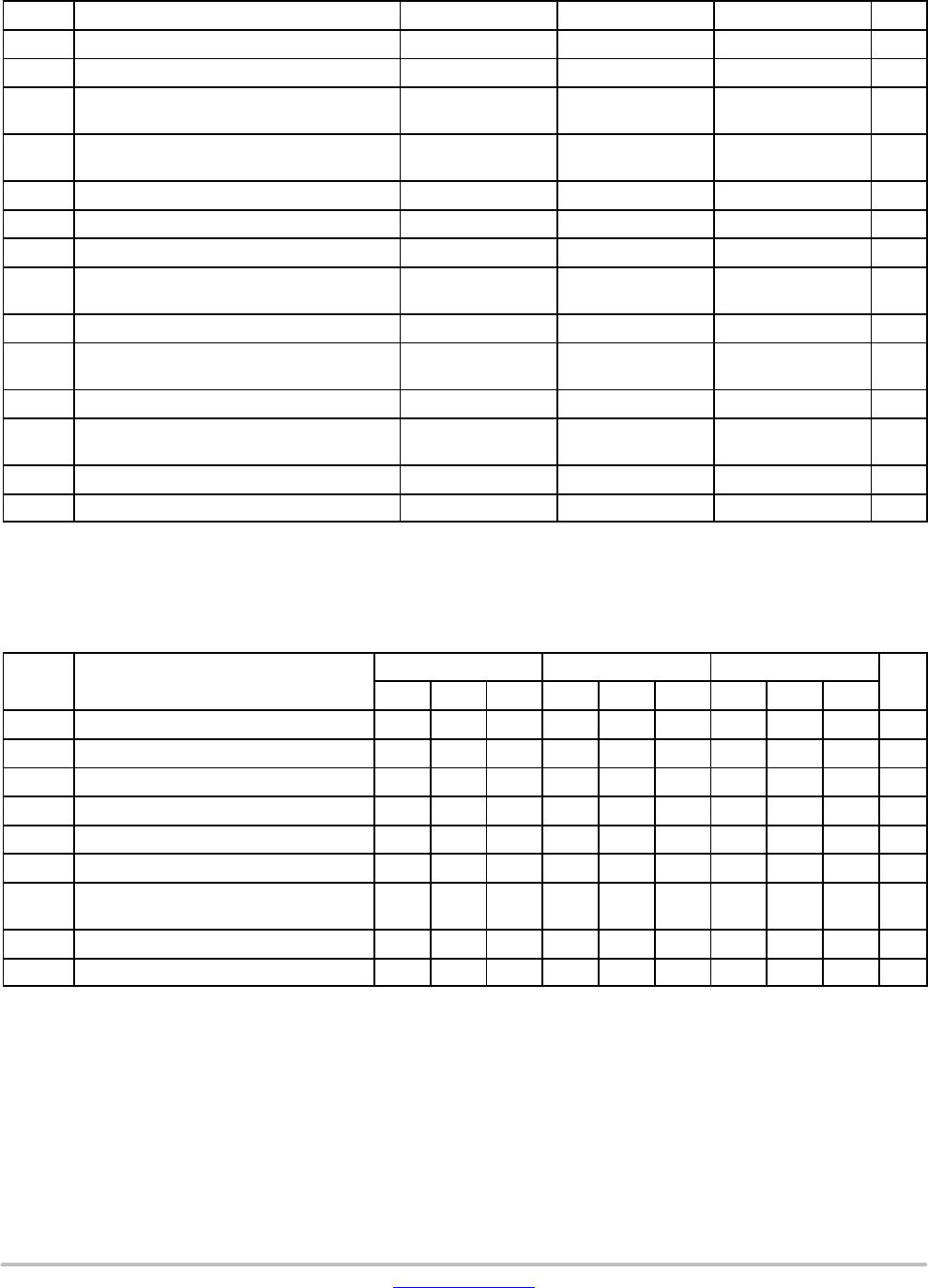

Table 4. MAXIMUM RATINGS

Symbol Parameter Condition 1 Condition 2 Rating Unit

V

CC

PECL Mode Power Supply V

EE

= 0 V 6 V

V

EE

NECL Mode Power Supply V

CC

= 0 V −6 V

V

I

PECL Mode Input Voltage

NECL Mode Input Voltage

V

EE

= 0 V

V

CC

= 0 V

V

I

v V

CC

V

I

w V

EE

6

−6

V

I

out

Output Current Continuous

Surge

50

100

mA

I

BB

V

BB

Sink/Source ± 0.5 mA

T

A

Operating Temperature Range −40 to +85 °C

T

stg

Storage Temperature Range −65 to +150 °C

q

JA

Thermal Resistance (Junction-to-Ambient) 0 lfpm

500 lfpm

SOIC−8NB 190

130

°C/W

q

JC

Thermal Resistance (Junction-to-Case) Standard Board SOIC−8NB 41 to 44 °C/W

q

JA

Thermal Resistance (Junction-to-Ambient) 0 lfpm

500 lfpm

TSSOP−8 185

140

°C/W

q

JC

Thermal Resistance (Junction-to-Case) Standard Board TSSOP−8 41 to 44 °C/W

q

JA

Thermal Resistance (Junction-to-Ambient) 0 lfpm

500 lfpm

DFN8 129

84

°C/W

T

sol

Wave Solder (Pb-Free) <2 to 3 sec @ 260°C 265 °C

q

JC

Thermal Resistance (Junction-to-Case) (Note 1) DFN8 35 to 40 °C/W

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

1. JEDEC standard multilayer board − 2S2P (2 signal, 2 power)

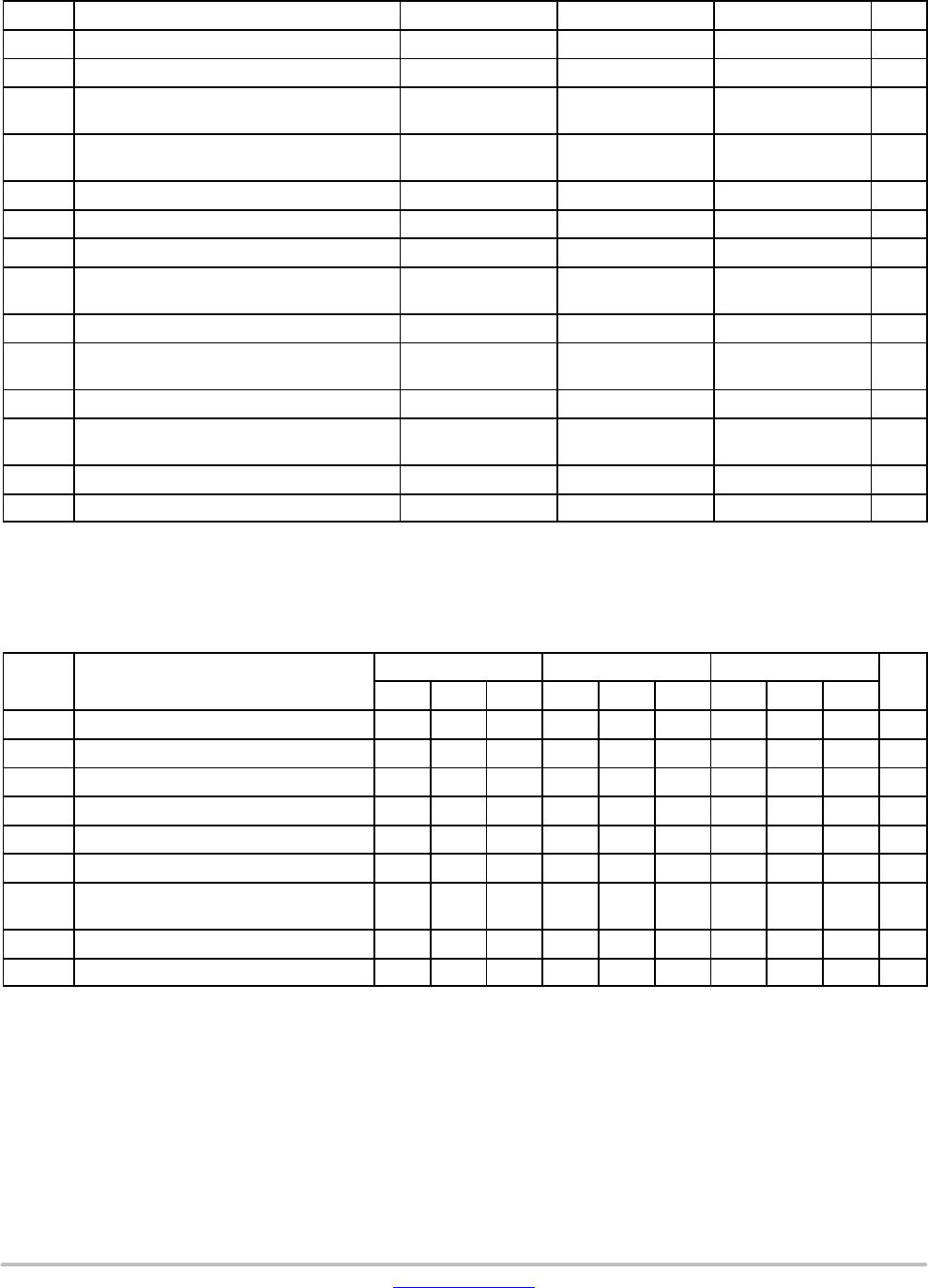

Table 5. 10EP DC CHARACTERISTICS, PECL (V

CC

= 3.3 V, V

EE

= 0 V (Note 1))

Symbol

Characteristic

−40°C 25°C 85°C

Unit

Min Typ Max Min Typ Max Min Typ Max

I

EE

Power Supply Current 23 30 40 23 30 40 23 30 40 mA

V

OH

Output HIGH Voltage (Note 2) 2165 2290 2415 2230 2355 2480 2290 2415 2540 mV

V

OL

Output LOW Voltage (Note 2) 1365 1490 1615 1430 1555 1680 1490 1615 1740 mV

V

IH

Input HIGH Voltage (Single-Ended) 2090 2415 2155 2480 2215 2540 mV

V

IL

Input LOW Voltage (Single-Ended) 1365 1690 1430 1755 1490 1815 mV

V

BB

Output Voltage Reference 1790 1890 1990 1855 1955 2055 1915 2015 2115 mV

V

IHCMR

Input HIGH Voltage Common Mode

Range (Differential Configuration) (Note 3)

2.0 3.3 2.0 3.3 2.0 3.3 V

I

IH

Input HIGH Current 150 150 150

mA

I

IL

Input LOW Current 0.5 0.5 0.5

mA

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared

operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit

values are applied individually under normal operating conditions and not valid simultaneously.

1. Input and output parameters vary 1:1 with V

CC

. V

EE

can vary +0.3 V to −2.2 V.

2. All loading with 50 W to V

CC

− 2.0 V.

3. V

IHCMR

min varies 1:1 with V

EE

, V

IHCMR

max varies 1:1 with V

CC

. The V

IHCMR

range is referenced to the most positive side of the differential

input signal.