DS197 (v1.2) February 23, 2017 www.xilinx.com

Product Specification 1

© Copyright 2014–2017 Xilinx, Inc., Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, UltraScale, Virtex, Vivado, Zynq, and other designated brands included herein are

trademarks of Xilinx in the United States and other countries. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used under license. All other trademarks are the

property of their respective owners.

General Description

Xilinx® XA Artix®-7 (Automotive) FPGAs are optimized for the lowest cost and power with small form-factor packaging for high-volume automotive

applications. Designers can leverage more logic per watt compared to the Spartan®-6 family.

Built on a state-of-the-art high-performance/low-power (HPL) 28 nm high-k metal gate (HKMG) process technology, XA Artix-7 FPGAs redefine low-cost

alternatives with more logic per watt. Unparalleled increase in system performance with 52 Gb/s I/O bandwidth, 100,000 logic cell capacity, 264 GMAC/s

DSP, and flexible built-in DDR3 memory interfaces enable a new class of high-throughput, low-cost automotive applications. XA Artix-7 FPGAs also offer

many high-end features, such as integrated advanced Analog Mixed Signal (AMS) technology. Analog becomes the next level of integration through the

seamless implementation of independent dual 12-bit, 1 MSPS, 17-channel analog-to-digital converters. Most importantly, XA Artix-7 FPGAs proudly meet

the high standards of the automotive grade with a maximum temperature of 125°C.

Summary of XA Artix-7 FPGA Features

• Automotive Temperatures:

• I-Grade: Tj= –40°C to +100°C

• Q-Grade: Tj= –40°C to +125°C

• Automotive Standards:

• ISO-TS16949 compliant

• AEC-Q100 qualification

• Production Part Approval Process (PPAP) documentation

• Beyond AEC-Q100 qualification is available upon request

• Advanced high-performance FPGA logic based on real 6-input look-

up table (LUT) technology configurable as distributed memory

• 36 Kb dual-port block RAM with built-in FIFO logic for on-chip data

buffering

• Sub-watt performance in 100,000 logic cells

• High-performance SelectIO™ technology with support for DDR3

interfaces up to 800 Mb/s

• High-speed serial connectivity with built-in serial transceivers from

500 Mb/s to maximum rates of 6.25 Gb/s, enabling 50 Gb/s peak

bandwidth (full duplex)

• A user configurable analog interface (XADC), incorporating dual

12-bit 1MSPS analog-to-digital converters with on-chip thermal and

supply sensors.

• Single-ended and differential I/O standards with speeds of up to

1.25 Gb/s

• 240 DSP48E1 slices with up to 264 GMACs of signal processing

• Powerful clock management tiles (CMT), combining phase-locked

loop (PLL) and mixed-mode clock manager (MMCM) blocks for high

precision and low jitter

• Integrated block for PCI Express® (PCIe®), for up to x4 Gen2

Endpoint

• Wide variety of configuration options, including support for

commodity memories, 256-bit AES encryption with HMAC/SHA-256

authentication, and built-in SEU detection and correction

• Low-cost wire-bond packaging, offering easy migration between

family members in the same package, all packages available Pb-free

• Designed for high performance and lowest power with 28 nm,

HKMG, HPL process, 1.0V core voltage process technology

• Strong automotive-specific third-party ecosystem with IP,

development boards, and design services

XA Artix-7 FPGA Summary Tables

10

XA Artix-7 FPGAs Data Sheet: Overview

DS197 (v1.2) February 23, 2017 Product Specification

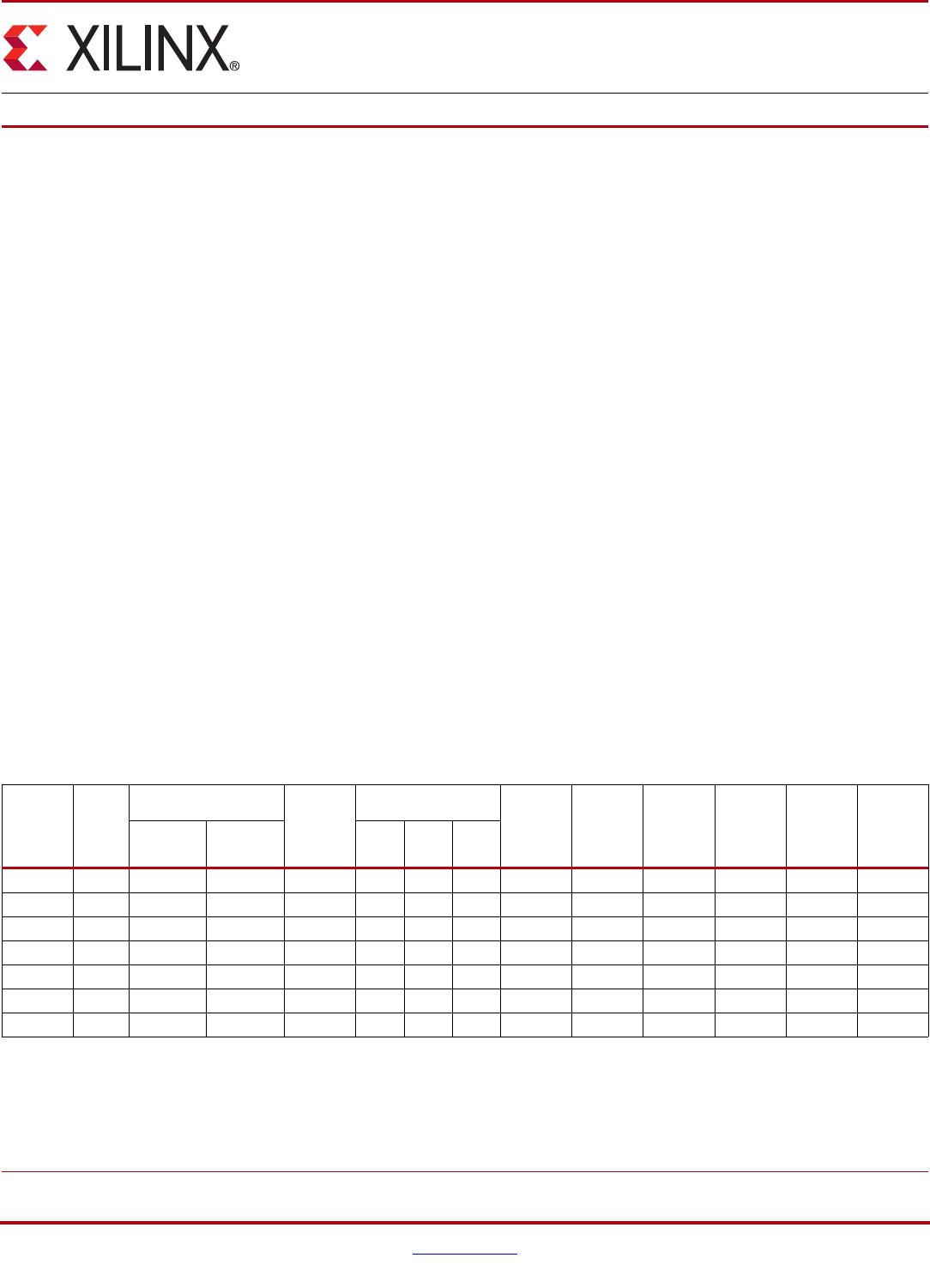

Table 1: XA Artix-7 FPGA Device-Feature Table

Device

Logic

Cells

Configurable Logic

Blocks (CLBs)

DSP48E1

Slices

(2)

Block RAM Blocks

(3)

CMTs

(4)

PCIe

(5)

GTPs

XADC

Blocks

Total I/O

Banks

(6)

Max User

I/O

(7)

Slices

(1)

Max

Distributed

RAM (Kb)

18 Kb 36 Kb

Max

(Kb)

XA7A12T12,8002,00017140402072031213150

XA7A15T16,6402,60020045502590051415210

XA7A25T23,3603,6503138090451,62031413150

XA7A35T33,2805,20040090100501,80051415210

XA7A50T52,1608,150600120150752,70051415210

XA7A75T75,52011,8008921802101053,78061416285

XA7A100T101,44015,8501,1882402701354,86061416285

Notes:

1. Each 7 series FPGA slice contains four LUTs and eight flip-flops; only some slices can use their LUTs as distributed RAM or SRLs.

2. Each DSP slice contains a pre-adder, a 25 x 18 multiplier, an adder, and an accumulator.

3. Block RAMs are fundamentally 36 Kb in size; each block can also be used as two independent 18 Kb blocks.

4. Each CMT contains one MMCM and one PLL.

5. XA Artix-7 FPGA Interface Blocks for PCI Express support up to x4 Gen 2.

6. Does not include configuration Bank 0.

7. This number does not include GTP transceivers.