D

2

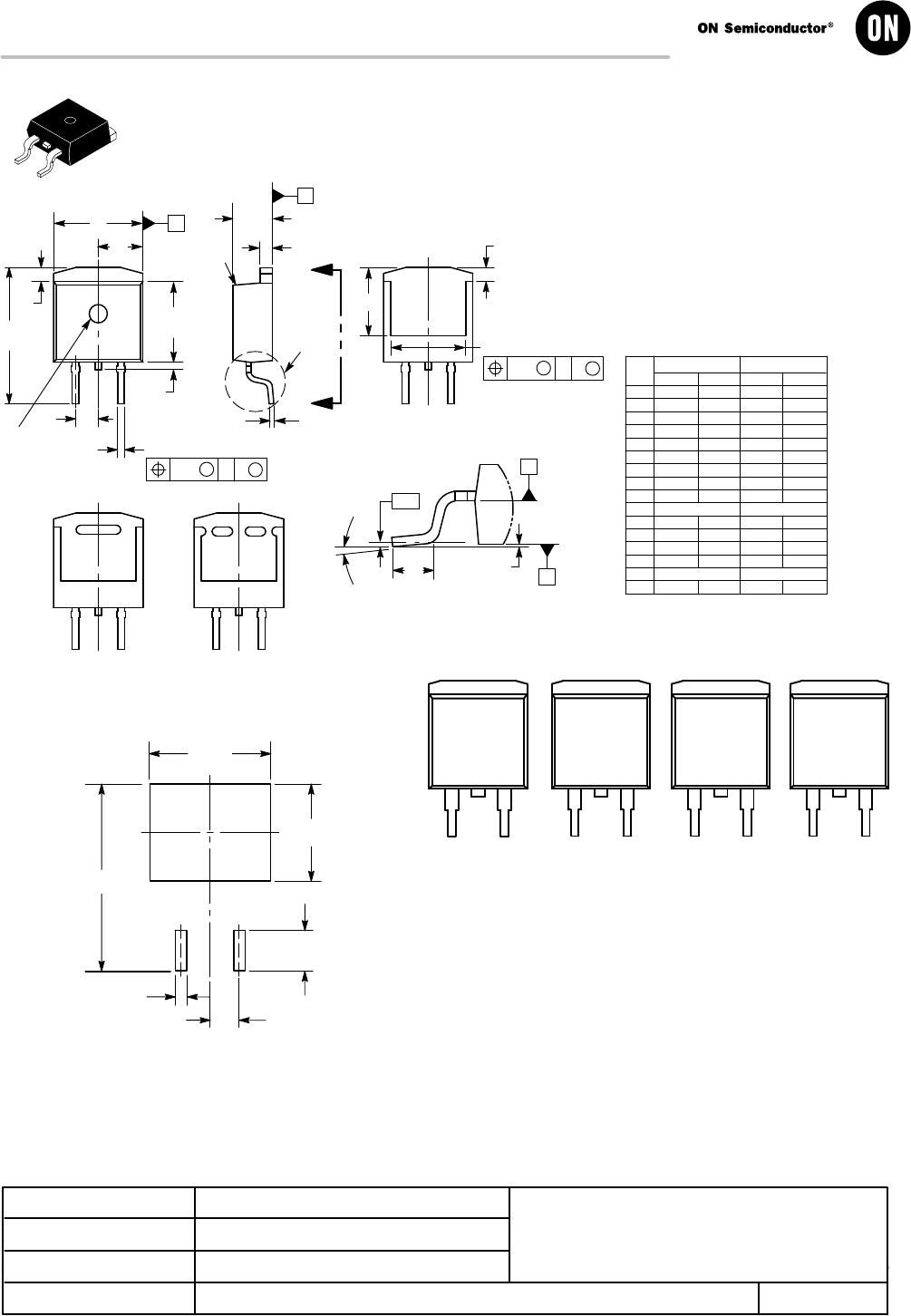

PAK−3 (TO−263, 3−LEAD)

CASE 418AJ

ISSUE B

DATE 08 OCT 2013

SCALE 1:1

DIM MIN MAX MIN MAX

MILLIMETERSINCHES

D 0.330 0.380 8.38 9.65

E 0.380 0.420 9.65 10.67

A 0.160 0.190 4.06 4.83

b 0.020 0.039 0.51 0.99

c2 0.045 0.065 1.14 1.65

e 0.100 BSC 2.54 BSC

A1 0.000 0.010 0.00 0.25

c 0.012 0.029 0.30 0.74

L 0.070 0.110 1.78 2.79

H 0.575 0.625 14.60 15.88

L2 −−−− 0.070 −−−− 1.78

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME

Y14.5M, 1994.

2. CONTROLLING DIMENSION: INCHES.

3. CHAMFER OPTIONAL

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD

FLASH. MOLD FLASH SHALL NOT EXCEED 0.005

PER SIDE. THESE DIMENSIONS ARE MEASURED

AT THE OUTERMOST EXTREMES OF THE

PLASTIC BODY AT DATUM H.

5. THERMAL PAD CONTOUR IS OPTIONAL WITHIN

DIMENSIONS E, L1, D1 AND E1.

6. OPTIONAL MOLD FEATURE

E1 0.245 −−−− 6.22 −−−−

L1 −−−− 0.066 −−−− 1.68

D1 0.260 −−−− 6.60 −−−−

L3 0.010 BSC 0.25 BSC

M 08 08°° °°

E

D

H

L1

b

e

A1

B

H

L

M

DETAIL C

SEATING

PLANE

A

2X

M

A

M

0.10 B

c2

c

A

B

SEATING

PLANE

DETAIL C

VIEW A−A

SIDE VIEW

TOP VIEW

E2

L2

A

A

VIEW A−A

E1

D1

L1

OPTIONAL CONSTRUCTIONS

L3

GAUGE

PLANE

NOTE 3

M

A

M

0.10 B

XX

XXXXXXXXX

AWLYWWG

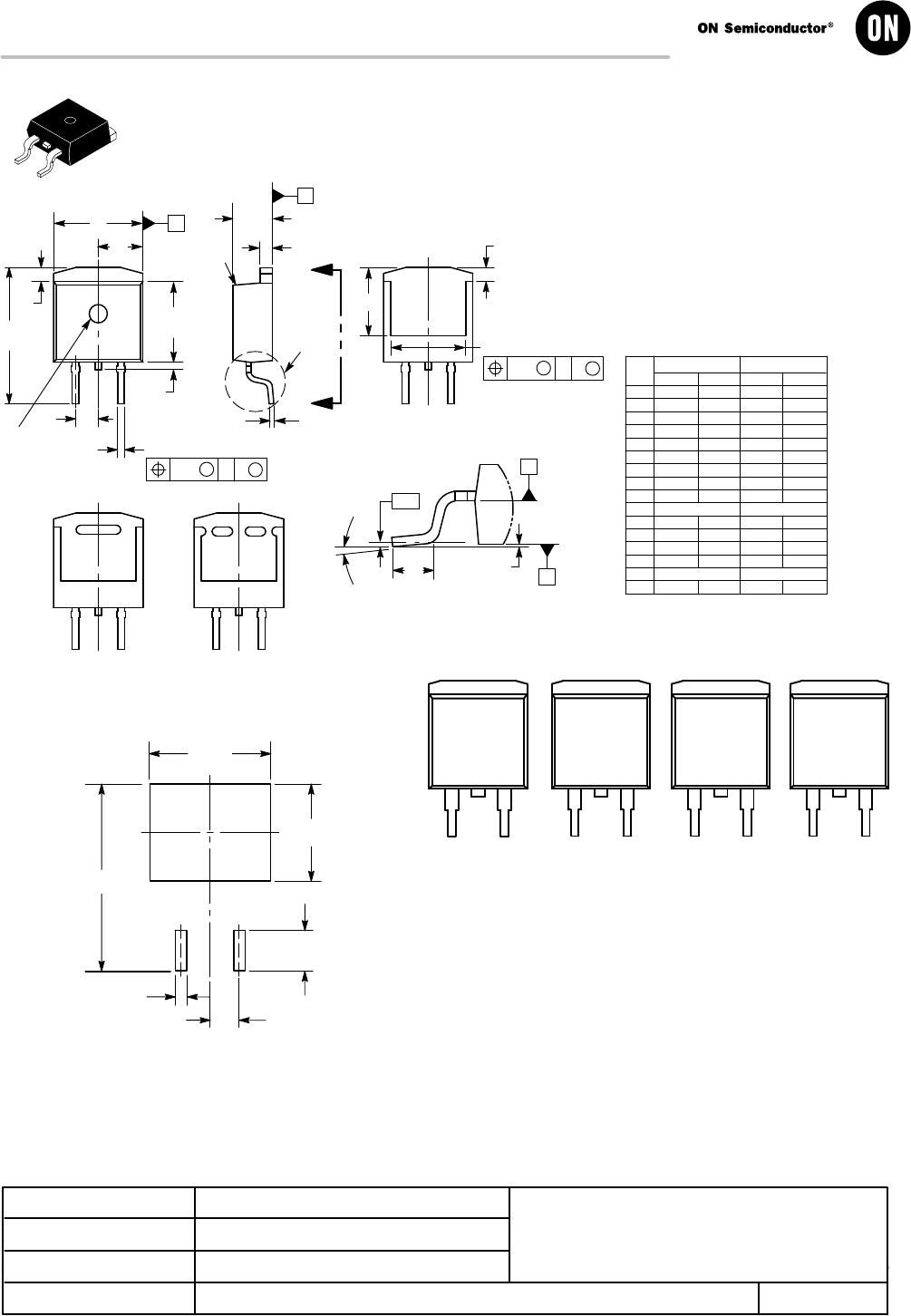

GENERIC MARKING DIAGRAMS*

XXXXXX = Specific Device Code

A = Assembly Location

WL = Wafer Lot

Y = Year

WW = Work Week

W = Week Code (SSG)

M = Month Code (SSG)

G = Pb−Free Package

AKA = Polarity Indicator

IC Standard

XXXXXXXXG

AYWW

*This information is generic. Please refer to

device data sheet for actual part marking.

Pb−Free indicator, “G” or microdot “ G”,

may or may not be present.

Rectifier

AYWW

XXXXXXXXG

AKA

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

RECOMMENDED

0.366

0.100

DIMENSIONS: INCHES

PITCH

2X

0.653

0.063

2X

0.436

0.169

SOLDERING FOOTPRINT*

NOTE 6

SSG

XXXXXX

XXYMW

MECHANICAL CASE OUTLINE

PACKAGE DIMENSIONS

http://onsemi.com

1

© Semiconductor Components Industries, LLC, 2002

October, 2002 − Rev. 0

Case Outline Number:

XXX

DOCUMENT NUMBER:

STATUS:

NEW STANDARD:

DESCRIPTION:

98AON56370E

ON SEMICONDUCTOR STANDARD

D

2

PAK−3 (TO−263, 3−LEAD)

Electronic versions are uncontrolled except when

accessed directly from the Document Repository. Printed

versions are uncontrolled except when stamped

“CONTROLLED COPY” in red.

PAGE 1 OF 2