ZL30123 Data Sheet

15

Zarlink Semiconductor Inc.

Coarse Frequency Monitor (CFM)

The CFM block monitors the reference frequency over a measurement period of 30 μs so that it can quickly detect

large changes in frequency. A CFM failure (cfm_fail) is triggered when the frequency has changed by more than 3%

or approximately 30000 ppm.

Precise Frequency Monitor (PFM)

The PFM block measures the frequency accuracy of the reference over a 10 second interval. To ensure an

accurate frequency measurement, the PFM measurement interval is re-initiated if phase or frequency irregularities

are detected by the SCM or CFM. The PFM provides a level of hysteresis between the acceptance range and the

rejection range to prevent a failure indication from toggling between valid and invalid for references that are on the

edge of the acceptance range.

When determining the frequency accuracy of the reference input, the PFM uses the external oscillator’s output

frequency (f

ocsi

) as its point of reference.

Guard Soak Timer (GST)

The GST block mimics the operation of an analog integrator by accumulating failure events from the CFM and the

SCM blocks and applying a selectable rate of decay when no failures are detected.

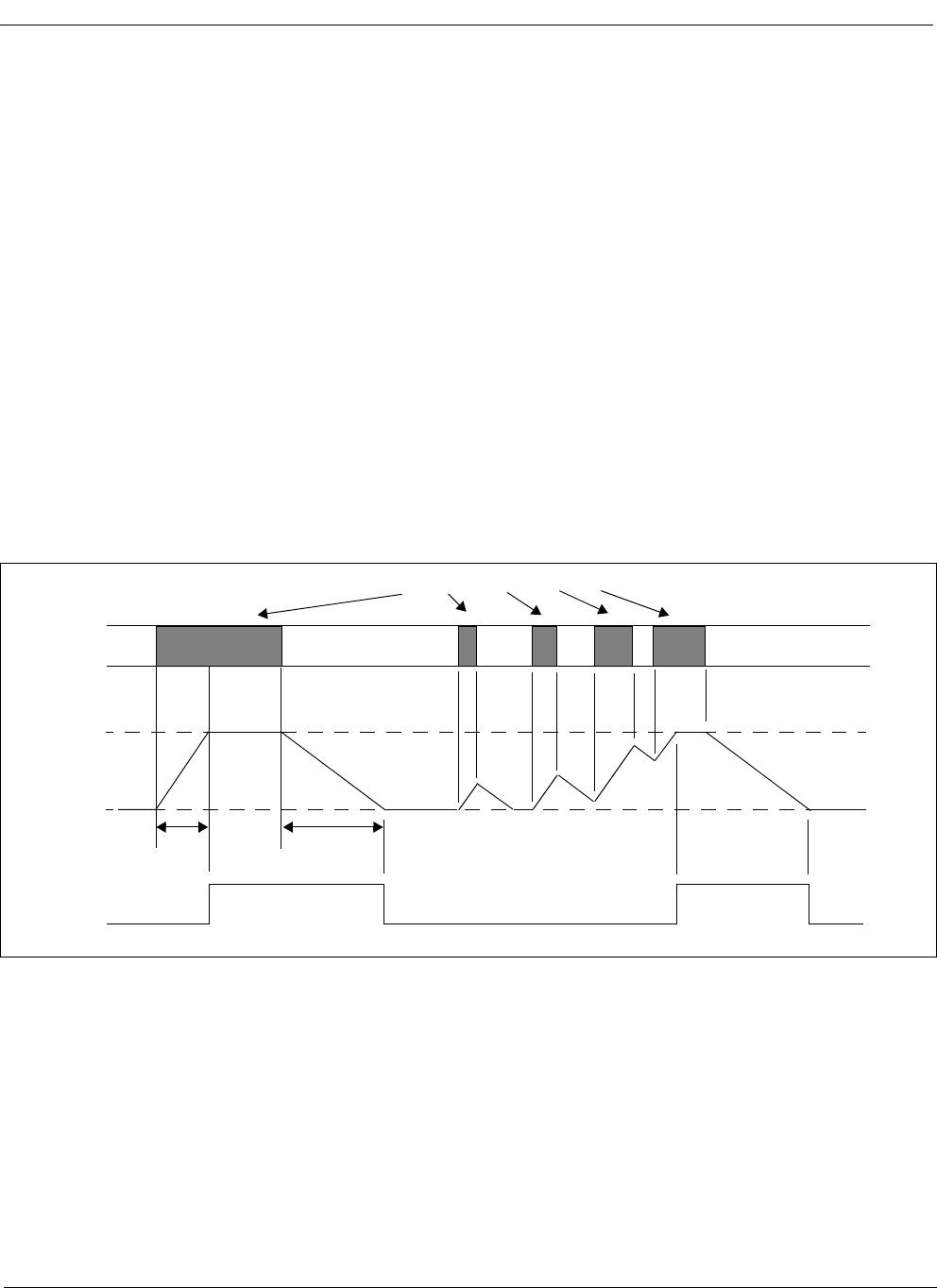

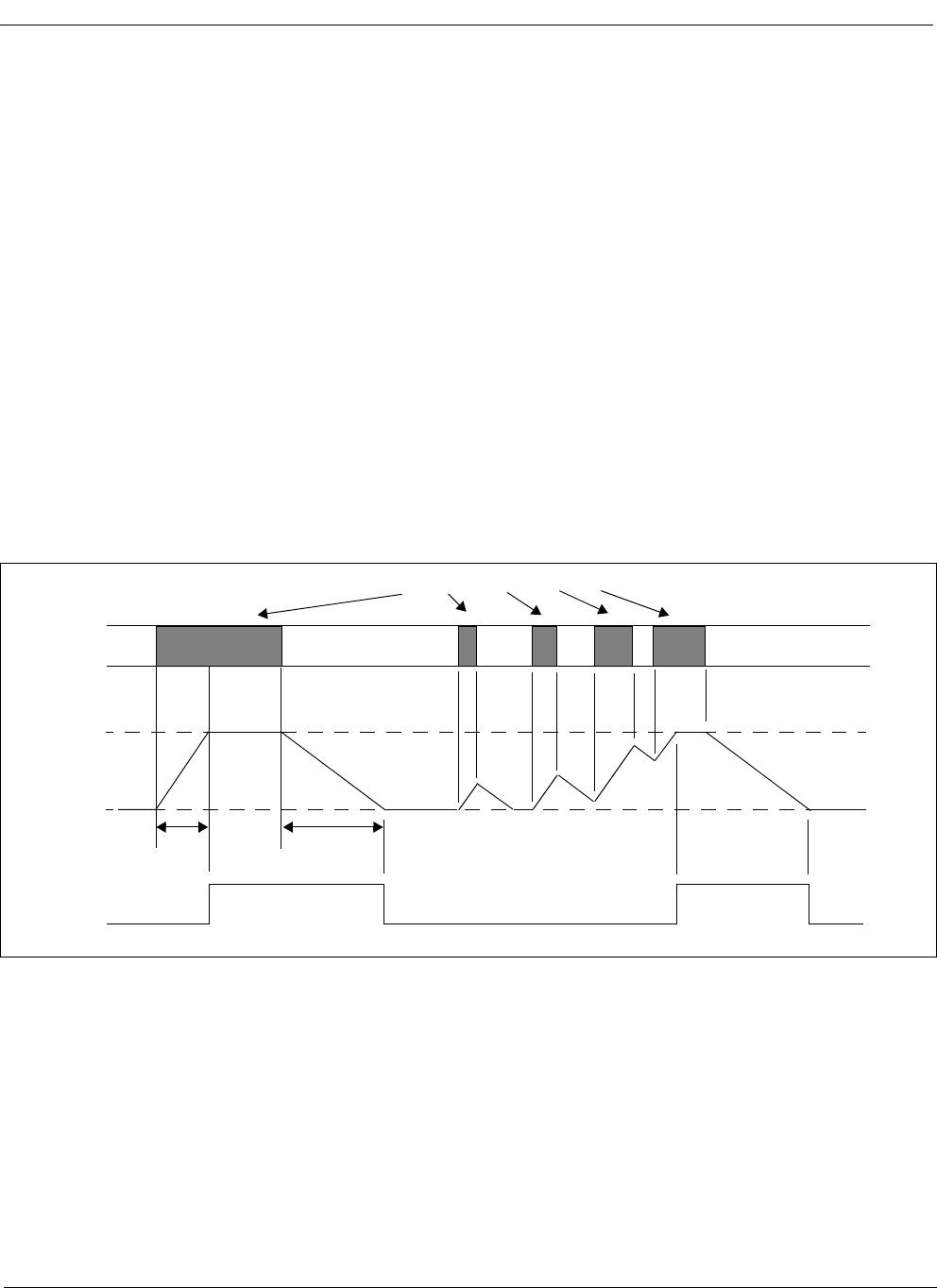

As shown in Figure 5, a GST failure (gst_fail) is triggered when the accumulated failures have reached the upper

threshold during the disqualification observation window. When there are no CFM or SCM failures, the accumulator

decrements until it reaches its lower threshold during the qualification window.

Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM Failures

All sync inputs (sync0 to sync2) are continuously monitored to ensure that there is a correct number of reference

clock cycles within the frame pulse period.

1.5 Output Clocks and Frame Pulses

The ZL30123 offers a wide variety of outputs including two low-jitter differential LVPECL clocks (diff0_p/n,

diff1_p/n), two SONET/SDH LVCMOS (sdh_clk0, sdh_clk1) output clocks and four programmable LVCMOS

(p0_clk0, p0_clk1, p1_clk0, p1_clk1) output clocks. In addition to the clock outputs, two LVCMOS SONET/SDH

frame pulse outputs (sdh_fp0, sdh_fp1) and two LVCMOS programmable frame pulses (p0_fp0, p0_fp1) are also

available.

ref

CFM or SCM failures

upper threshold

lower threshold

t

d

- disqualification time

t

q

- qualification time = n * t

d

t

d

t

q

gst_fail