LTC2601/LTC2611/LTC2621

11

2601fb

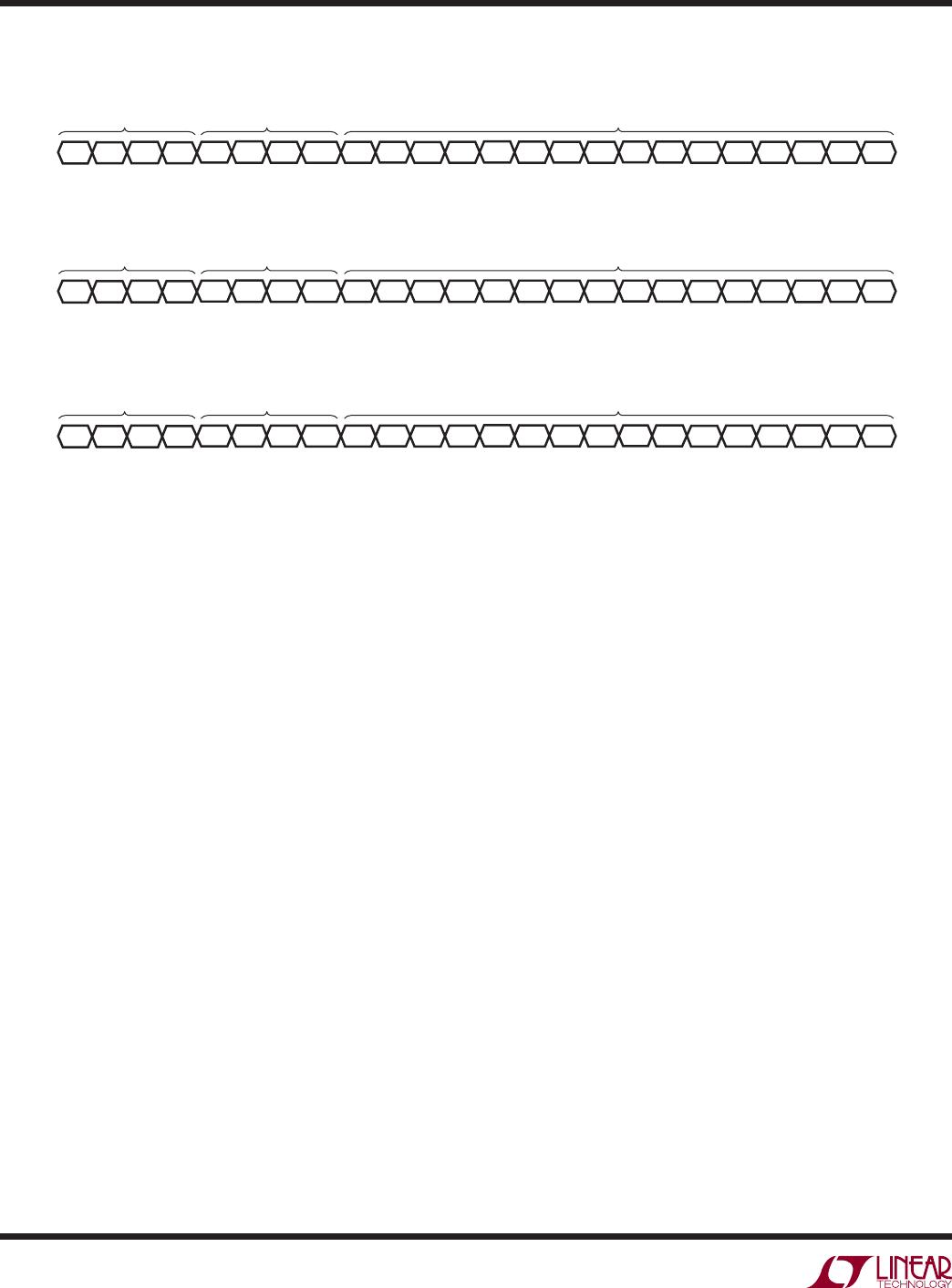

OPERATION

only be transferred to the device when the CS/LD signal

is low.The rising edge of CS/LD ends the data transfer and

causes the device to execute the command specifi ed in

the 24-bit input word. The complete sequence is shown

in Figure 2a.

The command (C3-C0) assignments are shown in Table

1. The fi rst four commands in the table consist of write

and update operations. A write operation loads a 16-bit

data word from the 32-bit shift register into the input

register of the DAC. In an update operation, the data word

is copied from the input register to the DAC register and

converted to an analog voltage at the DAC output. The

update operation also powers up the DAC if it had been in

power-down mode. The data path and registers are shown

in the Block Diagram.

While the minimum input word is 24 bits, it may option-

ally be extended to 32 bits. To use the 32-bit word width,

8 don’t-care bits are transferred to the device fi rst, followed

by the 24-bit word as just described. Figure 2b shows the

32-bit sequence. The 32-bit word is required for daisy-

chain operation, and is also available to accommodate

microprocessors which have a minimum word width of

16 bits (2 bytes).

Daisy-Chain Operation

The serial output of the shift register appears at the SDO

pin. Data transferred to the device from the SDI input is

delayed 32 SCK rising edges before being output at the

next SCK falling edge.

The SDO output can be used to facilitate control of multiple

serial devices from a single 3-wire serial port (i.e., SCK,

SDI and CS/LD). Such a “daisy chain” series is confi gured

by connecting SDO of each upstream device to SDI of the

Power-On Reset

The LTC2601/LTC2611/LTC2621 clear the outputs to zero

scale when power is fi rst applied, making system initializa-

tion consistent and repeatable. The LTC2601-1/LTC2611-

1/LTC2621-1 set the voltage outputs to midscale when

power is fi rst applied.

For some applications, downstream circuits are active

during DAC power-up, and may be sensitive to nonzero

outputs from the DAC during this time. The LTC2601/

LTC2611/LTC2621 contain circuitry to reduce the power-

on glitch; furthermore, the glitch amplitude can be made

arbitrarily small by reducing the ramp rate of the power

supply. For example, if the power supply is ramped to 5V

in 1ms, the analog outputs rise less than 10mV above

ground (typ) during power-on. See Power-On Reset Glitch

in the Typical Performance Characteristics section.

Power Supply Sequencing

The voltage at REF (Pin 6) should be kept within the range

–0.3V ≤ V

REF

≤ V

CC

+ 0.3V (see Absolute Maximum Rat-

ings). Particular care should be taken to observe these

limits during power supply turn-on and turn-off sequences,

when the voltage at V

CC

(Pin 16) is in transition.

Transfer Function

The digital-to-analog transfer function is:

V

k

V

OUT IDEAL

N

REF()

=

⎛

⎝

⎜

⎞

⎠

⎟

2

where k is the decimal equivalent of the binary DAC input

code, N is the resolution and V

REF

is the voltage at REF

(Pin 6).

Serial Interface

The CS/LD input is level triggered. When this input is

taken low, it acts as a chip-select signal, powering-on the

SDI and SCK buffers and enabling the input shift register.

Data (SDI input) is transferred at the next 24 rising SCK

edges. The 4-bit command, C3-C0, is loaded fi rst; then

4 don’t care bits; and fi nally the 16-bit data word. The

data word comprises the 16-, 14- or 12-bit input code,

ordered MSB-to-LSB, followed by 0, 2 or 4 don’t care bits

(LTC2601, LTC2611 and LTC2621 respectively). Data can

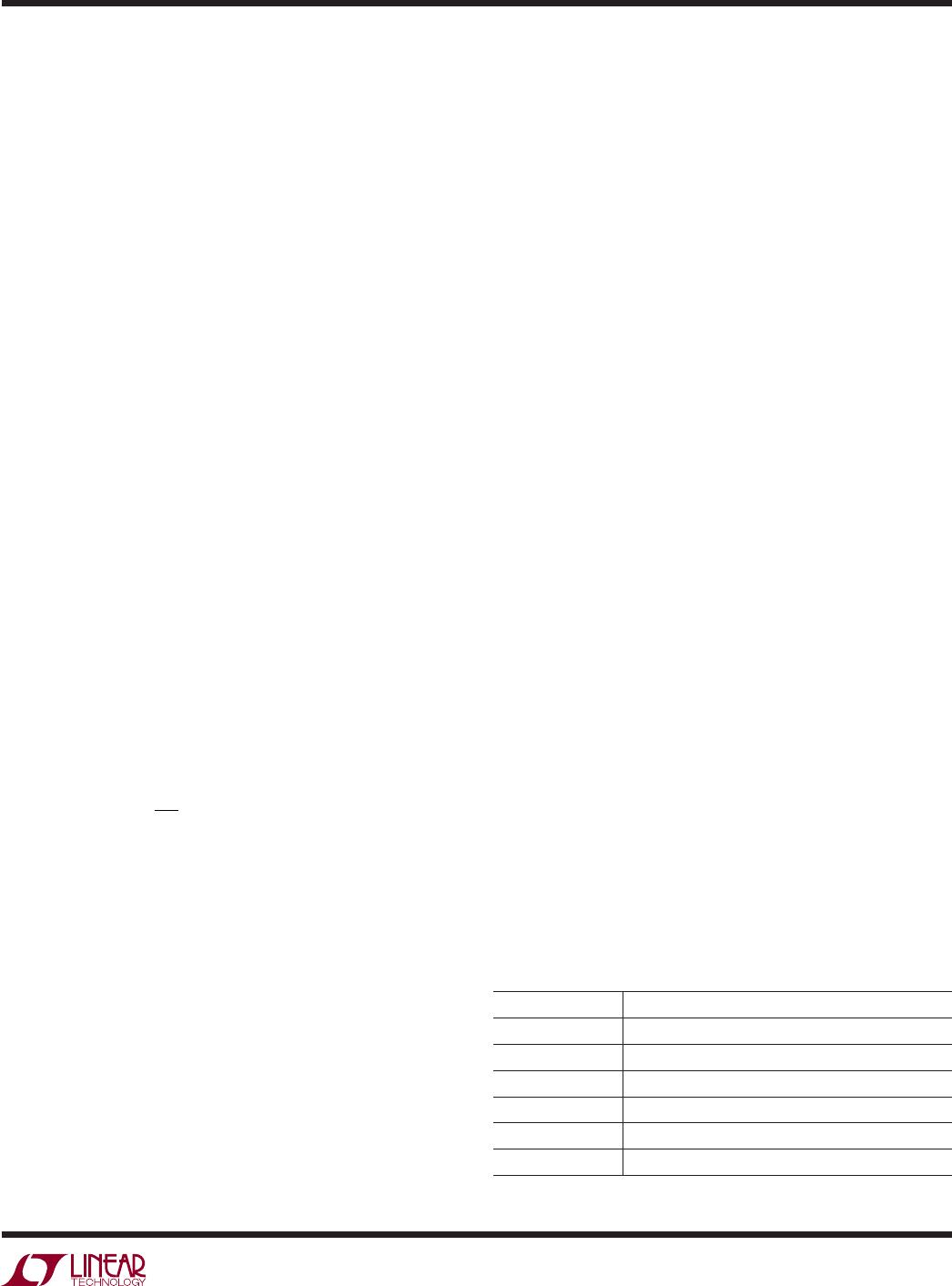

Table 1.

COMMAND*

C3 C2 C1 C0

0 0 0 0 Write to Input Register

0 0 0 1 Update (Power Up) DAC Register

0 0 1 1 Write to and Update (Power Up)

0 1 0 0 Power Down

1 1 1 1 No Operation

*Command codes not shown are reserved and should not be used.