ZL30321 Short Form Data Sheet

3

Zarlink Semiconductor Inc.

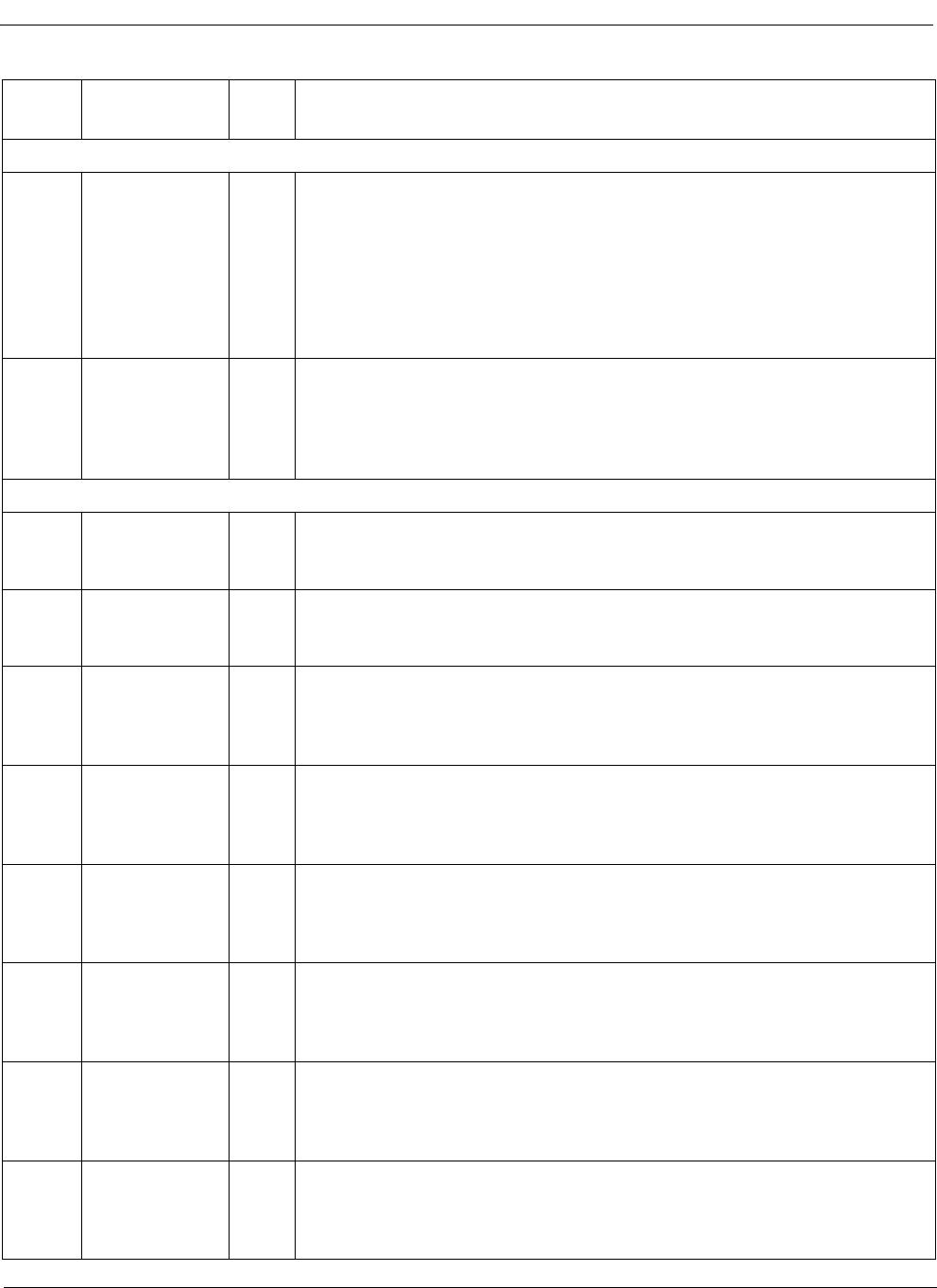

E1 ref_out O DPLL2 Selected Output Reference (LVCMOS). This is a buffered copy of

the output of the reference selector for DPLL2. Switching between input

reference clocks at this output is not hitless.

Control

H5 rst_b I Reset (LVCMOS, Schmitt Trigger). A logic low at this input resets the

device. To ensure proper operation, the device must be reset after power-up.

Reset should be asserted for a minimum of 300 ns.

J5 hs_en I

u

DPLL1 Hitless Switching Enable (LVCMOS, Schmitt Trigger). A logic high

at this input enables hitless reference switching. A logic low disables hitless

reference switching and re-aligns DPLL1’s output phase to the phase of the

selected reference input. This feature can also be controlled through software

registers. This pin is internally pulled up to Vdd.

C2

D2

mod0

mod1

I

u

DPLL1 Mode Select 1:0 (LVCMOS, Schmitt Trigger). During reset, the

levels on these pins determine the default mode of operation for DPLL1

(Automatic, Normal, Holdover or Freerun). After reset, the mode of operation

can be controlled directly with these pins, or by accessing the dpll1_modesel

register (0x1F) through the serial interface. This pin is internally pulled up to

Vdd.

Status

H1 lock O Lock Indicator (LVCMOS). This is the lock indicator pin for DPLL1. This

output goes high when DPLL1’s output is frequency and phase locked to the

input reference.

J1 hold O Holdover Indicator (LVCMOS). This pin goes high when DPLL1 enters the

holdover mode.

Serial Interface

E2 sck_scl I/B Clock for Serial Interface (LVCMOS). Serial interface clock. When i2c_en =

0, this pin acts as the sck pin for the serial interface. When i2c_en = 1, this pin

acts as the scl pin (bidirectional) for the I

2

C interface.

F1 si_sda I/B Serial Interface Input (LVCMOS). Serial interface data pin. When i2c_en = 0,

this pin acts as the si pin for the serial interface. When i2c_en = 1, this pin

acts as the sda pin (bidirectional) for the I

2

C interface.

G1 so O Serial Interface Output (LVCMOS). Serial interface data output. When

i2c_en = 0, this pin acts as the so pin for the serial interface. When i2c_en =

1, this pin is unused and should be left unconnected.

E3 cs_b_asel0 I

u

Chip Select for SPI/Address Select 0 for I

2

C (LVCMOS). When i2c_en = 0,

this pin acts as the chip select pin (active low) for the serial interface. When

i2c_en = 1, this pin acts as the asel0 pin for the I

2

C interface.

F3 asel1 I

u

Address Select 1 for I

2

C (LVCMOS). When i2c_en = 1, this pin acts as the

asel1 pin for the I

2

C interface. Internally pulled up to Vdd. Leave open when

not in use.

F2 asel2 I

u

Address Select 2 for I

2

C (LVCMOS). When i2c_en = 1, this pin acts as the

asel2 pin for the I

2

C interface. Internally pulled up to Vdd. Leave open when

not in use.

100BGA

Pin #

Name

I/O

Type

Description