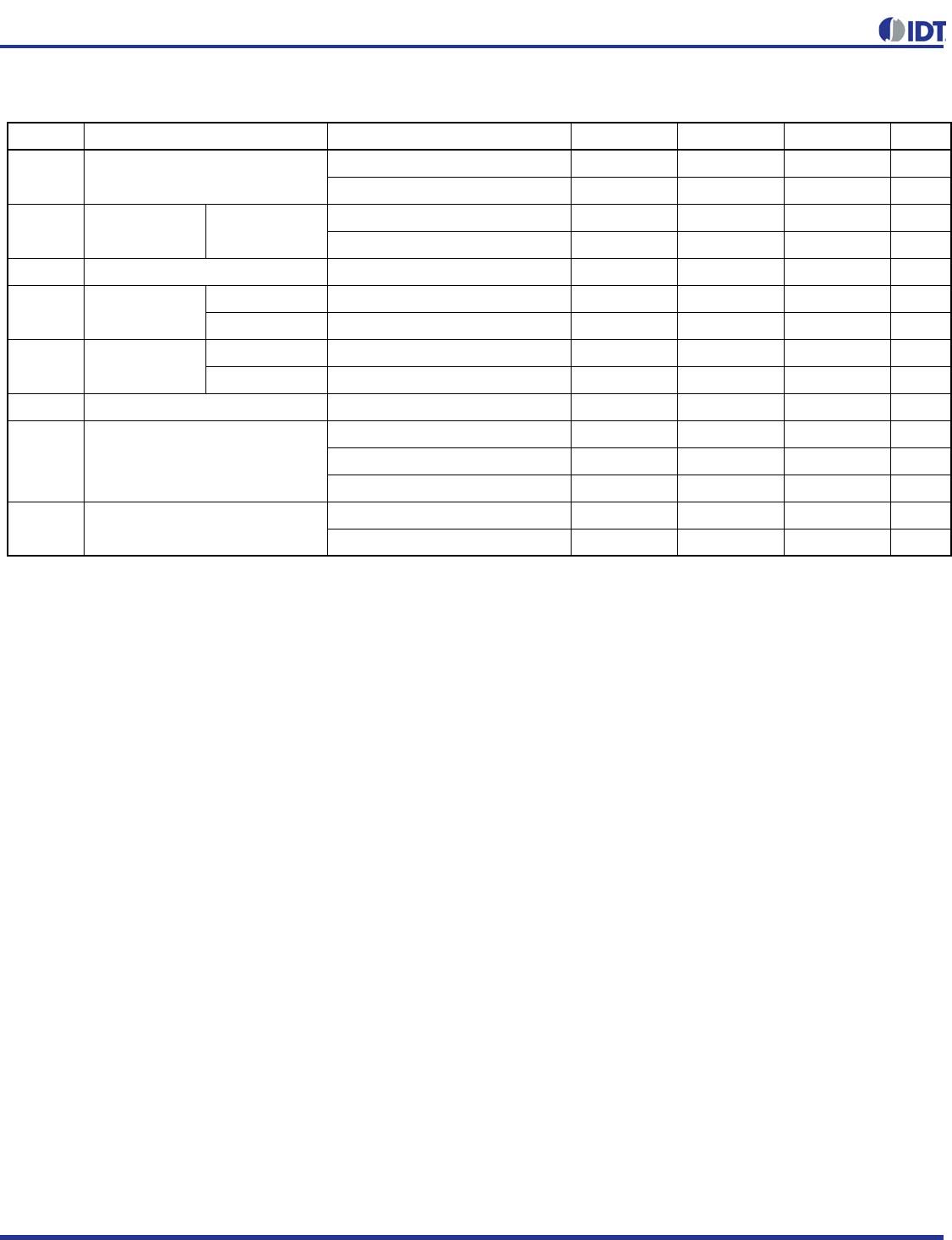

Table 4C. AC Characteristics, V

DD

= 3.3V ±5%, V

DDO

= 1.8V ±0.2V, T

A

= 0°C to 70°C

Test Conditions Minimum Typical Maximum Units

f

OUT

Output Frequency 12 19.44 31.25 MHz

tjit(Ø) RMS Phase Jitter (Random)

1

Integration Range: 1kHz – 1MHz 0.27 ps

tsk(o) Output Skew

2, 3

Q0:Q4 46 ps

Q0:Q5 DIV_SEL_Q5 = ÷1 175 ps

t

R

/ t

F

Output Rise/Fall Time 20% to 80% 450 1400 ps

odc Output Duty Cycle 44 56 %

REVISION B 7/29/16 5 VCXO-TO-6 LVCMOS OUTPUTS

81006 DATA SHEET

AC Characteristics

Table 4A. AC Characteristics, V

DD

= V

DDO

= 3.3V ±5%, T

A

= 0°C to 70°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

f

OUT

Output Frequency 12 19.44 31.25 MHz

tjit(Ø) RMS Phase Jitter (Random)

1

NOTE 1: Refer to the Phase Noise Plot.

Integration Range: 1kHz – 1MHz 0.35 ps

tsk(o) Output Skew

2, 3

NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the output differential

crosspoints.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

Q0:Q4 30 ps

Q0:Q5 DIV_SEL_Q5 = ÷1 100 ps

t

R

/ t

F

Output Rise/Fall Time 20% to 80% 200 700 ps

odc Output Duty Cycle 44 56 %

Table 4B. AC Characteristics, V

DD

= 3.3V ±5%, V

DDO

= 2.5V ±5%, T

A

= 0°C to 70°C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

f

OUT

Output Frequency 12 19.44 31.25 MHz

tjit(Ø) RMS Phase Jitter (Random)

1

NOTE 1: Refer to the Phase Noise Plot.

Integration Range: 1kHz – 1MHz 0.38 ps

tsk(o) Output Skew

2, 3

NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the output differential

crosspoints.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

Q0:Q4 20 ps

Q0:Q5 DIV_SEL_Q5 = ÷1 90 ps

t

R

/ t

F

Output Rise/Fall Time 20% to 80% 300 800 ps

odc Output Duty Cycle 45 55 %

Symbol Parameter

NOTE 1: Refer to the Phase Noise Plot.

NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the output differential

crosspoints.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.