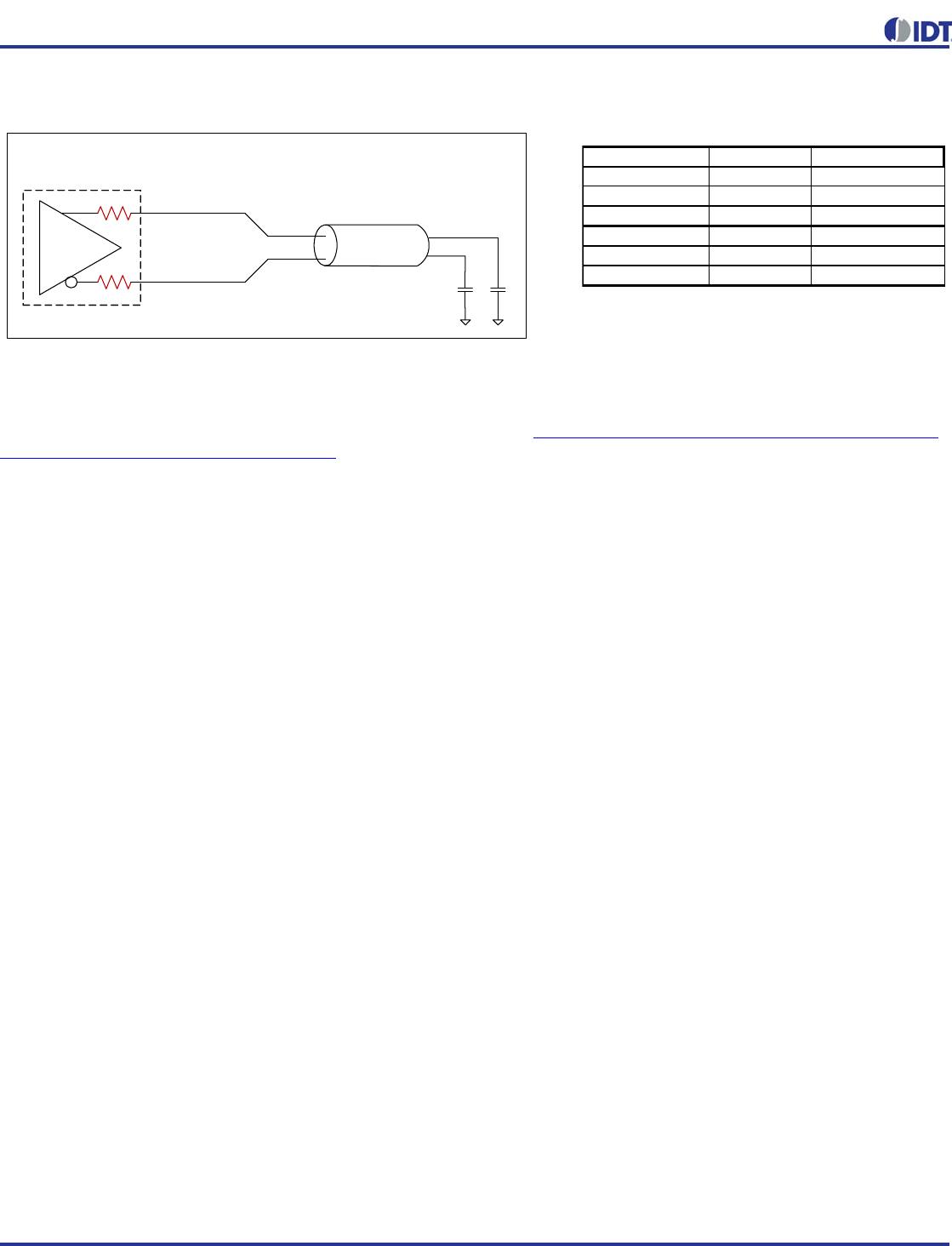

REVISION A 06/06/16 5 2:4 3.3V PCIE CLOCK MUX

9DML04 DATASHEET

Absolute Maximum Ratings

Stresses above the ratings listed below can cause permanent damage to the 9DML04. These ratings, which are standard values

for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions

above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating

conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended

operating temperature range.

Electrical Characteristics–Clock Input Parameters

Electrical Characteristics–Current Consumption

PARAMETER SYMBOL CONDITIONS

MIN TYP MAX

UNITS NOTES

Supply Voltage VDDx 4.6 V 1,2

Input Voltage V

IN

D

+0.5 V 1,3

Input High Voltage, SMBus V

IHSMB

SMBus clock and data pins 3.9 V 1

Storage Temperature Ts -65 150 °C 1

Junction Temperature Tj 125 °C 1

Input ESD protection

ESD prot Human Body Model 2500 V 1

1

Guaranteed by design and characterization, not 100% tested in production.

2

Operation under these conditions is neither implied nor guaranteed.

3

Not to exceed 4.6V.

TA = T

AMB,

Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS NOTES

Input Common Mode

Voltage - DIF_IN

V

COM

Common Mode Input Voltage 150 900 mV 1

Input Swing - DIF_IN V

SWING

Differential value 300 mV 1

Input Slew Rate - DIF_IN dv/dt Measured differentially 0.4 8 V/ns 1,2

Input Leakage Current I

IN

IN

DD ,

IN

GND -5 5 uA

Input Duty Cycle d

tin

Measurement from differential wavefrom 45 55 % 1

Input Jitter - Cycle to Cycle J

DIFIn

Differential Measurement 0 125 ps 1

1

Guaranteed by design and characterization, not 100% tested in production.

2

Slew rate measured through +/-75mV window centered around differential zero

TA = T

AMB,

Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS NOTES

Operating Supply Current

I

D

VDD, All outputs active @100MHz

23 30

mA

Powerdown Current

I

DDPD

VDD, all outputs disabled 1.6 2.5 mA

1

1

Input clock stopped.