AD1674–SPECIFICATIONS

AC SPECIFICATIONS

AD1674J/A AD1674K/B/T

Parameter Min Typ Max Min Typ Max Units

Signal to Noise and Distortion (S/N+D) Ratio

2, 3

69 70 70 71 dB

Total Harmonic Distortion (THD)

4

–90 –82 –90 –82 dB

0.008 0.008 %

Peak Spurious or Peak Harmonic Component –92 –82 –92 –82 dB

Full Power Bandwidth 1 1 MHz

Full Linear Bandwidth 500 500 kHz

Intermodulation Distortion (IMD)

5

Second Order Products –90 –80 –90 –80 dB

Third Order Products –90 –80 –90 –80 dB

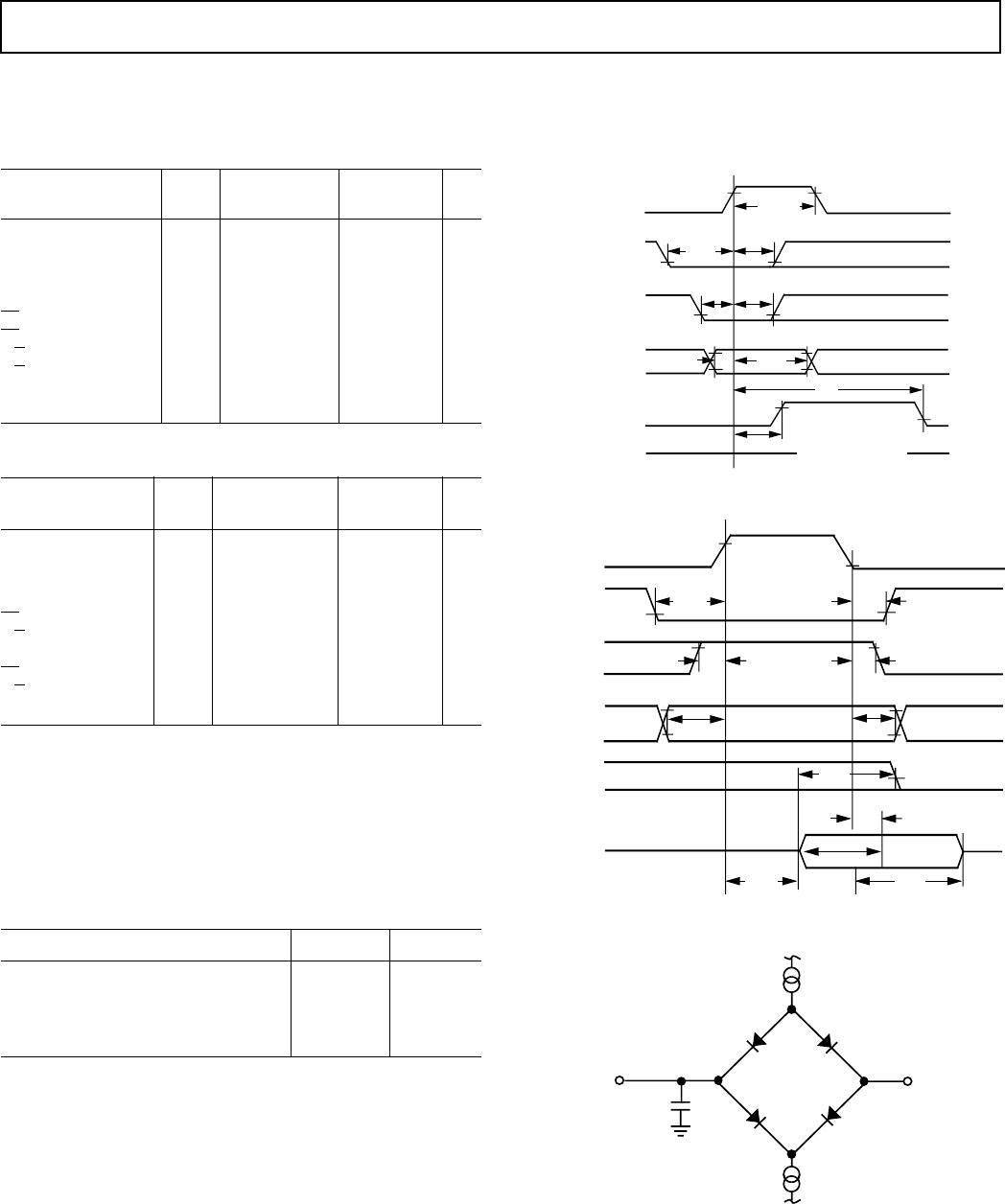

SHA (Specifications are Included in Overall Timing Specifications)

Aperture Delay 50 50 ns

Aperture Jitter 250 250 ps

Acquisition Time 1 1 µs

DIGITAL SPECIFICATIONS

Parameter Test Conditions Min Max Units

LOGIC INPUTS

V

IH

High Level Input Voltage +2.0 V

LOGIC

+0.5 V V

V

IL

Low Level Input Voltage –0.5 +0.8 V

I

IH

High Level Input Current (V

IN

= 5 V) V

IN

= V

LOGIC

–10 +10 µA

I

IL

Low Level Input Current (V

IN

= 0 V) V

IN

= 0 V –10 +10 µA

C

IN

Input Capacitance 10 pF

LOGIC OUTPUTS

V

OH

High Level Output Voltage I

OH

= 0.5 mA +2.4 V

V

OL

Low Level Output Voltage I

OL

= 1.6 mA +0.4 V

I

OZ

High-Z Leakage Current V

IN

= 0 to V

LOGIC

–10 +10 µA

C

OZ

High-Z Output Capacitance 10 pF

NOTES

1

f

IN

amplitude = –0.5 dB (9.44 V p-p) 10 V bipolar mode unless otherwise noted. All measurements referred to –0 dB (9.997 V p-p) input signal unless

otherwise noted.

2

Specified at worst case temperatures and supplies after one minute warm-up.

3

See Figures 12 and 13 for other input frequencies and amplitudes.

4

See Figure 11.

5

fa = 9.08 kHz, fb = 9.58 kHz with f

SAMPLE

= 100 kHz. See Definition of Specifications section and Figure 15.

All min and max specifications are guaranteed.

Specifications subject to change without notice.

–4–

REV. C

(T

MIN

to T

MAX

, with V

CC

= +15 V 6 10% or +12 V 6 5%, V

LOGIC

= +5 V 6 10%, V

EE

= –15 V 610% or

–12 V 6 5%, f

SAMPLE

= 100 kSPS, f

IN

= 10 kHz, stand-alone mode unless otherwise noted)

1

(for all grades T

MIN

to T

MAX

, with V

CC

= +15 V 6 10% or +12 V 6 5%, V

LOGIC

= +5 V 6 10%,

V

EE

= –15 V 6 10% or –12 V 6 5%)