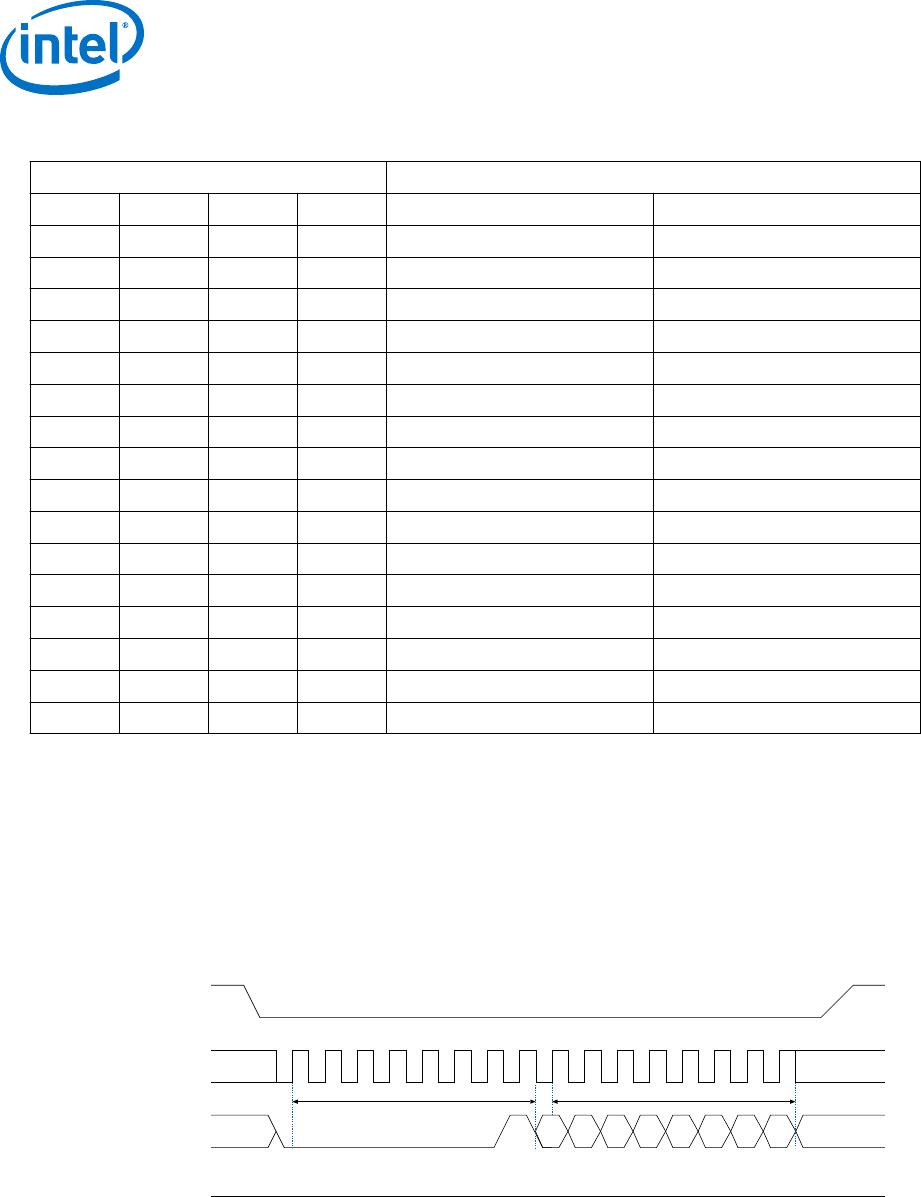

Table 21. Block Protection Bits in EPCQ128A

Status Register Content Memory Content

TB Bit BP2 Bit BP1 Bit BP0 Bit Protected Area Unprotected Area

0 0 0 0 None All sectors

0 0 0 1 Sectors (252 to 255) Sectors (0 to 251)

0 0 1 0 Sectors (248 to 255) Sectors (0 to 247)

0 0 1 1 Sectors (240 to 255) Sectors (0 to 239)

0 1 0 0 Sectors (224 to 255) Sectors (0 to 223)

0 1 0 1 Sectors (192 to 255) Sectors (0 to 191)

0 1 1 0 Sectors (128 to 255) Sectors (0 to 127)

0 1 1 1 All sectors None

1 0 0 0 None All sectors

1 0 0 1 Sectors (0 to 3) Sectors (4 to 255)

1 0 1 0 Sectors (0 to 7) Sectors (8 to 255)

1 0 1 1 Sectors (0 to 15) Sectors (16 to 255)

1 1 0 0 Sectors (0 to 31) Sectors (32 to 255)

1 1 0 1 Sectors (0 to 63) Sectors (64 to 255)

1 1 1 0 Sectors (0 to 127) Sectors (128 to 255)

1 1 1 1 All sectors None

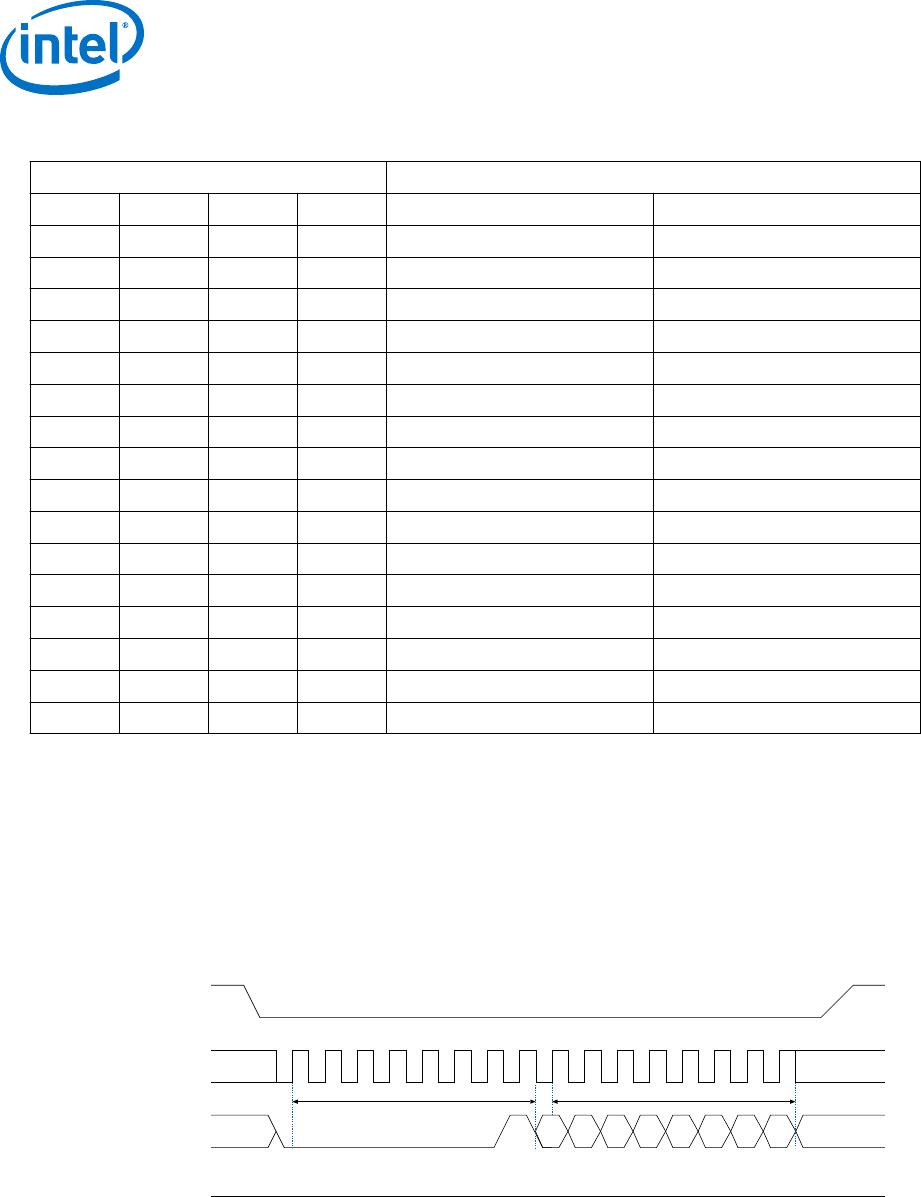

1.8.2. Write Status Operation

The write status operation does not affect the write enable latch and write in progress

bits. You can use the write status operation to set the status register block protection

and top or bottom bits. Therefore, you can implement this operation to protect certain

memory sectors. After setting the block protect bits, the protected memory sectors

are treated as read-only memory. You must execute the write enable operation before

the write status operation.

Figure 5. Write Status Operation Timing Diagram

Operation Code (01h) Status Register

DATA0

nCS

DCLK

DATA

High Impedance

0

1

2

3

4

5

6

7

8 9 10 11 12 13 14 15

0

1

2

3

4

5

6

7

MSB

Immediately after the nCS signal drives high, the device initiates the self-timed write

status cycle. The self-timed write status cycle usually takes 10 ms for all EPCQ-A

devices and is guaranteed to be less than 15 ms. For details about t

WS

, refer to the

related information below. You must account for this delay to ensure that the status

register is written with the desired block protect bits. Alternatively, you can check the

1. EPCQ-A Serial Configuration Device Datasheet

CF52014 | 2018.04.11

EPCQ-A Serial Configuration Device Datasheet

20