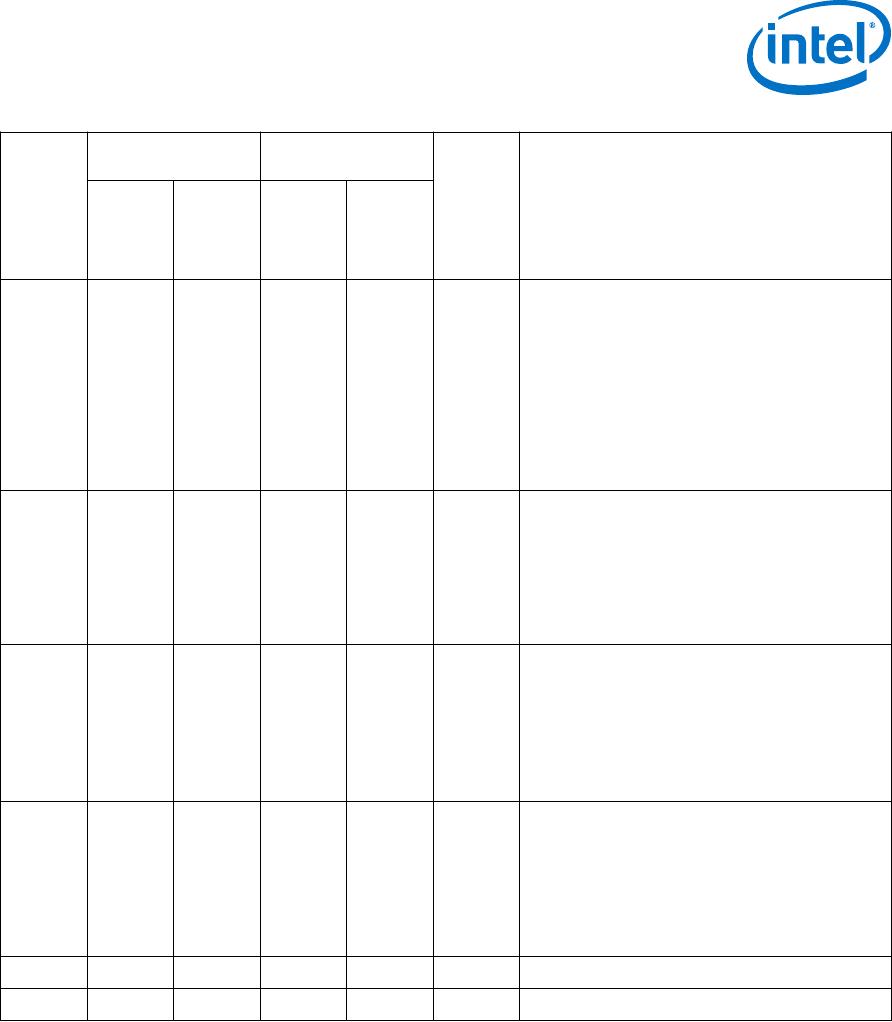

1.4.3. EPCQ-A Device Pin Description

Table 8. EPCQ-A Device Pin Description

Pin Name AS x1 Pin-Out

Diagram

AS x4 Pin-Out

Diagram

Pin Type Description

Pin

Number

in 8-Pin

SOIC

Package

Pin

Number

in 16-Pin

SOIC

Package

Pin

Number

in 8-Pin

SOIC

Package

Pin

Number

in 16-Pin

SOIC

Package

DATA0

5 15 5 15 I/O For AS x1 mode, use this pin as an input signal

pin to write or program the EPCQ-A device.

During write or program operations, data are

latched at rising edges of the DCLK signal. This

pin is equivalent to the ASDI pin in EPCS devices.

For AS x4 mode, use this pin as an I/O signal pin.

During write or program operations, this pin acts

as an input pin that serially transfers data into

the EPCQ-A device. The data are latched at rising

edges of the DCLK signal. During read or

configuration operations, this pin acts as an

output signal pin that serially transfers data out

of the EPCQ-A device to the FPGA. The data is

shifted out at falling edges of the DCLK signal.

During the quad input fast write bytes operation,

this pin acts as an input pin that serially transfers

data into the EPCQ-A device. The data is latched

at rising edges of the DCLK signal. During

extended dual input fast read or extended quad

input fast read operations, this pin acts as an

output signal pin that serially transfers data out

of the EPCQ-A device to the FPGA. The data is

shifted out at falling edges of the DCLK signal.

DATA1

2 8 2 8 I/O For AS x1 and x4 modes, use this pin as an

output signal pin that serially transfers data out

of the EPCQ-A device to the FPGA during read or

configuration operations. The transition of the

signal is at falling edges of the DCLK signal. This

pin is equivalent to the DATA pin in EPCS devices.

During the quad input fast write bytes operation,

this pin acts as an input signal pin that serially

transfers data into the EPCQ-A device. The data is

latched at rising edges of the DCLK signal.

During extended quad input fast read operations,

this pin acts as an output signal pin that serially

transfer data out of the EPCQ-A device to the

FPGA. The data is shifted out at falling edges of

the DCLK signal. During read, configuration, or

program operations, you can enable the EPCQ-A

device by pulling the nCS signal low.

DATA2

— — 3 9 I/O For AS x1 mode, this pin must connect to V

CC

.

For AS x4 mode, use this pin as an output signal

that serially transfers data out of the EPCQ-A

device to the FPGA during read or configuration

operations. The transition of the signal is at

falling edges of the DCLK signal.

During the extended quad input fast read

operation, this pin acts as an output signal pin

that serially transfers data out of the EPCQ-A

device to the FPGA. The data is shifted out at

falling edges of the DCLK signal.

continued...

1. EPCQ-A Serial Configuration Device Datasheet

CF52014 | 2018.04.11

EPCQ-A Serial Configuration Device Datasheet

8