LTC2941-1

11

29411f

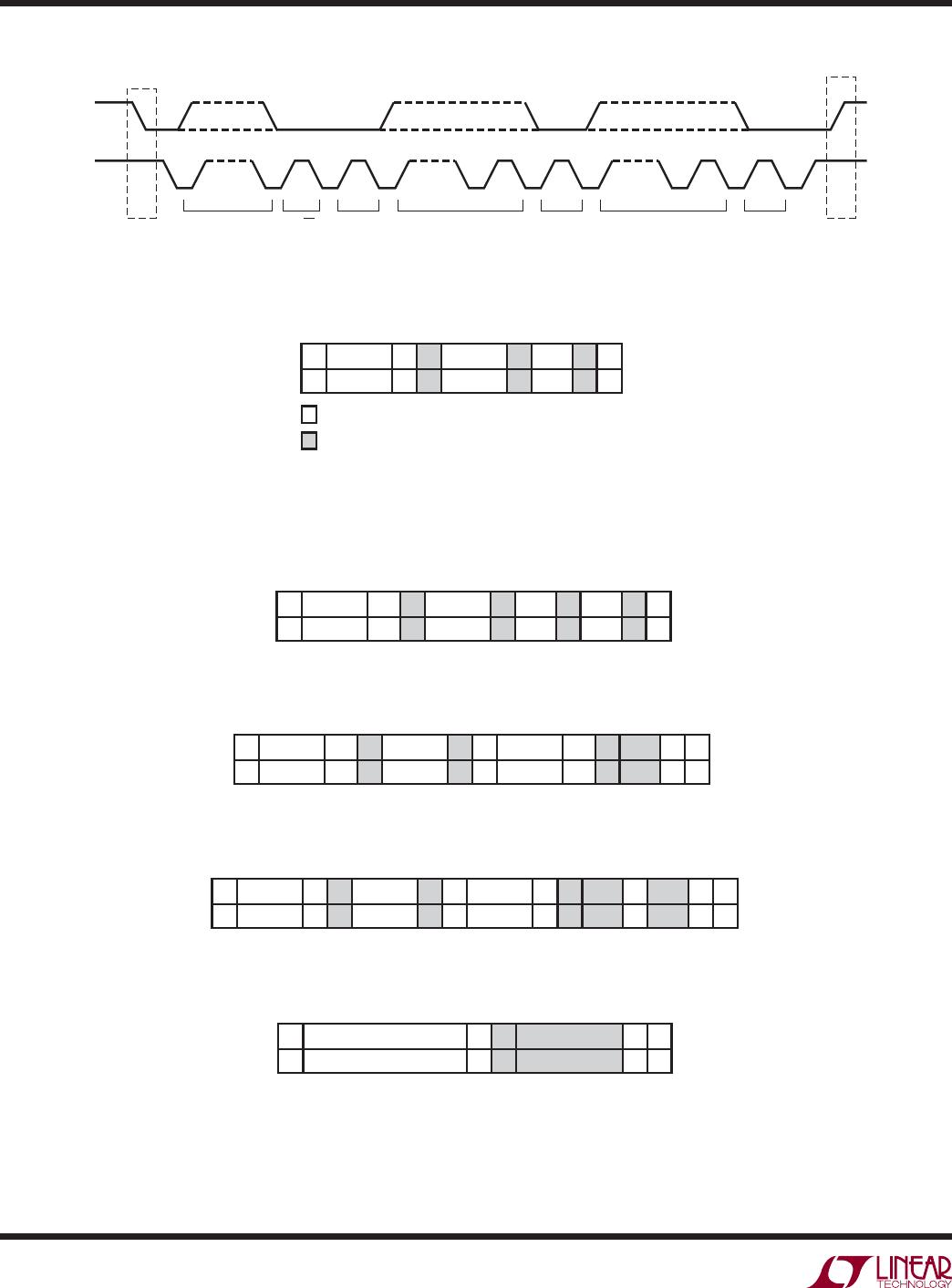

device. In addition to transmitters and receivers, devices

can also be classified as masters or slaves when perform-

ing data transfers. A master is the device which initiates a

data transfer on the bus and generates the clock signals

to permit that transfer. At the same time any device ad-

dressed is considered a slave. The LTC2941-1 always

acts as a slave. Figure 4 shows an overview of the data

transmission on the I

2

C bus.

Start and Stop Conditions

When the bus is idle, both SCL and SDA must be high. A

bus master signals the beginning of a transmission with

a START condition by transitioning SDA from high to low

while

SCL

is high. When the master has finished com-

municating with the slave, it issues a STOP condition by

transitioning SDA from low to high while SCL is high. The

bus is then free for another transmission. When the bus is

in use, it stays busy if a repeated START (Sr) is generated

instead of a STOP condition. The repeated START (Sr)

conditions are functionally identical to the START (S).

Data Transmission

After a START condition, the I

2

C bus is considered busy

and data transfer begins between a master and a slave. As

data is transferred over I

2

C in groups of nine bits (eight

data bits followed by an acknowledge bit), each group

takes nine SCL cycles. The transmitter releases the SDA

line during the acknowledge clock pulse and the receiver

issues an acknowledge (ACK) by pulling SDA low or leaves

SDA high to indicate a not-acknowledge (NAK) condition.

Change of data state can only happen while SCL is low.

Write Protocol

The master begins communication with a START condition

followed by the seven bit slave address 1100100 and the

R/W bit set to zero, as shown in Figure 5. The LTC2941-

1 acknowledges this by pulling SDA low and then the

master sends a command byte which indicates which

internal register the master is to write. The LTC2941-1

acknowledges and then latches the command byte into its

internal register address pointer. The master delivers the

data byte, the LTC2941-1 acknowledges once more and

latches the data into the desired register. The transmission

is ended when the master sends a STOP condition. If the

master continues by sending a second data byte instead

of a stop, the LTC2941-1 acknowledges again, increments

its address pointer and latches the second data byte in the

following register, as shown in Figure 6.

Read Protocol

The master begins a read operation with a START condition

followed by the seven bit slave address 1100100 and the

R/W bit set to zero, as shown in Figure 7. The LTC2941-1

acknowledges and then the master sends a command byte

which indicates which internal register the master is to

read. The LTC2941-1 acknowledges and then latches the

command byte into its internal register address pointer. The

master then sends a repeated START condition followed

by the same seven bit address with the R/W bit now set

to one. The LTC2941-1 acknowledges and sends the con-

tents of the requested register. The transmission is ended

when the master sends a STOP condition. If the master

acknowledges the transmitted data byte, the LTC2941-1

increments its address pointer and sends the contents of

the following register as shown in Figure 8.

Alert Response Protocol

In a system where several slaves share a common inter-

rupt line, the master can use the alert response address

(ARA) to determine which device initiated the interrupt

(Figure 9).

The master initiates the ARA procedure with a START con-

dition and the special 7-bit ARA bus address (0001100)

followed by the read bit (R) = 1. If the LTC2941-1 is as-

serting the AL/CC pin in alert mode, it acknowledges and

responds by sending its 7-bit bus address (1100100) and

a 1. While it is sending its address, it monitors the SDA pin

to see if another device is sending an address at the same

time using standard I

2

C bus arbitration. If the LTC2941-1

is sending a 1 and reads a 0 on the SDA pin on the rising

edge of SCL, it assumes another device with a lower ad-

dress is sending and the LTC2941-1 immediately aborts

its transfer and waits for the next ARA cycle to try again.

If transfer is successfully completed, the LTC2941-1 will

stop pulling down the AL/CC pin and will not respond to

further ARA requests until a new alert event occurs.

applicaTions inFormaTion