LTC2941-1

13

29411f

applicaTions inFormaTion

Internal Sense Resistor

The internal sense resistor uses proprietary* tempera-

ture compensation techniques to reduce the effective

temperature coefficient to less than ±50ppm/K typically.

The effective sense resistance as seen by the coulomb

counter is factory trimmed to 50mΩ. Both measures,

and the lack of thermocouple effects in the sense resis-

tor connections, contribute to the LTC2941-1’s superior

charge measurement accuracy compared to competing

solutions employing a common 1% tolerance, 50ppm/K

tempco discrete current sense resistor.

Like all sense resistors, the integrated sense resistor in

the LTC2941-1 will exhibit minor long-term resistance

shift. The resistance typically drops less than –0.1% per

1000h at 1A current and 85°C ambient temperature; this

outperforms most types of discrete sense resistors except

those of the very high and ultrahigh stability variety. See

the Typical Performance Characteristics for expected

resistor drift performance under worst-case conditions.

Drift will be much slower at lower temperatures. Contact

LTC applications for more information.

For most coulomb counter applications this aging behavior

of the integrated sense resistor is insignificant compared

to the change of battery capacity due to battery aging.

The LTC2941-1 is factory trimmed to optimum accuracy

when new; for applications which require the best possible

coulomb count accuracy over the full product lifetime, the

coulomb counter gain can be adjusted in software. For

instance, if the error contribution of sense resistor drift

must be limited to ±1%, coulomb counts may be biased

high by 1% (use factor 1.01), and maximum operational

temperature and current then must be derated such that

sense resistor drift over product lifetime or calibration

intervals is less than –2%.

Applications employing the standard external resistor

LTC2941 with an external 50mΩ sense resistor may be

upgraded to the pin compatible LTC2941-1 by removing

the external sense resistor.

Voltage Drop Between SENSE

+

and SENSE

–

The LTC2941-1 is trimmed for an effective internal resis-

tance of 50mΩ , but the total pin-to-pin resistance (R

PP

),

consisting of the sense resistor in series with pin and bond

wire resistances, is somewhat higher. Assuming a sense

resistor temperature coefficient of about 3900ppm/K, the

total resistance between SENSE

+

and SENSE

–

at a tem-

perature, T , is typically:

R

PP

(T) = R

PP

(T

NOM

) [1 + 0.0039(T – T

NOM

)]

where T

NOM

= 27°C (or 300K) and R

PP

(T

NOM

) is from the

Electrical Characteristics table. This means that the resis-

tance between SENSE

+

and SENSE

–

may drop by 26% if die

temperature changes from 27°C to –40°C or increase by

23% for a 27°C to 85°C die temperature change. Ensure that

total voltage drop between SENSE

+

and SENSE

–

, caused

by maximum peak current flowing in/out of SENSE

–

:

V

DROP

= I

PEAK

• R

PP

(T

DIE(MAX)

)

does not exceed the application’s requirements .

Limiting Inrush Current

Inrush currents during events like battery insertion or

closure of a mechanical power switch may be substan-

tially higher than peak currents during normal operation.

Extremely large inrush currents may require additional

circuitry to keep currents through the LTC2941-1 sense

resistor below the absolute maximum ratings.

Note that external Schottky clamp diodes between SENSE

+

and SENSE

–

can leak significantly, especially at high tem-

perature, which can cause significant coulomb counter

errors. Preferred solutions to limit inrush current include

active Hot Swap™ current limiting or connector designs

that include current limiting resistance and staggered pins

to ensure a low impedance connection when the connector

is fully mated.

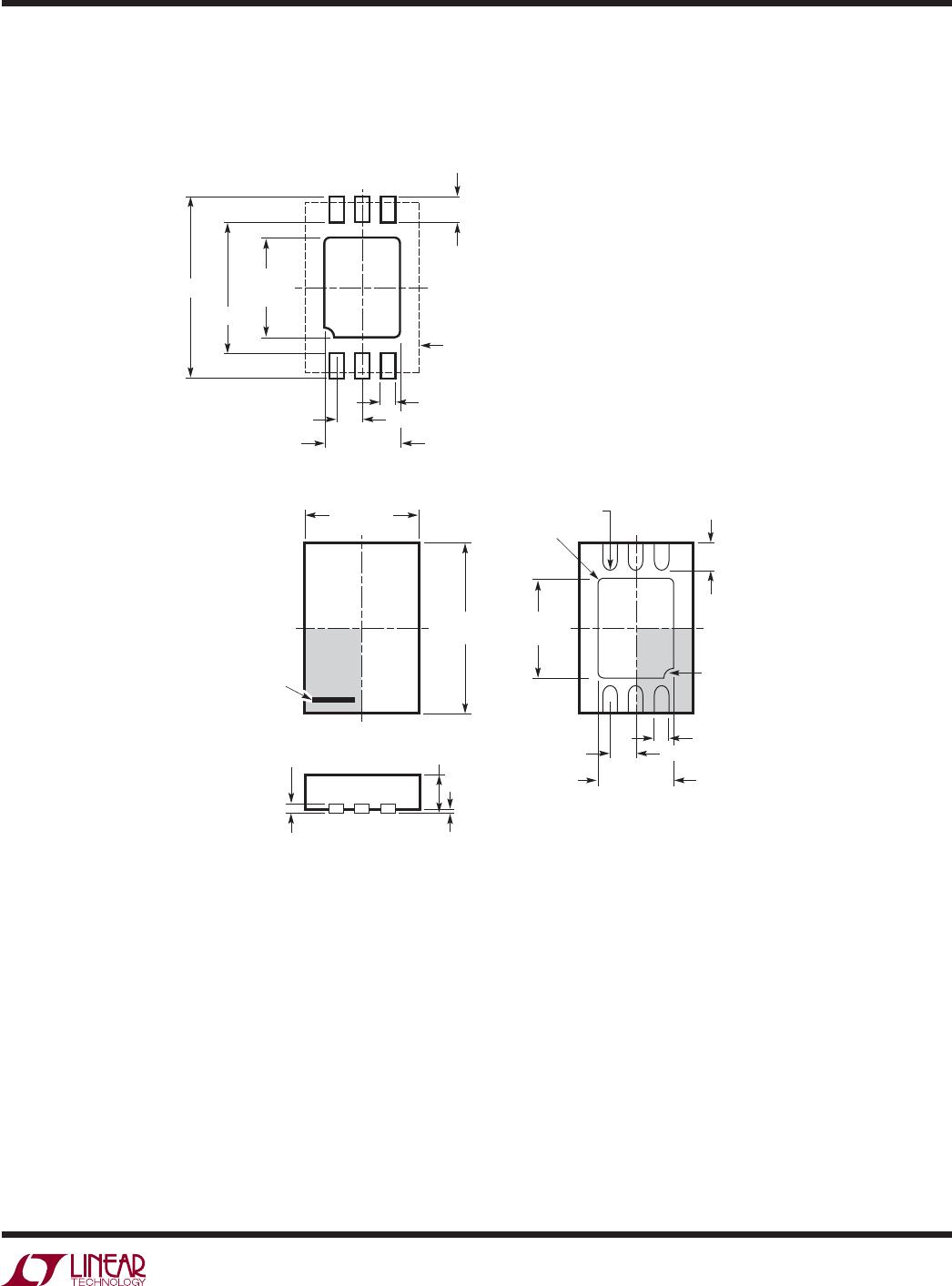

Power Dissipation

Power dissipation in the R

PP

resistance when operated

at high currents can increase the die temperature sev-

eral degrees over ambient. Soldering the exposed pad

of the DFN package to a large copper region on the PCB

is recommended for applications operating close to the

specified maximum current and ambient temperature. Die

temperature at a given I

SENSE

can be estimated by:

T

DIE

= T

AMB

+ 1.22 • θ

JA

• R

PP(MAX)

• I

SENSE

2

*Patent pending.