LTC6240/LTC6241/LTC6242

22

624012fe

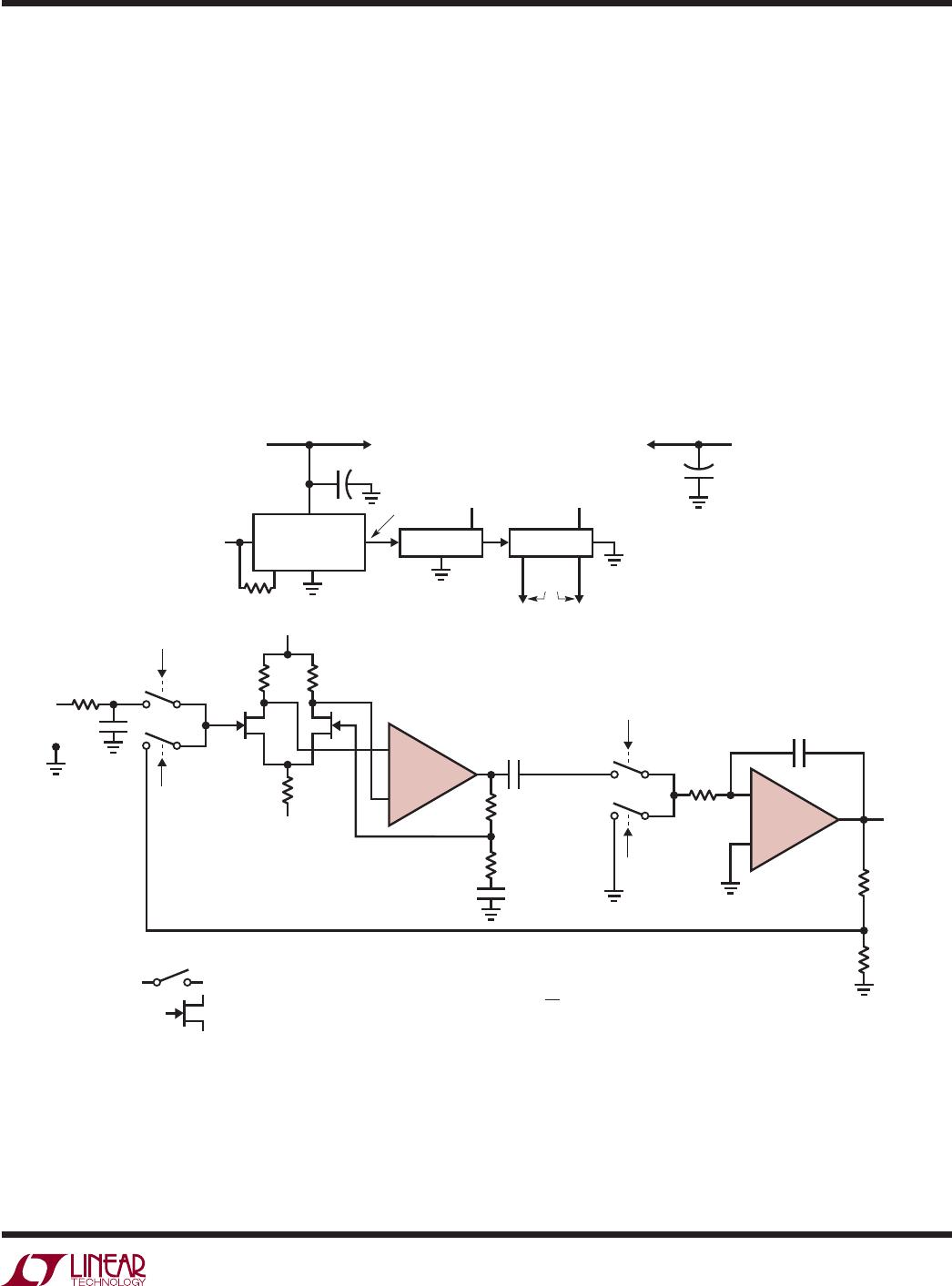

Figure 8. Wideband Difference Amplifi er with High

Input Impedance and Digitally Programmable Gain

The low bias current and current noise of the LTC6241

allow the use of high valued input resistors, 100k or

greater. Resistors R1, R2, R3 and R4 are equal and the

gain of the difference amplifi er is one. An LTC6910-2 PGA

amplifi es the difference amplifi er output with inverting

gains of –1, –2, –4, –8, –16, –32 and –64. The second

LTC6241 op amp is used as an integrator to set the DC

output voltage equal to the LT6650 reference voltage V

REF

.

The integrator drives the PGA analog ground to provide

a feedback loop, in addition to blocking any DC voltage

through the PGA. The reference voltage of the LT6650

can be set to a voltage from 400mV to V

+

– 350mV with

resistors R5 and R6. If R6 is 20k or less, the error due

to the LT6650 op amp bias current is negligible. The low

voltage offset and drift of the LTC6241 integrator will not

contribute any signifi cant error to the LT6650 reference

voltage. The LT6650 V

REF

voltage has a maximum error

of ±2% with 1% resistors. The upper –3dB frequency of

the amplifi er is set by resistor R3 and capacitor C1 and

is limited by the bandwidth of the PGA when operated at

a gain of 64. Capacitor C2 is equal to C1 and is added to

maintain good common mode rejection at high frequency.

The lower –3dB frequency is set by the integrator resistor

R7, capacitor C3, and the gain setting of the LTC6910-2

PGA. This lower –3dB zero frequency is multiplied by the

PGA gain. The rail-to-rail output of the LTC6910-2 PGA

allows for a maximum output peak-to-peak voltage equal

to twice the V

REF

voltage. At the maximum gain setting of

64, the maximum peak-to-peak difference between inputs

V1 and V2 is equal to twice V

REF

divided by 64.

Example Design: Design a programmable gain AC differ-

ence amplifi er, with a bandwidth of at least 10Hz to 100kHz,

an input impedance equal to or greater than 100k, and

an output DC reference equal to 1V.

a. Select input resistors R1, R2, R3 and R4 equal to

100k.

b. If the upper –3dB frequency is 100kHz then C1 = 1/(2π

• R2 • f3dB) = 1/(6.28 • 100k • 100kHz) = 15pF (to

the nearest 5% value) and C2 = C1 = 15pF.

c. Select R7 equal to one 1M and set the lower –3dB

frequency to 10Hz at the highest PGA gain of 64, then

C3 = Gain/(2π • R7 • f3dB) = 64/(6.28 • 100k • 10Hz)

= 1µF. Lower gains settings will give a lower f3dB.

d. Calculate the value of R5 to set the LT6650 reference

equal to 1V;

V

REF

= 0.4(R5/R6 + 1), so R5 = R6(2.5V

REF

– 1). For

R6 = 20k, R5 = 30k

With V

REF

= 1V the maximum input difference voltage

is equal to 2V/64 = 31.2mV.

40nVpp Noise, 0.05μV/°C Drift, Chopped FET

Amplifi er

Figure 9’s circuit combines the ±5V rail-to-rail performance

of the LTC6241HV with a pair of extremely low noise JFETs

confi gured in a chopper based carrier modulation scheme

APPLICATIONS INFORMATION

6241 F08

R4

R3

R2

–

+

1/2

LTC6241

C1

C2

1µF

0.1µF

8 765

G2 G1 G0

1

1

2

234

AGNDOUT IN V

–

V

+

0.1µF

V

+

V

+

R1

R1 = R2 = R3 = R4

V2

V1

R5

1k

1000pF

3 4

5

R6

20k

LTC6910-2

LT6650

V

OUT

V

REF

–

+

1/2

LTC6241

C3

R7

100Ω

1µF

DIGITAL INPUTS

G1G2 GO

GAIN

0

0

1

1

0

0

1

1

0

0

0

0

1

1

1

1

0

1

0

1

0

1

0

1

0

–1

–2

–4

–8

–16

–32

–64

V

OUT

= (V1 – V2) GAIN + V

REF

V

R

R

RkV

REF

REF

=+

¥

§

¦

´

¶

µ

=

=

04

5

6

1

510 5 2 R620

.•

•• – k

d BANDWIDTH f f

f

RC

HIGH LOW

HIGH

––

•• •

3

1

23

=

=

P 1273

f

GAIN

RC

LOW

=

•• •P