7

FN6462.0

February 26, 2007

input oscillations due to the capacitive load seen by the

PWM input through the body diode of the controller’s PWM

output when the power-up and/or power-down sequence of

bias supplies of the driver and PWM controller are required.

Power-On Reset (POR) Function

During initial startup, the VCC voltage rise is monitored.

Once the rising VCC voltage exceeds 9.8V (typically),

operation of the driver is enabled and the PWM input signal

takes control of the gate drives. If VCC drops below the

falling threshold of 7.6V (typically), operation of the driver is

disabled.

Pre-POR Overvoltage Protection

Prior to VCC exceeding its POR level, the upper gate is held

low and the lower gate is controlled by the overvoltage

protection circuits during initial startup. The PHASE is

connected to the gate of the low side MOSFET (LGATE),

which provides some protection to the microprocessor if the

upper MOSFET(s) is shorted during initial startup. For

complete protection, the low side MOSFET should have a

gate threshold well below the maximum voltage rating of the

load/microprocessor.

When VCC drops below its POR level, both gates pull low

and the Pre-POR overvoltage protection circuits are not

activated until VCC resets.

Internal Bootstrap Device

Both drivers feature an internal bootstrap schottky diode.

Simply adding an external capacitor across the BOOT and

PHASE pins completes the bootstrap circuit. The bootstrap

function is also designed to prevent the bootstrap capacitor

from overcharging due to the large negative swing at the

trailing-edge of the PHASE node. This reduces voltage

stress on the boot to phase pins.

The bootstrap capacitor must have a maximum voltage

rating above UVCC + 5V and its capacitance value can be

chosen from the following equation:

where Q

G1

is the amount of gate charge per upper MOSFET

at V

GS1

gate-source voltage and N

Q1

is the number of

control MOSFETs. The ΔV

BOOT_CAP

term is defined as the

allowable droop in the rail of the upper gate drive.

As an example, suppose two IRLR7821 FETs are chosen as

the upper MOSFETs. The gate charge, Q

G

, from the data

sheet is 10nC at 4.5V (V

GS

) gate-source voltage. Then the

Q

GATE

is calculated to be 53nC for UVCC (i.e. PVCC in

PX3511B, VCC in PX3511A) = 12V. We will assume a

200mV droop in drive voltage over the PWM cycle. We find

that a bootstrap capacitance of at least 0.267μF is required.

Gate Drive Voltage Versatility

The PX3511A and PX3511B provide the user flexibility in

choosing the gate drive voltage for efficiency optimization.

The PX3511A upper gate drive is fixed to VCC [+12V], but

the lower drive rail can range from 12V down to 5V

depending on what voltage is applied to PVCC. The

PX3511B ties the upper and lower drive rails together.

Simply applying a voltage from 5V up to 12V on PVCC sets

both gate drive rail voltages simultaneously.

Power Dissipation

Package power dissipation is mainly a function of the

switching frequency (F

SW

), the output drive impedance, the

external gate resistance, and the selected MOSFET’s

internal gate resistance and total gate charge. Calculating

the power dissipation in the driver for a desired application is

critical to ensure safe operation. Exceeding the maximum

allowable power dissipation level will push the IC beyond the

maximum recommended operating junction temperature of

+125°C. The maximum allowable IC power dissipation for

the SO8 package is approximately 800mW at room

temperature, while the power dissipation capacity in the DFN

package with an exposed heat escape pad is more than

1.5W. The DFN package is more suitable for high frequency

applications. See Layout Considerations paragraph for

thermal transfer improvement suggestions. When designing

the driver into an application, it is recommended that the

following calculation is used to ensure safe operation at the

desired frequency for the selected MOSFETs. The total gate

drive power losses due to the gate charge of MOSFETs and

the driver’s internal circuitry and their corresponding average

C

BOOT_CAP

Q

GATE

ΔV

BOOT_CAP

--------------------------------------

≥

Q

GATE

Q

G1

UVCC•

V

GS1

------------------------------------

N

Q1

•=

(EQ. 1)

50nC

20nC

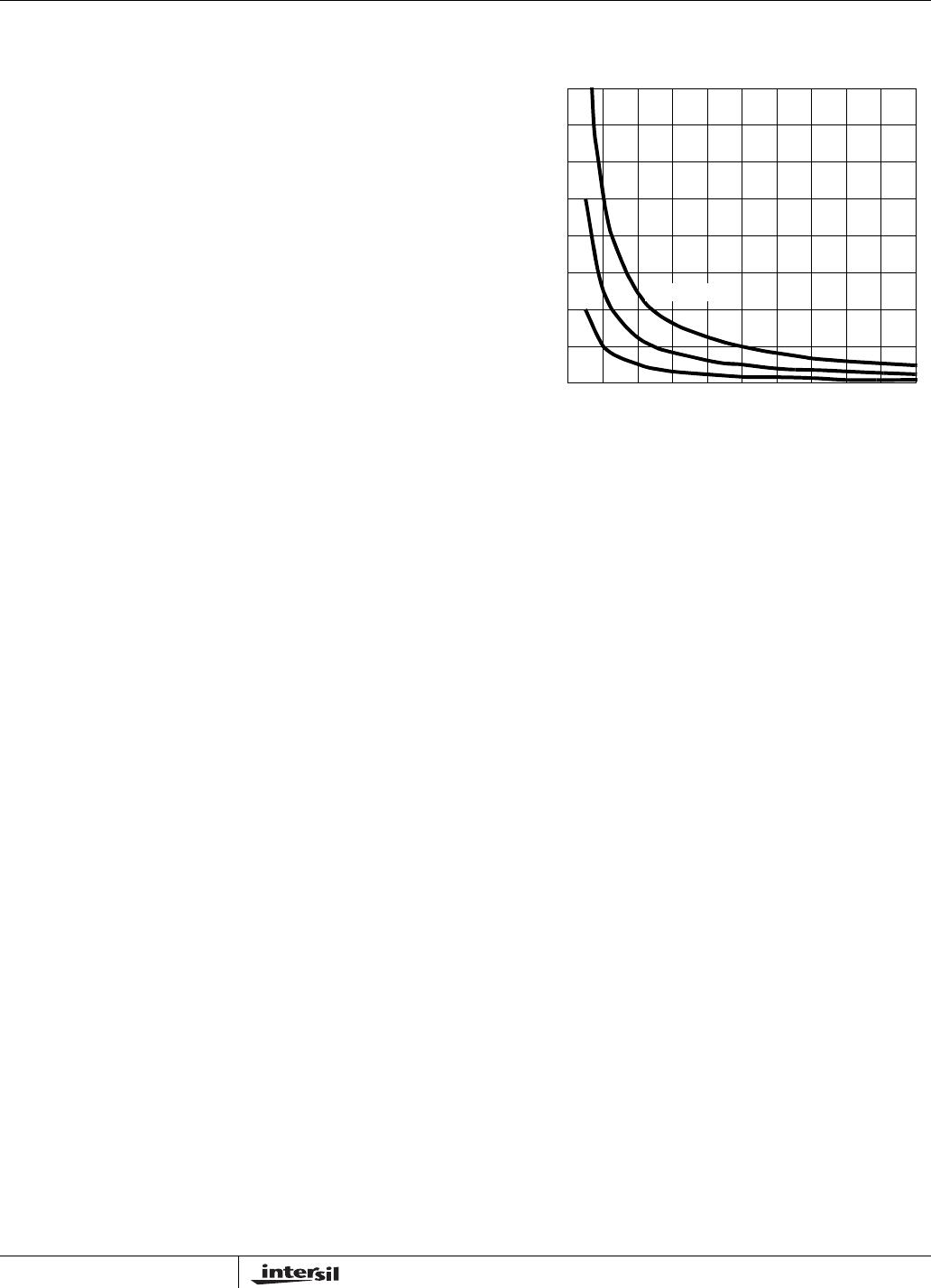

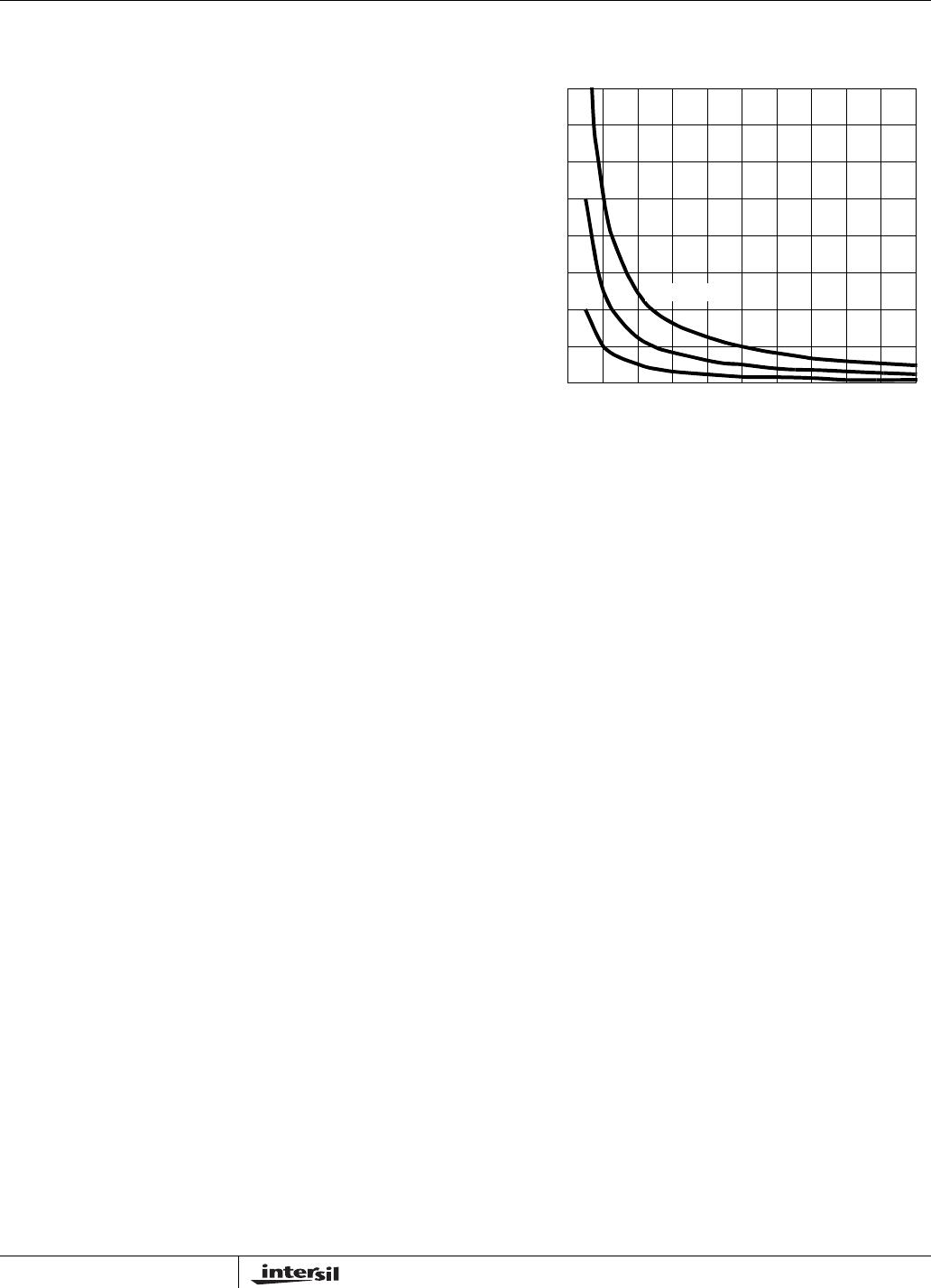

FIGURE 2. BOOTSTRAP CAPACITANCE vs BOOT RIPPLE

VOLTAGE

ΔV

BOOT_CAP

(V)

C

BOOT_CAP

(µF)

1.6

1.4

1.2

1.

0.8

0.6

0.4

0.2

0.0

0.30.0 0.1 0.2 0.4 0.5 0.6 0.90.7 0.8 1.0

Q

GATE

= 100nC

PX3511A, PX3511B