MAX1620/MAX1621

Digitally Adjustable LCD Bias Supplies

12 ______________________________________________________________________________________

The MAX1620 controls the DAC counter with the UP

and DN pins. A rising edge on UP increases V

OUT

by

decrementing the counter and decreasing the DAC

output voltage one step; a rising edge on DN de-

creases V

OUT

by incrementing the counter and

increasing the DAC output voltage one step. Holding

both UP and DN high resets the counter to half-scale.

The counter will not roll over at either the FS or ZERO

code. The control direction of UP and DN reverses for a

negative output, to maintain the same control direction

of the output voltage in absolute magnitude.

The MAX1621 controls the counter to the DAC through

the SMBus interface. The counter is treated as a 5-bit

register and resets on power-up. The setting in the DAC

is guaranteed to remain valid as long as V

DD

is greater

than the UVLO threshold (see Note 1 in the

Electrical

Characteristics

).

The MAX1620/MAX1621’s open-drain DMOSFET

(LCDON) can be used to disconnect the LCD panel

from the positive bias voltage with an external transistor.

The FET turns off (LCDON = float) if power-OK voltage

(POK) falls below 1V. In the MAX1621, LCDON can also

be controlled by the SMB command. LCDON cannot

switch negative output voltages.

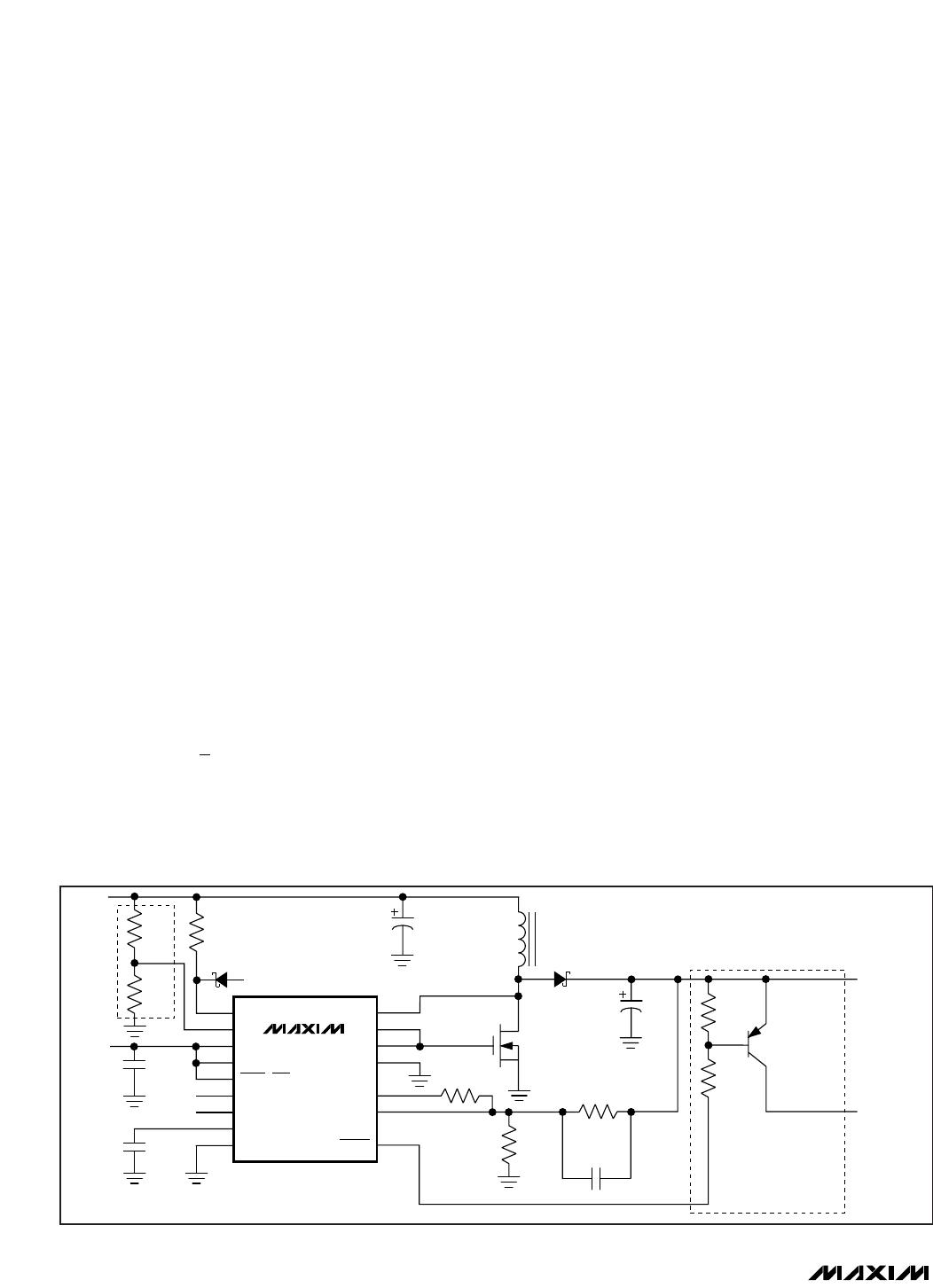

To prevent uncontrolled boosting when the output is

disconnected, the feedback resistors must sense the

boosted voltage rather than the output of the LCDON

switch (Figure 4).

Shutdown Mode

The MAX1620 shuts down when the SHDN pin is low.

The internal reference and biasing circuitry turn off,

and the supply current drops to 9µA. In shutdown,

DOUT = 0V and LCDON floats. UP/DN are ignored to

preserve the DAC state for the MAX1620. Tie unused

logic inputs to AGND for lowest operating current.

The MAX1621 can be shut down using the SMBus

interface (Table 2).

Reset Modes

If the MAX1620 is not in shutdown mode, the DAC can

be reset to mid-scale by holding UP and DN high. Mid-

scale is 16 steps from the minimum DAC output and 15

steps from the maximum.

The MAX1620/MAX1621 reset the DAC counter to mid-

scale at power-up or when V

DD

is below the undervolt-

age lockout threshold of 2.2V (typ).

MAX1621 Digital Interface

A single byte of data written over the Intel SMBus con-

trols the MAX1621. Figures 7 and 8 show example

single-byte writes. The MAX1621 contains two 2-bit reg-

isters for storing configuration data, and one register for

the 5-bit DAC data. Tables 1 and 2 describe the data

format for the configuration registers. The MAX1621

responds only to its own address (0101100 binary).

The REGSEL bit addresses the configuration registers.

REGSEL = 0 for the SUS register; REGSEL = 1 for the

OPR register. Each configuration register consists of a

SHDN bit and an LCDON bit. One of the two configura-

tion registers is always active. The state of the SUS pin

determines the active register. The OPR register is active

with SUS = high. The SUS register is active with SUS =

low.

Each byte written to the MAX1621 updates the DAC reg-

ister. DAC data is preserved in shutdown and when tog-

gling between configuration registers. Since there is only

one DAC register, SUS cannot be used to toggle

between two DAC codes.

Status information can be read from the MAX1621 using

the SMBus read-byte protocol. Figure 9 shows an exam-

ple status read and Table 3 describes the status-

information format.

During shutdown (SUS = 1 and OPR-SHDN = 0, or

SUS = 0 and SUS-SHDN = 0), the MAX1621 serial inter-

face remains fully functional and can be used to set

either the OPR-SHDN or SUS-SHDN bits to return the

MAX1621 to its normal operational state.

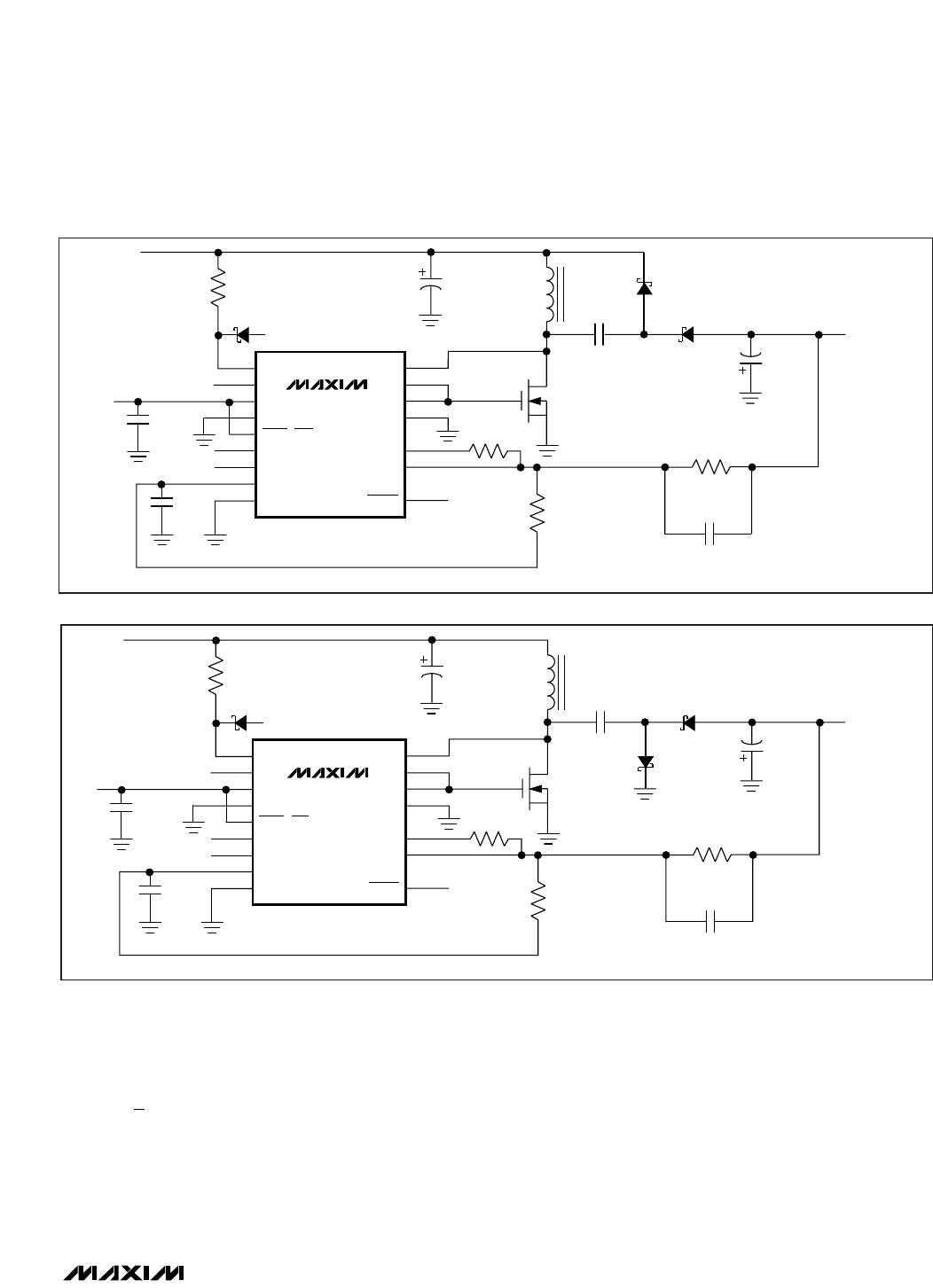

Separate/Same Power for L1 and V

DD

Separate voltage sources can supply the inductor (L1)

and the IC (V

DD

). This allows operation from low-voltage

batteries as well as high-voltage sources because chip

bias (150µA) is provided by a logic supply (3V to 5.5V)

while output power is sourced directly from the battery

to L1. Conversely, L1 and V

DD

can also be supplied

from one supply if it remains with V

DD

’s operating limits

(3V to 5.5V). If L1 and V

DD

are fed from the same volt-

age, D3 and R8 (Figures 4, 5, 6, and 10) can be omit-

ted, and BATT may be connected directly to V

DD

.