Technical information USBLC6-2

4/14 Doc ID 11265 Rev 5

2 Technical information

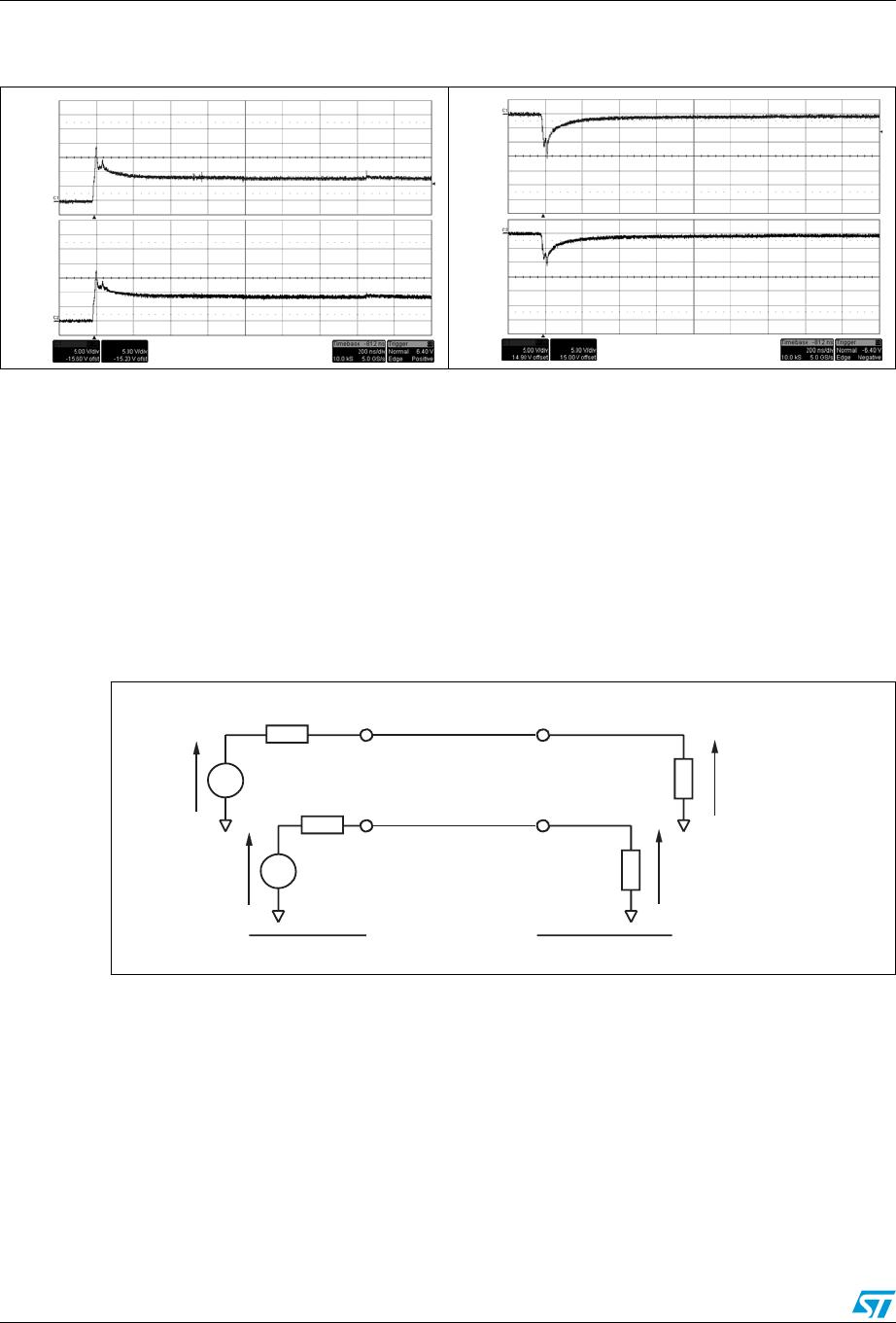

2.1 Surge protection

The USBLC6-2 is particularly optimized to perform surge protection based on the rail to rail

topology.

The clamping voltage V

CL

can be calculated as follow:

V

CL

+ = V

TRANSIL

+ V

F

for positive surges

V

CL

- = - V

F

for negative surges

with: V

F

= V

T

+ R

d

.I

p

(V

F

forward drop voltage) / (V

T

forward drop threshold voltage)

and V

TRANSIL

= V

BR

+ R

d_TRANSIL

.I

P

Calculation example

We assume that the value of the dynamic resistance of the clamping diode is typically:

R

d

= 0.5 Ω and V

T

= 1.1 V

We assume that the value of the dynamic resistance of the transil diode is typically:

R

d_TRANSIL

= 0.5 Ω and V

BR

= 6.1 V

For an IEC 61000-4-2 surge Level 4 (Contact Discharge: V

g

= 8 kV, R

g

= 330 Ω),

V

BUS

= +5 V, and if in first approximation, we assume that:

I

p

= V

g

/ R

g

= 24 A.

So, we find:

V

CL

+ = +31.2 V

V

CL

- = -13 V

Note: The calculations do not take into account phenomena due to parasitic inductances.

2.2 Surge protection application example

If we consider that the connections from the pin V

BUS

to V

CC

, from I/O to data line and from

GND to PCB GND plane are done by tracks of 10 mm long and 0.5 mm large, we assume

that the parasitic inductances L

VBUS

, L

I/O

and L

GND

of these tracks are about 6 nH. So when

an IEC 61000-4-2 surge occurs on data line, due to the rise time of this spike (t

r

=1ns), the

voltage V

CL

has an extra value equal to L

I/O

.dl/dt + L

GND

.dI/dt.

The dI/dt is calculated as:

dI/dt = I

p

/t

r

= 24 A/ns

The overvoltage due to the parasitic inductances is:

L

I/O

.dl/dt = L

GND

.dI/dt = 6 nH x 24 A/ns = 144 V

By taking into account the effect of these parasitic inductances due to unsuitable layout, the

clamping voltage will be:

V

CL

+ = +31.2 + 144 + 144 = 319.2 V

V

CL

- = -13.1 - 144 - 144 = -301.1 V