AD830

Rev. C | Page 16 of 20

stability and also keep bias current induced offsets low. Highest

CMRR and lowest dc offsets are preserved by including a

compensating resistor in series with Pin 3. The gain may be as

high as 100.

0.1µF

0.1µF

P

V

OUT

V

N

AD830

1

2

3

4

8

7

6

5

A = 1

C

G

M

G

M

INPUT

SIGNAL

CM

Z

CM

V

1

V

2

R

1

R

2

R

2

R

1

V

OUT

= (V

1

– V

2

)(1 + R

1

/R

2

)

00881-040

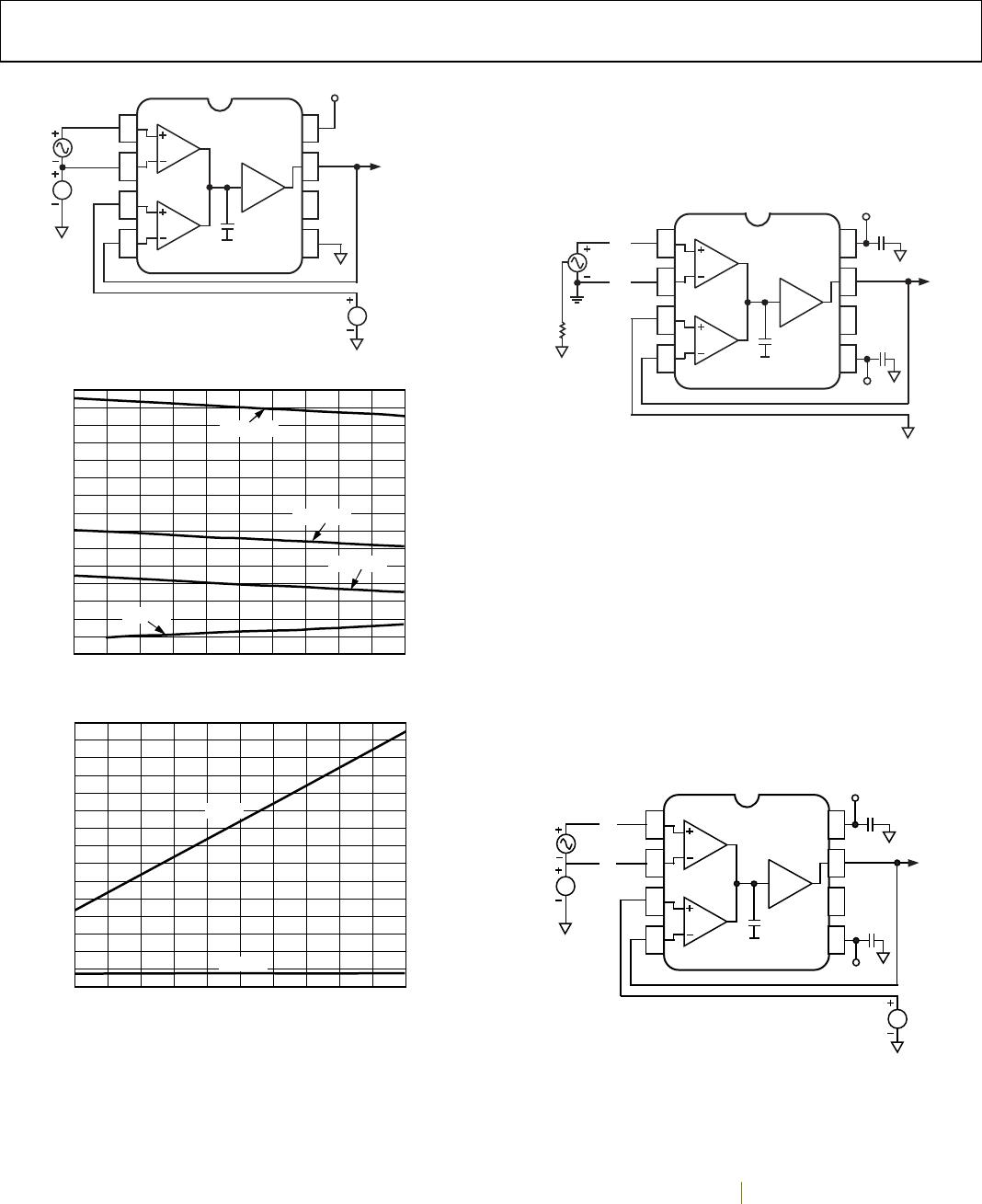

Figure 40. Gain of G Differential Amplifier, G>1

Offsetting the Output With Gain

Some applications, such as ADCs, require that the signal be

amplified and also offset, typically to accommodate the input

range of the device. The AD830 can offset the output signal

very simply through Pin 3 even with gain > 1. The voltage

applied to Pin 3 must be attenuated by an appropriate factor so

that V

3

× G = desired offset. In Figure 41, a resistive divider

from a voltage reference is used to produce the attenuated offset

voltage.

P

V

OUT

V

N

AD830

1

2

3

4

8

7

6

5

A = 1

G

M

G

M

C

0.1µF

0.1µF

INPUT

SIGNAL

V

CM

Z

CM

V

1

V

2

R

1

R

2

R

2

R

1

R

3

R

4

V

3

V

REF

V

OUT

= (V

1

– V

2

)(1 + R

1

/R

2

)

0881-041

Figure 41. Offsetting the Output with Differential Gain >1

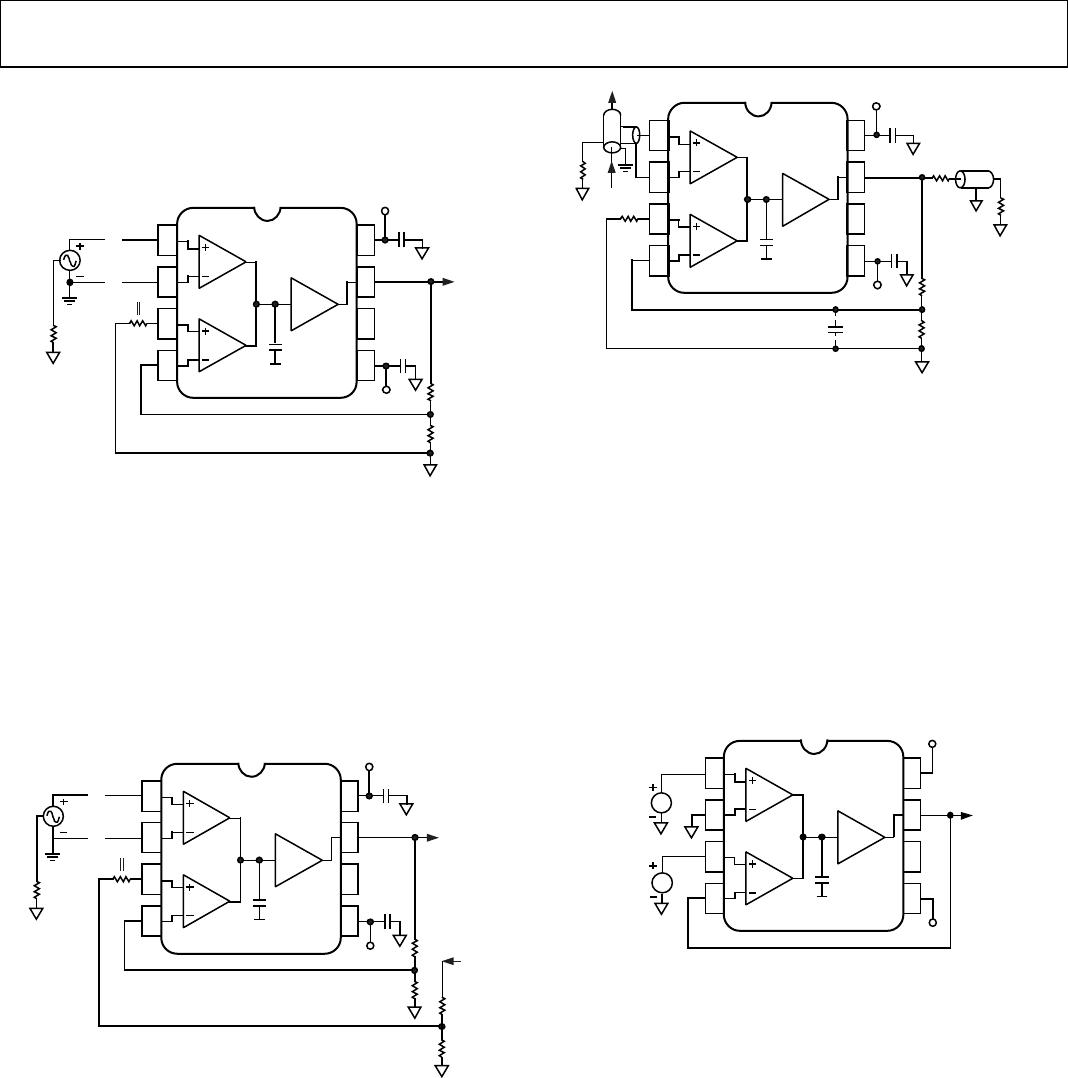

Loop Through or Line Bridging Amplifier (Figure 42)

The AD830 is ideally suited for use as a video line bridging

amplifier. The video signal is tapped from the conductor of the

cable relative to its shield. The high input impedance of the

AD830 provides negligible loading on the cable. More significantly,

the benign loading is maintained while the AD830 is powered

down. Coupled with its good video load driving performance,

the AD830 is well suited for video cable monitoring applications.

P

V

OUT

V

N

AD830

1

2

3

4

8

7

6

5

A = 1

G

M

C

G

M

R

G

249Ω

OPTIONAL C

C

499Ω

499Ω

75Ω

75Ω

0.1µF

0.1µF

0881-042

Figure 42. Cable Tap Amplifier

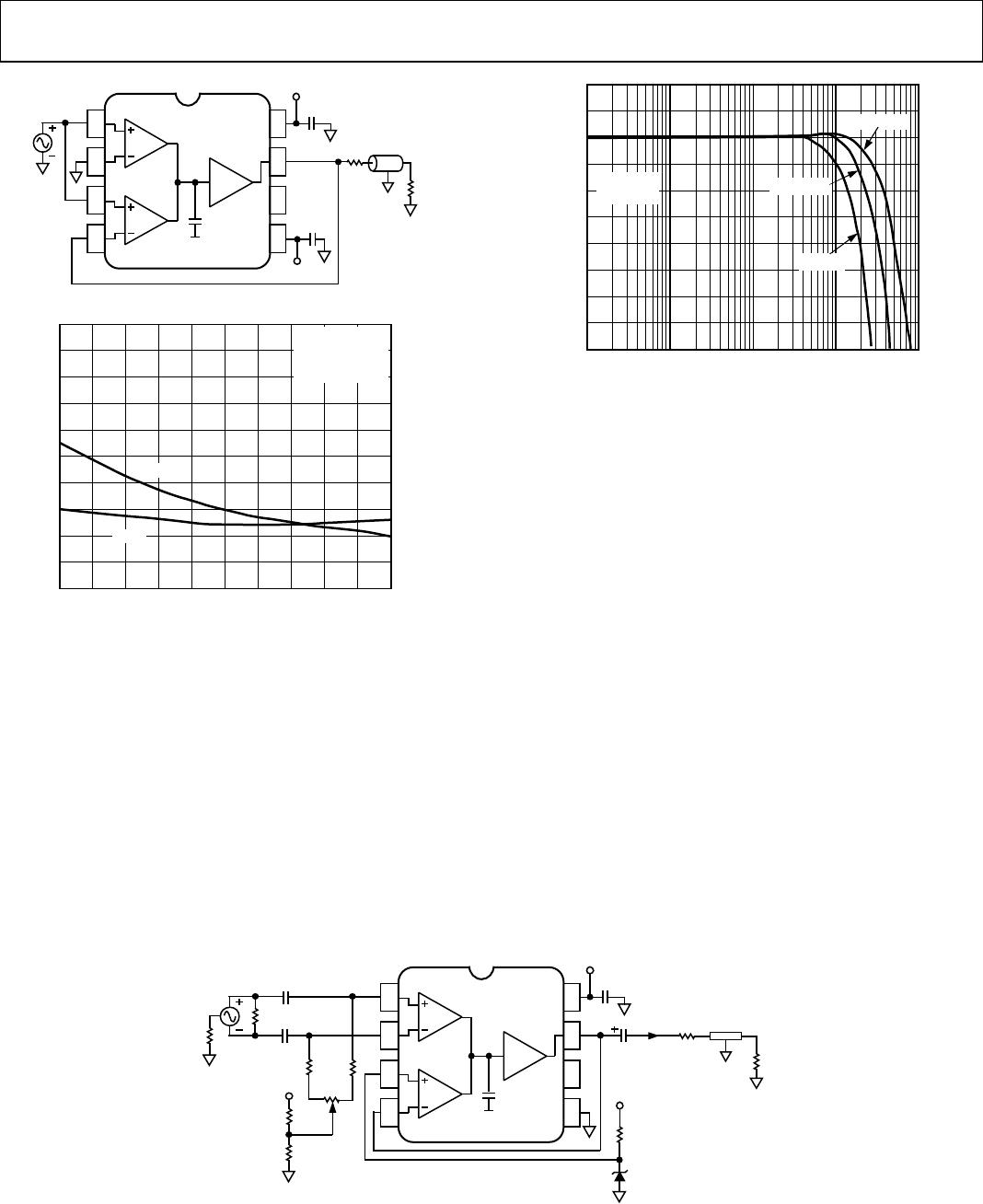

Resistorless Summing

Direct, two input, resistorless summing is easily realized from

the general unity gain mode. By grounding V

X2

and applying the

two inputs to V

X1

and V

Y1

, the output is the exact sum of the

applied voltages, V

1

and V

3

, relative to common; V

OUT

= V

1

+ V

3

.

A diagram of this simple but potent application is shown below

in Figure 43. The AD830 summing circuit possesses several

virtues not present in the classic op amp based summing circuits.

It has high impedance inputs, no resistors, very precise summing,

high reverse isolation, and noninverting gain. Achieving this

function and performance with op amps requires significantly

more components.

P

OUT

V

N

AD830

1

2

3

4

8

7

6

5

A = 1

G

M

C

G

M

V

1

V

3

V

OUT

= V

1

+V

3

0881-043

Figure 43. Resistorless Summing Amplifier

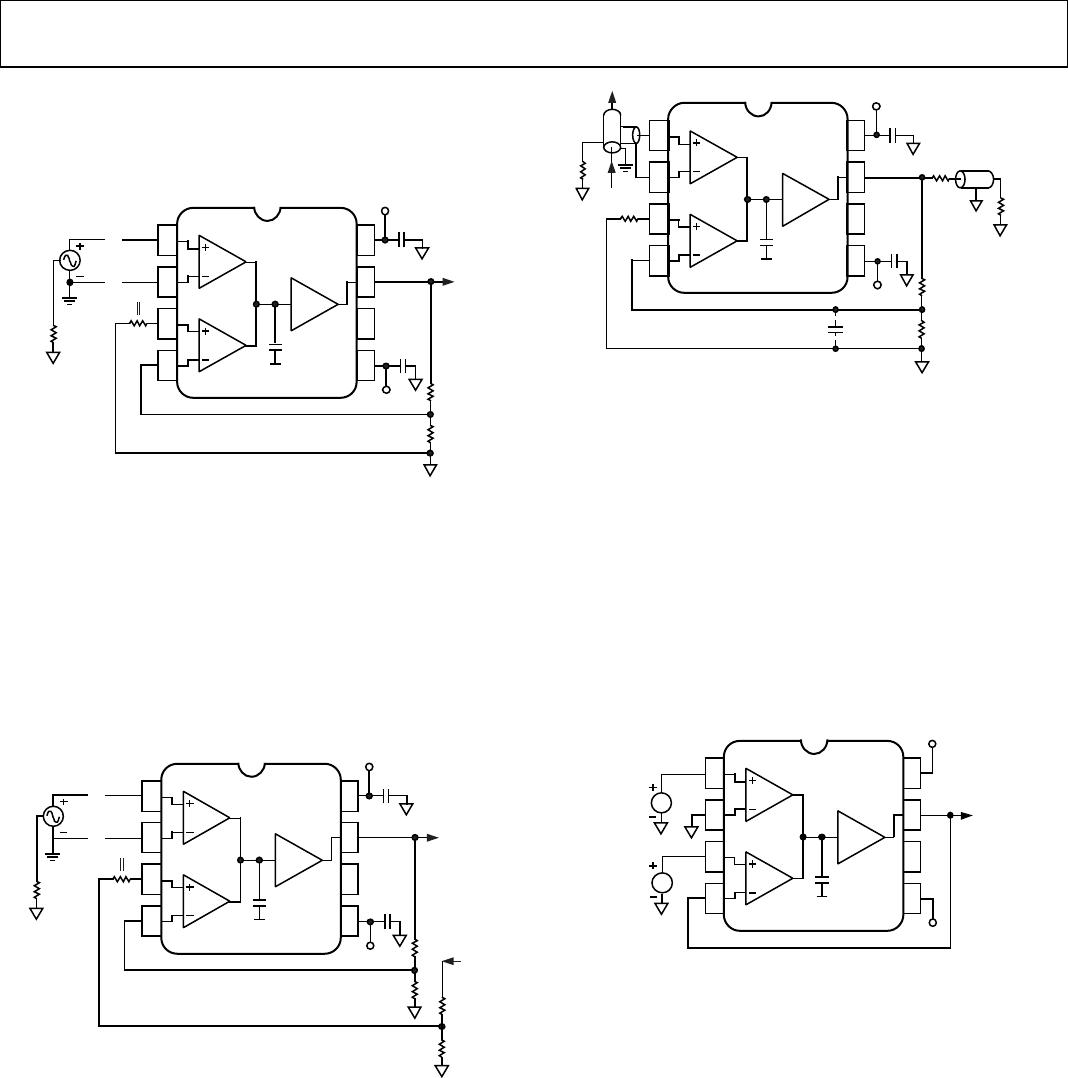

2× Gain Bandwidth Line Driver

A gain of two, without the use of resistors, is possible with the

AD830. This is accomplished by grounding V

X2

, tying the V

X1

and V

Y1

inputs together, and applying the input, V

IN

, to this

wired connection. The output is exactly twice the applied

voltage, V

IN

; V

OUT

= 2 × V

IN

. Figure 44 shows the connections

for this highly useful application. The most notable characteristic of

this alternative gain of +2 is that there is no loss of bandwidth as

in a voltage feedback op amp based gain of +2 where the

bandwidth is halved; therefore, the gain bandwidth is doubled.

In addition, this circuit is accurate without the need for any

precise valued resistors, as in the op amp equivalents, and it

possesses excellent differential gain and phase performance, as

shown in Figure 45 and Figure 46.