MAX1060/MAX1064

400ksps, +5V, 8-/4-Channel, 10-Bit ADCs

with +2.5V Reference and Parallel Interface

______________________________________________________________________________________ 11

Table 1. Control Byte Functional Description

NAME FUNCTION

D4

0

SGL/DIF

SGL/DIF = 0: Pseudo-differential analog input mode

SGL/DIF = 1: Single-ended analog input mode

In single-ended mode, input signals are referred to COM. In pseudo-differential mode, the voltage

difference between two channels is measured (Tables 2 and 3).

10

D3

UNI/BIP

Standby power-down mode. Clock mode is unaffected.

0

11

UNI/BIP = 0: Bipolar mode

UNI/BIP = 1: Unipolar mode

In unipolar mode, an analog input signal from 0 to V

REF

can be converted; in bipolar mode, the

signal can range from -V

REF

/2 to +V

REF

/2.

D2, D1, D0

Normal operation mode. External clock mode is selected.

1

A2, A1, A0

Address bits A2, A1, A0 select which of the 8/4 (MAX1060/MAX1064) channels are to be converted

(Tables 3 and 4).

Normal operation mode. Internal clock mode is selected.

BIT

PD1, PD0

0

D7, D6

PD1 and PD0 select the various clock and power-down modes.

Full power-down mode. Clock mode is unaffected.

D5 ACQMOD

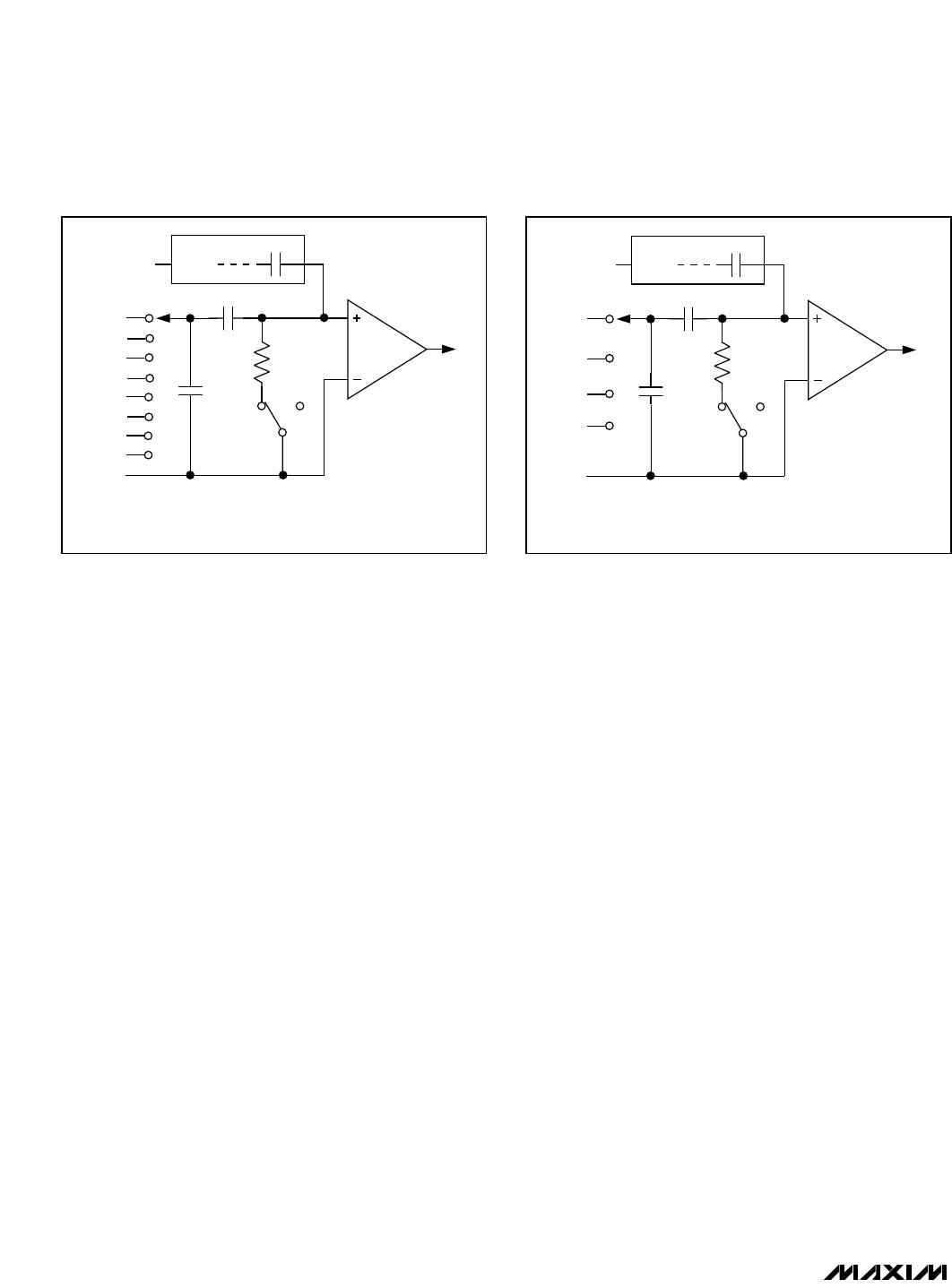

ACQMOD = 0: Internal acquisition mode

ACQMOD = 1: External acquisition mode

the acquisition interval. The ACQMOD (acquisition

mode) bit in the input control byte (Table 1) offers two

options for acquiring the signal: an internal and an

external acquisition. The conversion period lasts for 13

clock cycles in either the internal or external clock or

acquisition mode. Writing a new control byte during a

conversion cycle aborts the conversion and starts a

new acquisition interval.

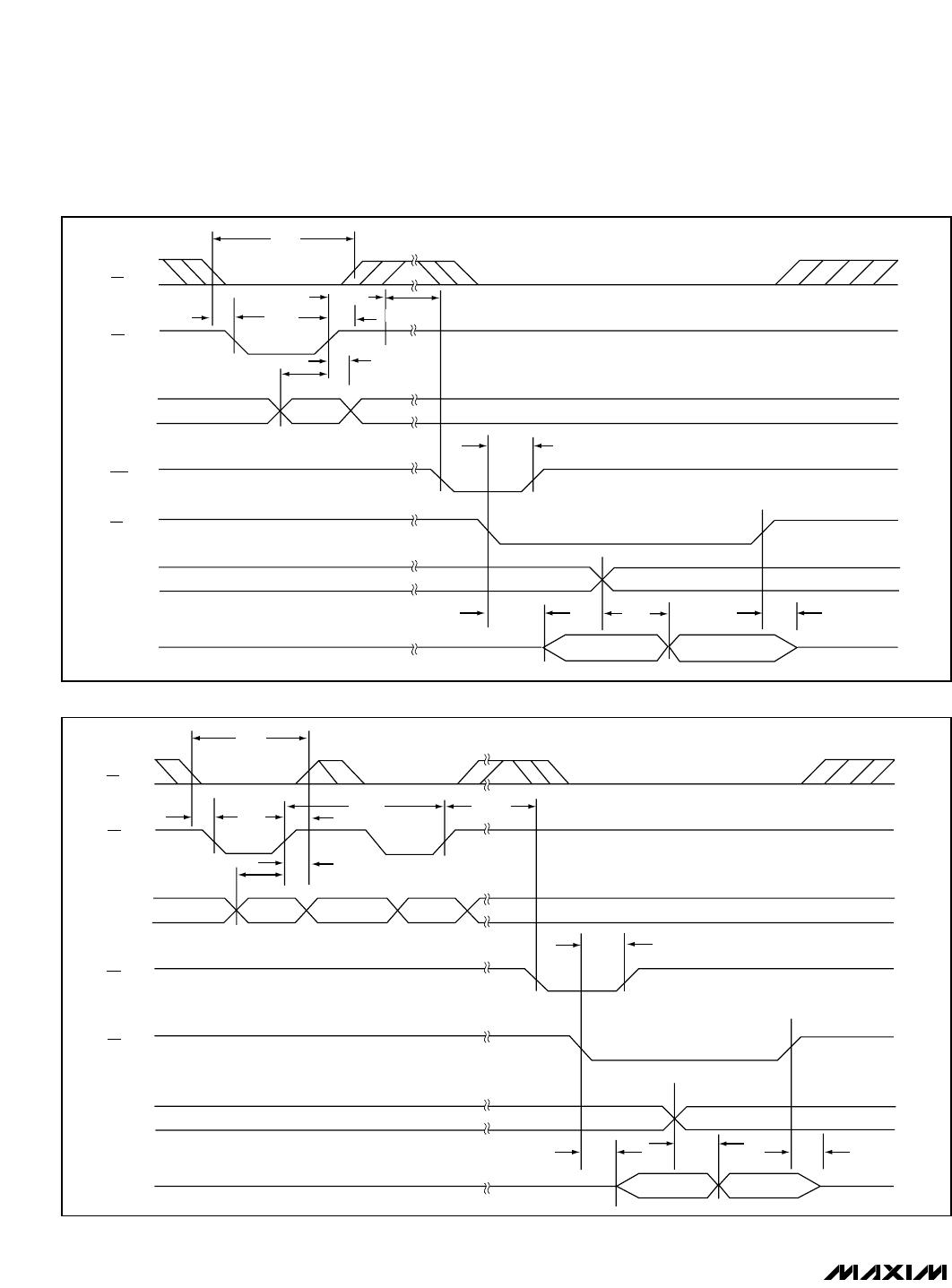

Internal Acquisition

Select internal acquisition by writing the control byte

with the ACQMOD bit cleared (ACQMOD = 0). This

causes the write pulse to initiate an acquisition interval

whose duration is internally timed. Conversion starts

when this acquisition interval (three external clock

cycles or approximately 1µs in internal clock mode)

ends (Figure 4). When the internal acquisition is com-

bined with the internal clock, the aperture jitter can be

as high as 200ps. Internal clock users wishing to

achieve the 50ps jitter specification should always use

external acquisition mode.

External Acquisition

Use external acquisition mode for precise control of the

sampling aperture and/or dependent control of acquisi-

tion and conversion times. The user controls acquisition

and start-of-conversion with two separate write pulses.

The first pulse, written with ACQMOD = 1, starts an

acquisition interval of indeterminate length. The second

write pulse, written with ACQMOD = 0 (all other bits in

the control byte are unchanged), terminates acquisition

and starts conversion on WR rising edge (Figure 5).

The address bits for the input multiplexer must have the

same values on the first and second write pulses.

Power-down mode bits (PD0, PD1) can assume new

values on the second write pulse (see the Power-Down

Modes section). Changing other bits in the control byte

corrupts the conversion.

Reading a Conversion

A standard interrupt signal, INT, is provided to allow the

MAX1060/MAX1064 to flag the µP when the conversion

has ended and a valid result is available. INT goes low

when the conversion is complete and the output data is

ready (Figures 4 and 5). INT returns high on the first

read cycle or if a new control byte is written.

Selecting Clock Mode

The MAX1060/MAX1064 operate with an internal or

external clock. Control bits D6 and D7 select either

internal or external clock mode. The part retains the

last-requested clock mode if a power-down mode is

selected in the current input word. For both internal and

external clock modes, internal or external acquisition

can be used. At power-up, the MAX1060/MAX1064

enter the default external clock mode.