WM8781 Production Data

w

PD, January 2012, Rev 4.5

10

DEVICE DESCRIPTION

INTRODUCTION

The WM8781 is a stereo 24-bit ADC designed for demanding recording applications such as DVD

recorders, studio mixers, PVRs, and AV amplifiers. The WM8781 consists of stereo line level inputs,

followed by a sigma-delta modulator and digital filtering.

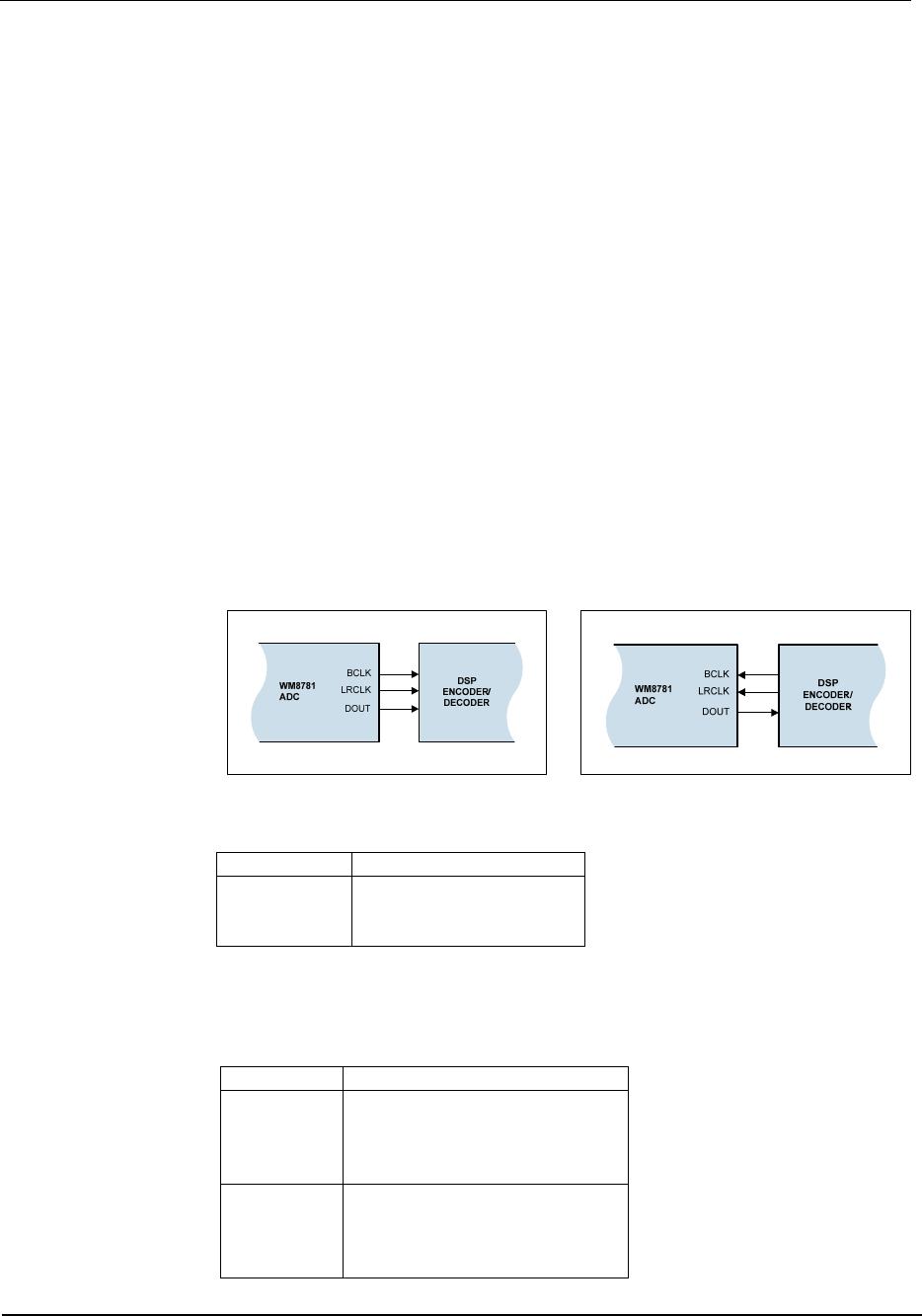

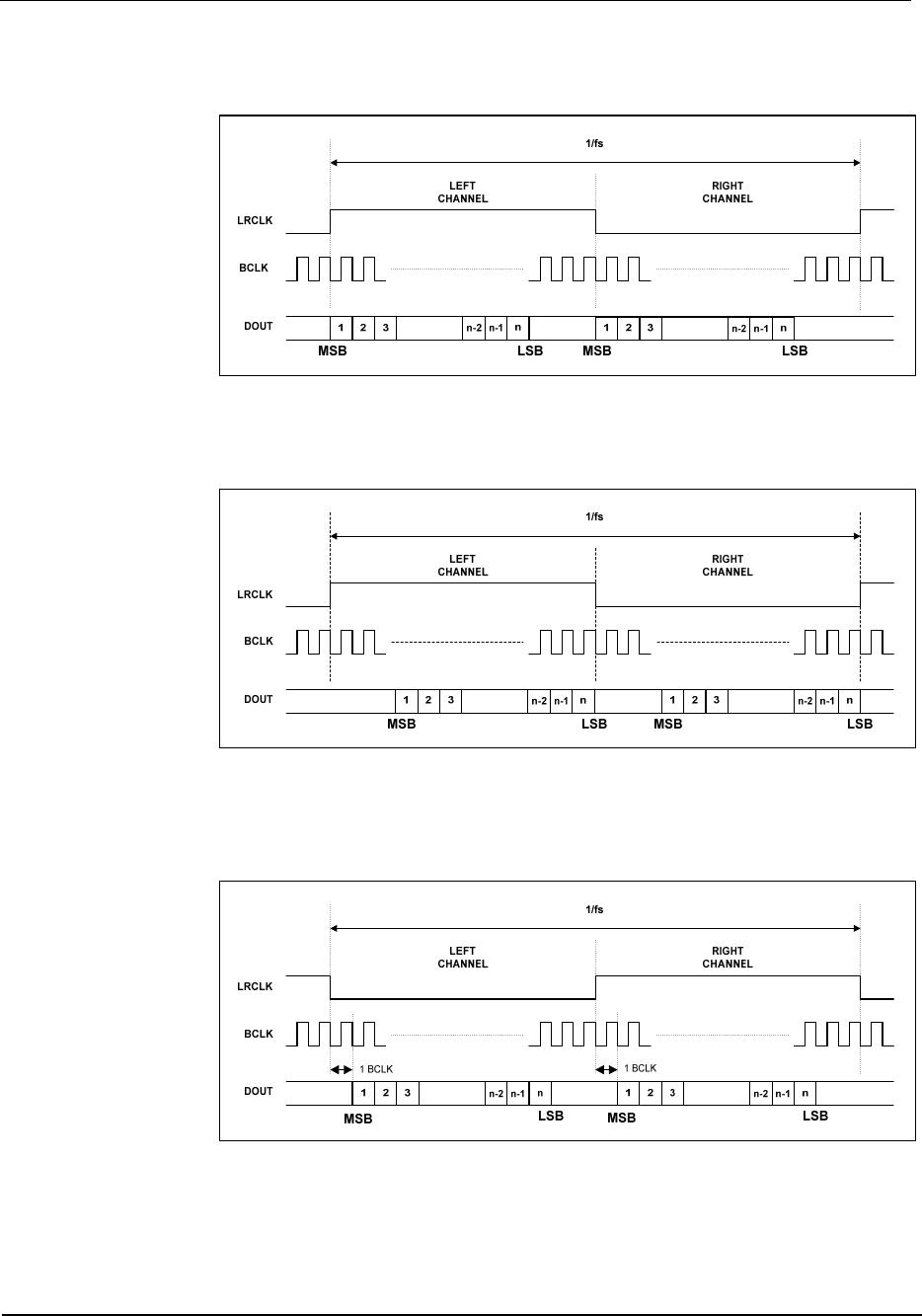

The device offers stereo line level inputs along with two control input pins (FORMAT, IWL) to allow

operation of the audio interface in three industry standard modes (left justified, right justified or I

2

S) .

An internal op-amp is integrated on the front end of the chip to accommodate analogue input signals

greater than 1V

rms

. The device also has a high pass filter to remove residual DC offsets.

The WM8781 offers Master or Slave mode clocking schemes. A control input pin M/S is used to allow

Slave mode or Master mode operation. The WM8781 supports master clock rates from 128fs to 768fs

and digital audio output word lengths from 16-24 bits. Sampling rates from 8kHz to 192kHz are

supported, delivering high SNR operating with 128x, 64x or 32x over-sampling, according to the

sample rate.

The line inputs are biased internally through the operational amplifier to V

MID

.

ADC

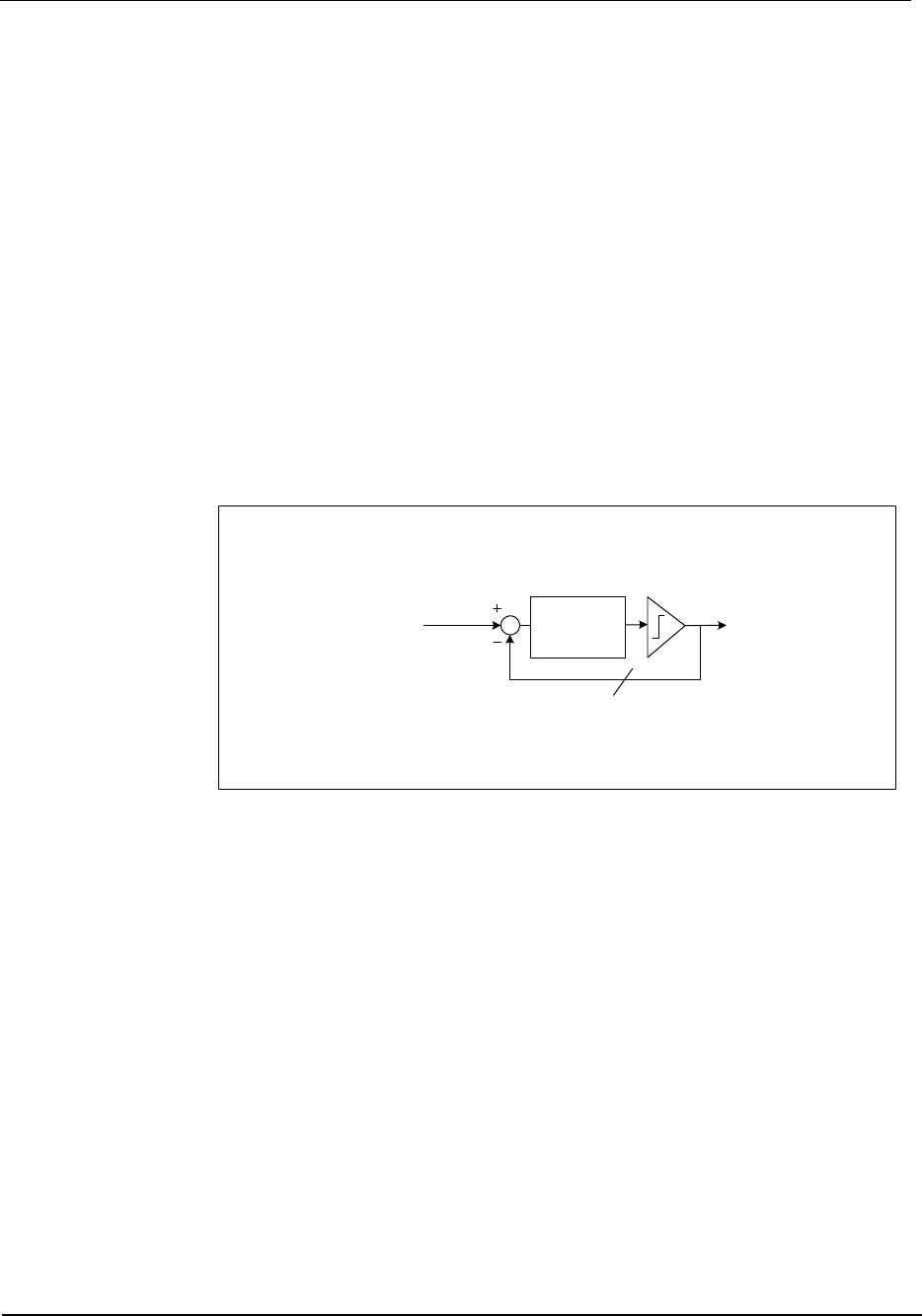

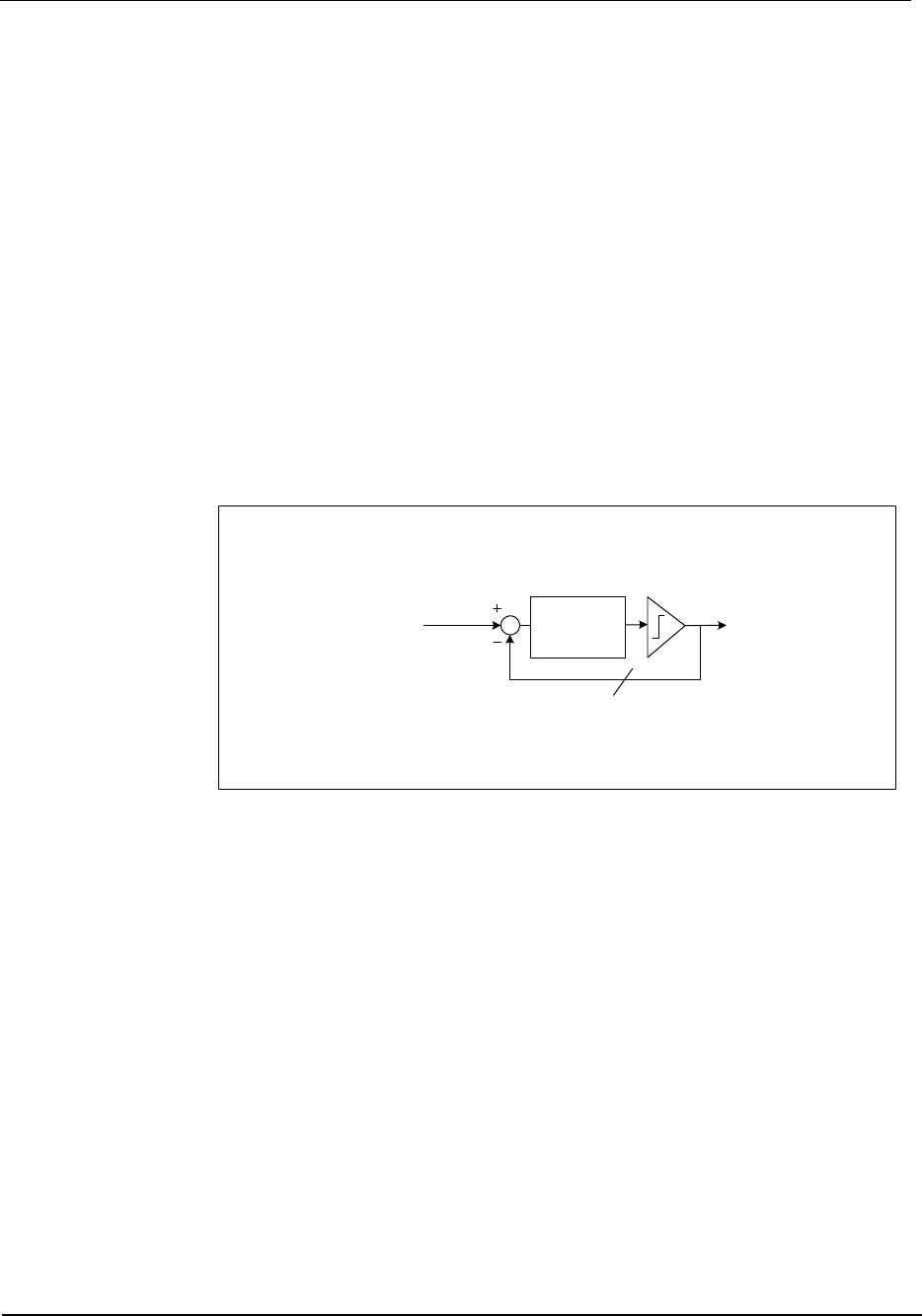

The WM8781 uses a multi-bit over sampled sigma-delta ADC. A single channel of the ADC is

illustrated in Figure 4 Multi-Bit Oversampling Sigma Delta ADC Schematic.

LIN/RIN

ANALOG

INTEGRATOR

MULTI

BITS

TO ADC DIGITAL FILTERS

Figure 4 Multi-Bit Oversampling Sigma Delta ADC Schematic

The use of multi-bit feedback and high oversampling rates reduces the effects of jitter and high

frequency noise.

The ADC Full Scale input is 1.0V rms at AVDD = 5.0 volts. Any input voltage greater than full scale

will possibly overload the ADC and cause distortion. Note that the full scale input has a linear

relationship with AVDD. The internal op-amp and appropriate resistors can be used to reduce signals

greater than 1Vrms before they reach the ADC.

The ADC filters perform true 24 bit signal processing to convert the raw multi-bit oversampled data

from the ADC to the correct sampling frequency to be output on the digital audio interface.

ADC DIGITAL FILTER

The ADC digital filters contain a digital high pass filter. The high-pass filter response detailed in Digital

Filter Characteristics. The operation of the high pass filter removes residual DC offsets that are

present on the audio signal.