Production Data WM8781

w

PD, January 2012, Rev 4.5

13

MASTER CLOCK AND AUDIO SAMPLE RATES

In a typical digital audio system there is only one central clock source producing a reference clock to

which all audio data processing is synchronised. This clock is often referred to as the audio system’s

Master Clock (MCLK). The external master system clock can be applied directly through the MCLK

input pin. In a system where there are a number of possible sources for the reference clock it is

recommended that the clock source with the lowest jitter be used to optimise the performance of the

ADC.

The master clock is used to operate the digital filters and the noise shaping circuits. The WM8781

supports master clocks of 128fs, 192fs, 256fs, 384fs, 512fs and 768fs, where fs is the audio sampling

frequency (LRCLK). In Slave Mode, the WM8781 automatically detects the audio sample rate. In

Master Mode, LRCLK is generated for rate 384fs, unless the user changes this to 192fs using the

FSAMPEN pin = z (see Table 7 below). BCLK is also generated in Master Mode, where BCLK=64fs.

Table 6 shows the common MCLK frequencies for different sample rates.

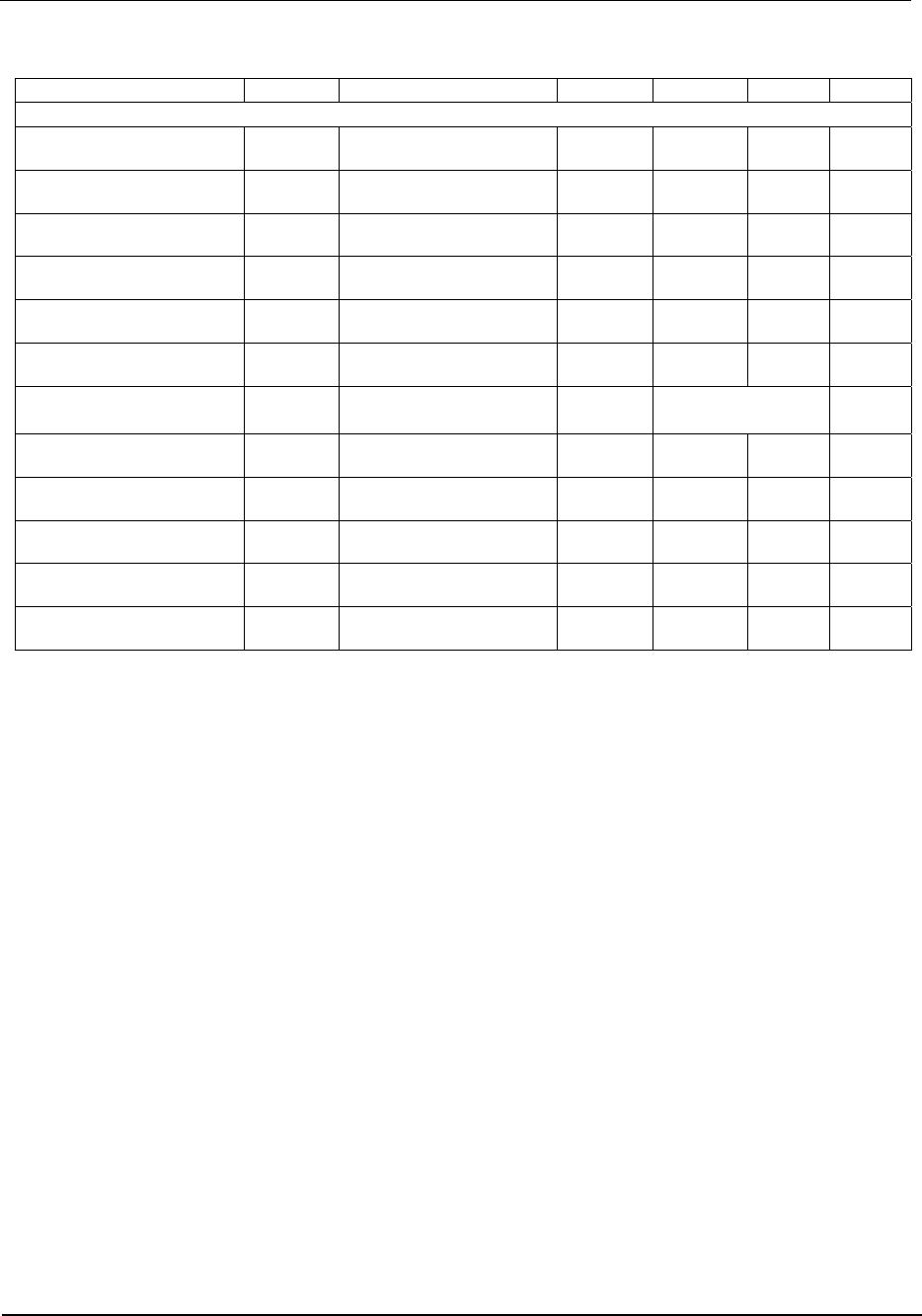

SAMPLING RATE

(LRCLK)

Master Clock Frequency (MHz)

128fs 192fs 256fs 384fs 512fs 768fs

8kHz 1.024 1.536 2.048 3.072 4.096 6.144

16kHz 2.048 3.072 4.096 6.144 8.192 12.288

32kHz 4.096 6.144 8.192 12.288 16.384 24.576

44.1kHz 5.6448 8.467 11.2896 16.9340 22.5792 33.8688

48kHz 6.144 9.216 12.288 18.432 24.576 36.864

96kHz 12.288 18.432 24.576 36.864 - -

192kHz 24.576 36.864 - - - -

Table 6 Master Clock Frequency Selection

In Slave mode, the WM8781 has a master detection circuit that automatically determines the

relationship between the master clock frequency and the sampling rate (to within +/- 32 system

clocks). If there is a greater than 32 clocks error the interface sets itself to the highest rate available

(768fs). There must be a fixed number of MCLKS per LRCLK, although the WM8781 is tolerant of

phase variations or jitter on these clocks.

The WM8781 can operate at sample rates from 8kHz to 192kHz. The WM8781 uses a sigma-delta

modulator that operates at a fixed frequency of 6.144MHz (128 x LRCLK oversampling @ 48kHz

sampling rate). For correct operation of the device and optimal performance, the user must set the

appropriate ADC modulator sampling rate enable. In both Master and Slave Modes, it is

recommended that for 96kHz the user sets FSAMPEN to 1, and for 192kHz set FSAMPEN to z. For

Master Mode 192kHz, FSAMPEN set to z is a requirement.

PIN DESCRIPTION

M/S Master/Slave Selection

0 = Slave Mode (128fs, 192fs,

256fs, 384fs, 512fs, 768fs)

1= Master Mode (384fs, 192fs

when FSAMPEN=z)

FSAMPEN Fast sampling rate enable

0 = 48kHz enable (128x OSR)

1 = 96kHz enable (64x OSR)

z = 192kHz enable (32x OSR)

Table 7 Master/Slave and Sampling Rate Enable Selection