TFF11092HN All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

Product data sheet Rev. 1 — 28 March 2013 6 of 17

NXP Semiconductors

TFF11092HN

Low phase noise LO generator for VSAT applications

10.2 Output buffer

The output consists of a differential pair with 50 collector resistors R

BUF_P

and R

BUF_N

. If

only one output is used, terminate the non used output with the same impedance as the

load (see Figure 8

)

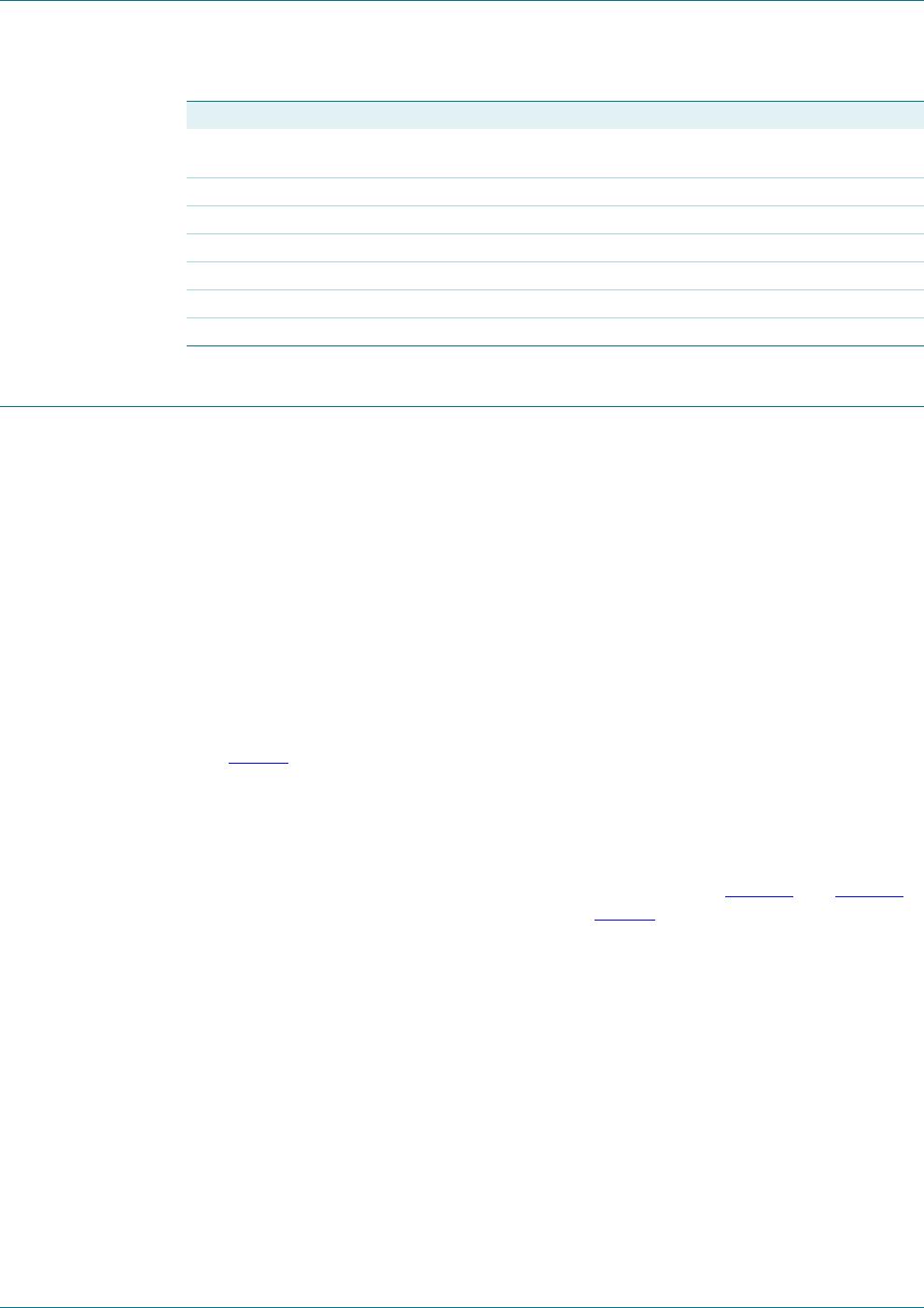

10.3 Lock detector

The lock detector is the output of a window detector. The window detector compares the

output voltage over the charge pump. This voltage is identical to VTUNE when a

type 2 loop filter is used (see Figure 4

). In case of a type 3 loop filter this voltage is filtered

by R2/C3 (see Figure 5

). Due to this filtering the attack and decay time will decrease.

The lower window detector threshold voltage is 7 % of the output voltage on

VREGVCO (pin 1), the upper window detector threshold voltage is 93 % of the output

voltage on VREGVCO (pin 1). The hysteresis is 0.1 V. The output is 2.5 V CMOS

compliant. The values are shown in Table 6

. The timing diagram is shown in Figure 6.

At start-up the LCKDET (pin 7) will be LOW until the circuit has acquired lock.

Fig 4. Type 2 loop filter Fig 5. Type 3 loop filter

001aal727

10 pF

C2

C1

R1

30 pF

3

VTUNE

2

CPOUT

1

VREGVCO

2.7 V

001aal728

10 pF

C2

C3

R2

C1

R1

30 pF

3

VTUNE

2

CPOUT

1

VREGVCO

2.7 V

Table 5. Component values used for characterization

f

i(ref)

Divider value C1 C2 C3 R1 R2

(MHz) (nF) (pF) (pF) () ()

35.273 to 36.016 256 27 82 33 470 560

70.547 to 72.031 128 18 82 33 330 560

141.094 to 144.063 64 18 120 33 270 560

282.188 to 288.125 32 33 270 33 120 560

564.375 to 576.250 16 68 560 33 68 560