TFF11092HN All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

Product data sheet Rev. 1 — 28 March 2013 8 of 17

NXP Semiconductors

TFF11092HN

Low phase noise LO generator for VSAT applications

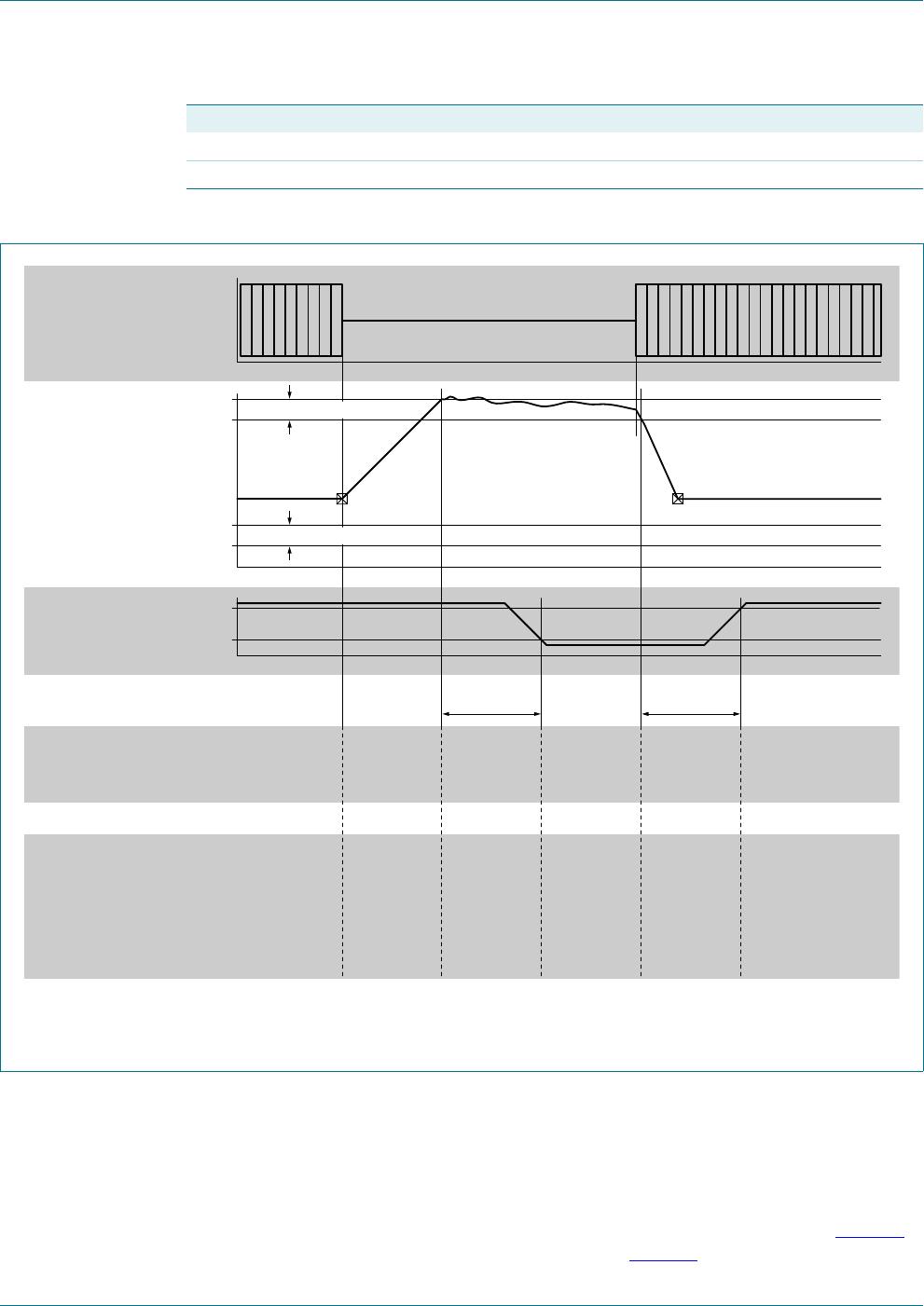

Note that the phase noise of the output signal is also determined by the phase noise of the

reference signal. The reference frequency range is equal to the

output frequency / division value. Note that the output frequency is guaranteed from

8.20 GHz to 8.60 GHz.

10.5 Divider settings (NSL2, NSL1, NSL0)

The divider can be set to 16, 32, 64, 128 and 256 (See Table 8). The logic levels for

NSL0 (pin 4), NSL1 (pin 5) and NSL2 (pin 6) are given in Table 7

.

The pins have a pull-up resistor of 100 k to V

CC(DIV)

(pin 13).

The device is only guaranteed when NSL2, NSL1 and NSL0 are predefined at start-up (no

change of divider value is allowed during operation).

The truth table is shown in Table 8.

[1] Test mode, divider output will be disabled.

11. Limiting values

Table 7. Logical and physical value for divider setting (NSL2, NSL1, NSL0)

Logical value Physical value

0GND

1 open or V

CC

Table 8. Divider setting as function of NSL2, NSL1 and NSL0

Setting number NSL2 NSL1 NSL0 Divider value

000016

100132

201064

3011128

4100256

5101

[1]

6110

[1]

7111

[1]

Table 9. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter Conditions Min Max Unit

V

I

input voltage on pin NSL0 0.5 +5 V

on pin NSL1 0.5 +5 V

on pin NSL2 0.5 +5 V

on pin IN(REF)_P 0.5 +5 V

on pin IN(REF)_N 0.5 +5 V

on pin V

CC(REF)

0.5 +5 V

on pin V

CC(DIV)

0.5 +5 V

on pin V

CC(BUF)

0.5 +5 V