NJM2211

-

-

Ver.2003-12-09

● Reference Voltage V

R

(Pin 10)

This pin is internally biased at the reference voltage level, V

R

; V

R

=V+ / 2-650mV. The DC voltage level at this pin forms

an internal reference for the voltage levels at pin 3, 8, 11, and 12. Pin 10 must be bypassed to ground with a 0.1µF

capacitor.

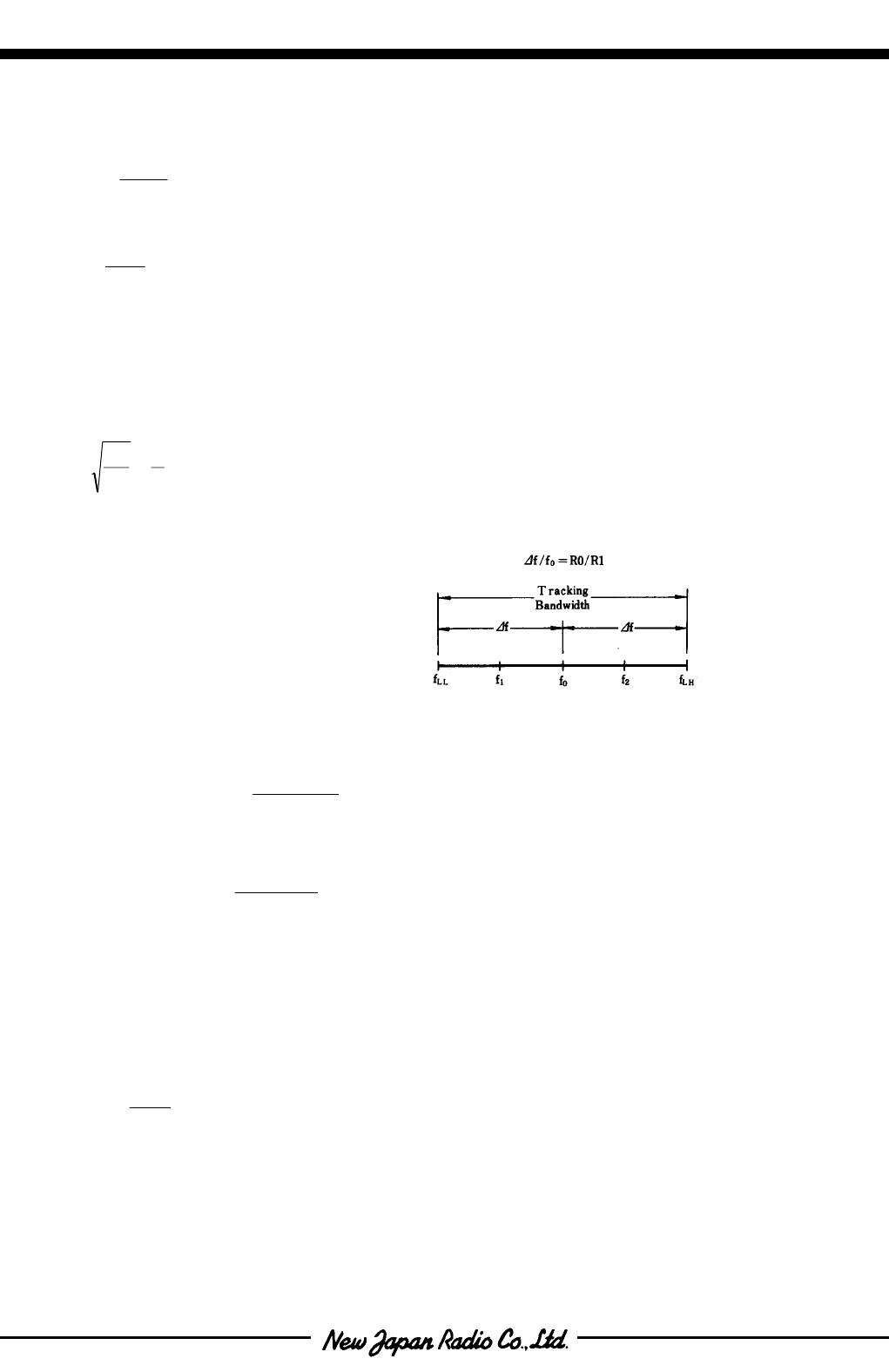

● Loop Phase Detector Output (Pin 11)

This terminal provides a high impedance output for the loop phase-detector. The PLL loop filter is formed by R1 and C1

connected to pin 11 (see Figure 1). With no input signal, or with no phase error within the PLL, the DC level at pin 11 is

very nearly equal to V

REF

. The peak voltage swing available at the phase detector output is equal to ±V

REF

.

Figure 1. FSK & Tone Detection

● VCO Control Input (Pin 12)

VCO free-running frequency is determined by external timing resistor, R0, connected from this terminal to ground. The

VCO free-running frequency, f

0

, is given by :

()

0C0R

1

Hzf

0

=

where C0 is the timing capacitor across pins 13 and 14. For optimum temperature stability R0 must be in the range of

10kΩ to 100kΩ (see Typical Electrical Characteristics).

This terminal is a low impedance point, and is internally biased at a DC level equal to V

R

. The maximum timing current

drawn from pin 12 must be limited to ≤ 3mA for proper operation of the circuit.

● VCO Timing Capacitor (Pins 13 and 14)

VCO frequency is inversely proportional to the external timing capacitor, C0, connected across these terminals. C0 must

be non-polarized, and in the range of 200pF to 10µF.

● VCO Frequency Adjustment

VCO can be fine tuned by connecting a potentiometer, R

X

, in series with R0 at pin 12 (see Figure 2)

● VCO Free-Running Frequency, F

0

The NJM2211 does not have a separate VCO output terminal. Instead, the VCO outputs are internally connected to the

phase-detector sections of the circuit. However, for setup or adjustment purposes, the VCO free-running frequency can

be measured at pin 3 (with C

D

disconnected) with no input and also pin 2 shorted to pin 10.