FEDR44V064B-02

Issue Date: Sep. 07, 2017

MR44V064B

64k Bit(8,192-Word × 8-Bit) FeRAM (Ferroelectric Random Access Memory) I2C

1/16

GENERAL DESCRIPTION

The MR44V064B is a nonvolatile 8,192-word x 8-bit ferroelectric random access memory (FeRAM) developed

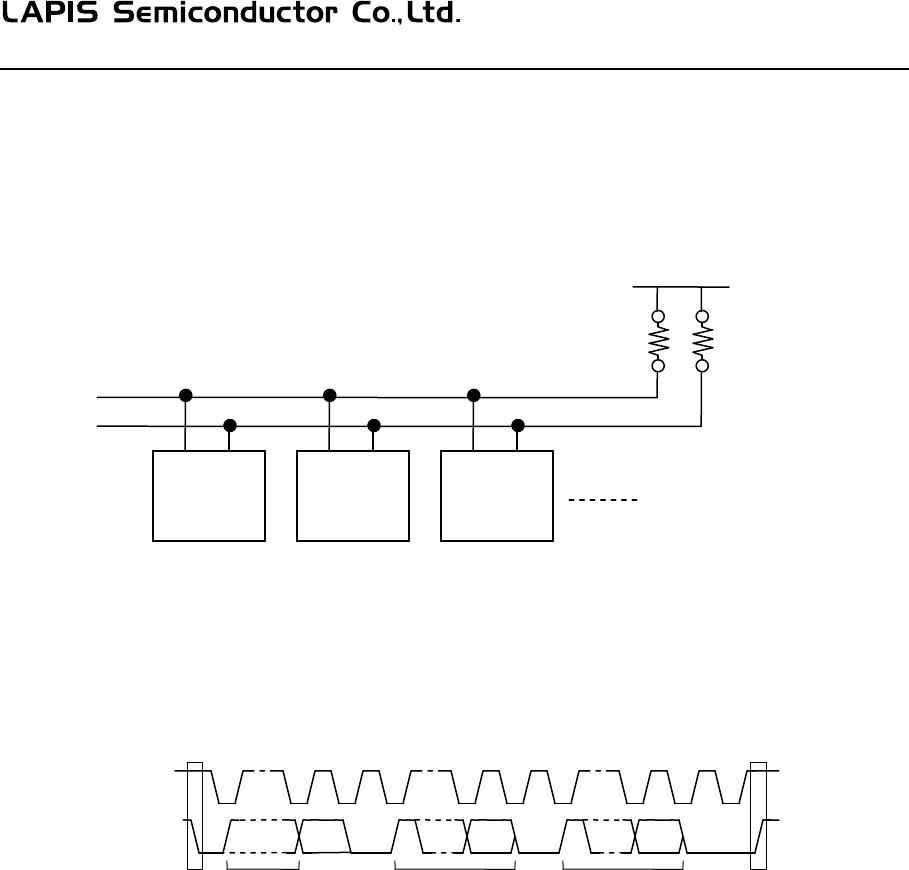

in the ferroelectric process and silicon-gate CMOS technology. The MR44V064B is accessed using Two-wire

Serial Interface ( I2C BUS ).Unlike SRAMs, this device, whose cells are nonvolatile, eliminates battery backup

required to hold data. This device has no mechanisms of erasing and programming memory cells and blocks,

such as those used for various EEPROMs. Therefore, the write cycle time can be equal to the read cycle time and

the power consumption during a write can be reduced significantly.

The MR44V064B can be used in various applications, because the device is guaranteed for the write/read

tolerance of 10

12

cycles per bit and the rewrite count can be extended significantly.

FEATURES

• 8,192-word × 8-bit configuration I2C BUS Interface

• A single 3.3 V typ (1.8V to 3.6V) power supply

• Operating frequency: 3.4MHz(Max) HS-mode

1MHz(Max) F/S-mode Plus

• Read/write tolerance 10

12

cycles/bit

• Data retention 10 years

• Guaranteed operating temperature range −40 to 85°C

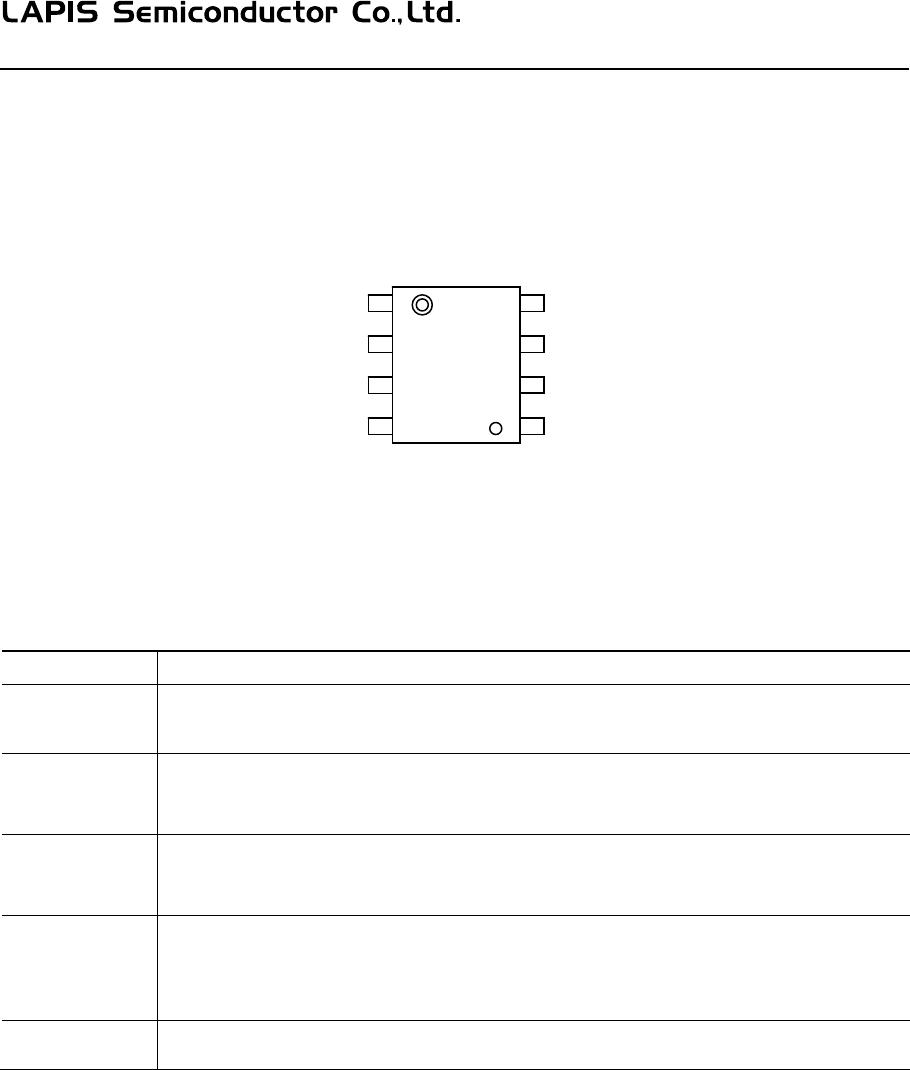

• Package options:

8-pin plastic SOP (P-SOP8-200-1.27-T2K)

• RoHS (Restriction of hazardous substances) compliant